#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# High-Speed Optical Wireless Communications using Reduced-State Sequence Detection

by

Bahram Zand

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy

Graduate Department of Electrical and Computer Engineering

University of Toronto

© Copyright by Bahram Zand 2002

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-69143-8

# High-Speed Optical Wireless Communications using Reduced-State Sequence Detection

Bahram Zand

Department of Electrical and Computer Engineering

University of Toronto

Degree of Doctor of Philosophy, 2002

#### **Abstract**

Driven by the need for high-speed connectivity in short distances and the costs and difficulties of deploying cables, this thesis discusses the design of short-distance optical wireless data communications with the target speed of IGb/s. In addition to exploring the effect of individual components in this link, two blocks at the receiver side, the front-end transimpedance amplifier and the back-end detector, were designed and implemented and their performance summary are given below.

A transimpedance amplifier with differential dc-coupled photocurrent sensing was integrated in a standard 0.35  $\mu$ m CMOS. It achieves 33k $\Omega$  transimpedance gain and a bandwidth of 255 MHz with a 2pF photodiode capacitance. This design exhibits 40dB power supply rejection ratio and an average input noise of  $6.8 pA/\sqrt{Hz}$ . Power dissipation is 30mW from a 3V supply. Also, an active dc photocurrent rejection circuit was included in this circuit to prevent the circuit output from saturation under intense background light.

A 1Gb/s analog Viterbi detector based on a 4-PAM duobinary scheme was designed in a 0.25µm CMOS process. This chip is the first integrated implementation of an *analog* reduced state sequence detector. Pipelining structure and parallel processing have been incor-

porated in this design for high-speed operation. Due to test equipment limitations, experimental results are given for 200 Mb/s operation while simulation results indicate a speed of 1 Gb/s. Power dissipation is 55mW from a 2.5V supply while occupying 0.78mm<sup>2</sup> of area. Although a duobinary scheme has been the focus of this work for its application in optical links, this design can be readily modified or extended to other PRS schemes such as dicode and PR4.

## Acknowledgment

I wish to express my deepest gratitude to Prof. David A. Johns for his invaluable assistance and inspirational supervision. I am indebted to him for all the academic, financial and moral support he provided for me.

I would like to thank the members of my PhD thesis committee Profs. S. Pasupathy, W.T. Ng, F. Najm, J. Long and G. Cauwenberghs.

My thanks is also extended to administration staff in the Department of Electrical and Computer Engineering and in particular to Sarah Cherian and Judith Levene for their compassionate support. To Jennifer Rodrigues for her help at anytime.

I am always honored to have the opportunity to learn from so many sincere friends. My especial thanks to Dr. Mohammad Hossein Shakiba, Profs. Khoman Phang and Anthony Carusone, Amir Hadji-Abdolhamid, Steve Hranilovic, Shahriar Mirabbasi, Takis Zourntos, Tooraj Esmailian and Mehrdad Ramezani. I also learnt from the fruitful conversations and debates with Sebastian Magierowski, Raj Mahadevan, Cameron Lacy, Kasra Ardalan, Sotoudeh Hamedi-Hagh and my other colleagues in room EA104.

To my parents for their continual support and devotion and for their encouragement to make this journey possible for me. My heart is always with you. To my brother, Behnam, who cheerfully took over all my responsibilities when leaving home and prepared a peace of mind for me to accomplish this work. May god help me to deserve your so loving dedication.

To my wife Fariba and my daughter Neekoo for their relentless inspiration throughout this work. How could I even imagine of this achievement without your perpetual support. Thank you so much for your patience and love.

# **Table of Contents**

| CHAPTER 1 | Introduction                                   | 1   |

|-----------|------------------------------------------------|-----|

| CHAPTER 2 | Background                                     | 7   |

| 2.1       | Partial Response Signalling and Detection      |     |

|           | Techniques 7                                   |     |

|           | 2.1.1 Nyquist System 8                         |     |

|           | 2.1.2 Partial Response Signalling 9            |     |

|           | 2.1.3 Detection Techniques in PRS 11           |     |

|           | 2.1.4 Analog Viterbi Detectors 16              |     |

| 2.2       | Optical Wireless Communications 18             |     |

|           | 2.2.2 Modulation Schemes 21                    |     |

|           | 2.2.3 Noise 22                                 |     |

|           | 2.2.4 Preamplifiers 22                         |     |

| 2.3       | Application of Modulation and Detection        |     |

|           | Techniques in Optical Wireless                 |     |

|           | Communications 27                              |     |

| 2.4       | Summary 33                                     |     |

| 2.5       | References 35                                  |     |

| CHAPTER 3 | Fully Differential DC-Coupled                  |     |

|           | Transimpedance Amplifier                       | 37  |

| 3.1       | Circuit Implementation 38                      |     |

|           | 3.1.1 The Photodiode Biasing Circuit 40        |     |

|           | 3.1.2 The Differential Amplifier 41            |     |

|           | 3.1.3 The DC Photocurrent Rejection Circuit 44 |     |

| 3.2       | Output Buffer 46                               |     |

| 3.3       | Noise Performance 47                           |     |

| 3.4       | Experimental Results 48                        |     |

| 3.5       | Summary 51                                     |     |

| 3.6       | references 53                                  |     |

| CHAPTER 4 | Analog Reduced-State Sequence                  |     |

|           | Detection: System and Circuit Design           | 54  |

| 4.1       | 4-PAM Signalling 56                            | - • |

| 4.2                                          | Reduced-State Viterbi Detector 57                                                                                                                                      |     |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                              | 4.2.1 System Approach 57                                                                                                                                               |     |

|                                              | 4.2.2 Performance Evaluation 66                                                                                                                                        |     |

|                                              | 4.2.3 RSSD for other PRS 68                                                                                                                                            |     |

| 4.3                                          | Analog RSSD 71                                                                                                                                                         |     |

|                                              | 4.3.1 Circuit Design 71                                                                                                                                                |     |

|                                              | 4.3.2 Pipelining Structure 76                                                                                                                                          |     |

|                                              | 4.3.3 Path Memory 80                                                                                                                                                   |     |

|                                              | 4.3.4 Comparator Offset Effects 81                                                                                                                                     |     |

| 4.4                                          | Building Blocks 82                                                                                                                                                     |     |

|                                              | 4.4.1 Voltage-to-Current Converter 83                                                                                                                                  |     |

|                                              | 4.4.2 Comparators 84                                                                                                                                                   |     |

|                                              | 4.4.3 Input Quantizing Circuit 86                                                                                                                                      |     |

|                                              | 4.4.4 Input Sample and Holds 88                                                                                                                                        |     |

|                                              | 4.4.5 Offset Generators 89                                                                                                                                             |     |

|                                              | 4.4.6 Clock Generator 90                                                                                                                                               |     |

| 4.5                                          | Summary 91                                                                                                                                                             |     |

| 4.6                                          | References 92                                                                                                                                                          |     |

|                                              |                                                                                                                                                                        |     |

| CHAPTER 5                                    | Analog Reduced-State Sequence                                                                                                                                          |     |

|                                              | <b>Detection: Experimental Results</b>                                                                                                                                 | 94  |

| 5.1                                          | Layout 94                                                                                                                                                              |     |

|                                              | 5.1.1 Clock Buffers 97                                                                                                                                                 |     |

|                                              | 5.1.2 Digital I/O Line Translators 97                                                                                                                                  |     |

|                                              |                                                                                                                                                                        |     |

| 5.2                                          | Test Set-Up 99                                                                                                                                                         |     |

| 5.3                                          | Experimental Results 101                                                                                                                                               |     |

| 5.3<br>5.4                                   | Experimental Results 101 Summary 102                                                                                                                                   |     |

| 5.3                                          | Experimental Results 101                                                                                                                                               |     |

| 5.3<br>5.4                                   | Experimental Results 101 Summary 102                                                                                                                                   | 104 |

| 5.3<br>5.4<br>5.5<br>CHAPTER 6               | Experimental Results 101 Summary 102 References 103  Conclusions and Future Directions                                                                                 | 104 |

| 5.3<br>5.4<br>5.5                            | Experimental Results 101 Summary 102 References 103                                                                                                                    | 104 |

| 5.3<br>5.4<br>5.5<br>CHAPTER 6<br>6.1        | Experimental Results 101 Summary 102 References 103  Conclusions and Future Directions Summary and Conclusions 104                                                     | 104 |

| 5.3<br>5.4<br>5.5<br>CHAPTER 6<br>6.1        | Experimental Results 101 Summary 102 References 103  Conclusions and Future Directions Summary and Conclusions 104                                                     | 104 |

| 5.3<br>5.4<br>5.5<br>CHAPTER 6<br>6.1<br>6.2 | Experimental Results 101 Summary 102 References 103  Conclusions and Future Directions Summary and Conclusions 104 Future Directions 106                               | 104 |

| 5.3<br>5.4<br>5.5<br>CHAPTER 6<br>6.1<br>6.2 | Experimental Results 101 Summary 102 References 103  Conclusions and Future Directions Summary and Conclusions 104 Future Directions 106  Study of Adjacency in Branch | 104 |

### **List of Tables**

- Table 2.1: Specification for some optical wireless and RF systems

- Table 2.2: Optical power and bandwidth requirements for some intensity modulation schemes

- Table 3.1: Performance Summary

- Table 3.2: Comparison with previous work

- Table 4.1: Branch extension and their metrics

- Table 4.2: Branch extension and difference metric update of state I

- Table 4.3: Branch extension and difference metric update of state III

- Table 4.4: Branch extension and difference metric update of state V

- Table 4.5: Branch extension and difference metric update of state I in dicode PRS

- Table 5.1: Performance Summary

- Table A.1: Survived metrics for the adjacent states  $b_0(n-1)$  and  $b_1(n-1)$

# **List of Figures**

- Fig. 2.1: The minimum-bandwidth Nyquist systems with normalized  $T_s(1/f_s)=1$ sec, a: Impulse response b: Frequency

- Fig. 2.2: The duobinary PRS system with normalized  $T_s(1/f_s)=1$  sec, a: Impulse response, b: Frequency response

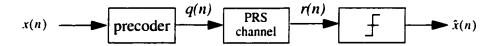

- Fig. 2.3: A partial-response encoder model

- Fig. 2.4: Symbol-by-symbol detection using DFE

- Fig. 2.5: Symbol-by-symbol detection using precoder/slicer

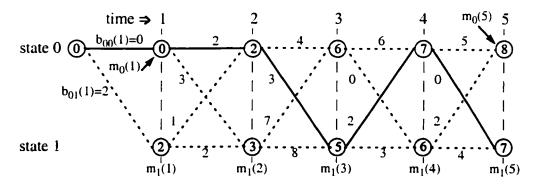

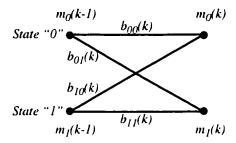

- Fig. 2.6: A typical two-state trellis diagram

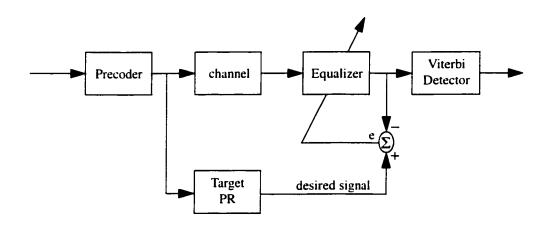

- Fig. 2.7: A typical transceiver with adaptive equalizers at the front of the detector

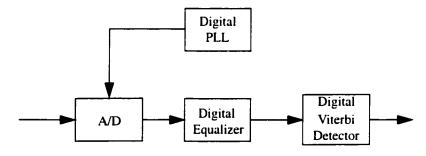

- Fig. 2.8: The receiver architecture in the presence of digital Viterbi detector

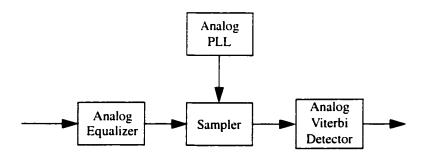

- Fig. 2.9: The receiver architecture in the presence of analog Viterbi detector

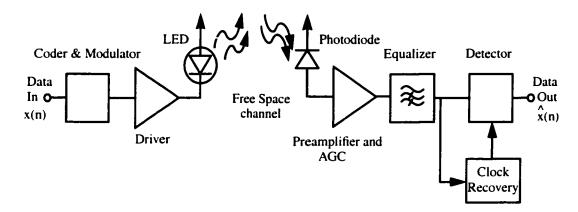

- Fig. 2.10: A typical optical wireless transceiver system

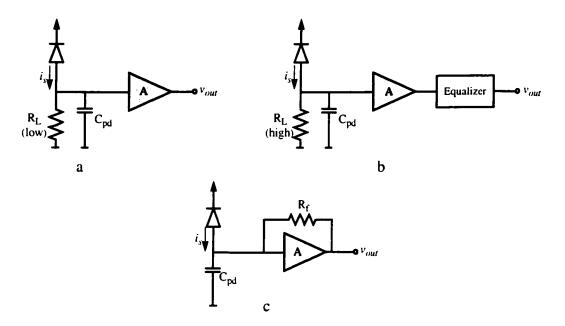

- Fig. 2.11: Three optical preamplifier structures, at low input impedance, bt high input impedance, ct transimpedance amplifier

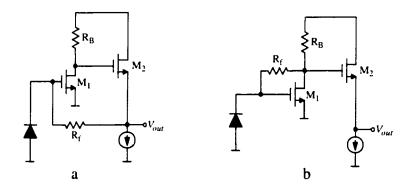

- Fig. 2.12: Common-source transimpedance amplifiers

- Fig. 2.13: Common-gate transimpedance amplifiers

- Fig. 2.14: Common-gate transimpedance amplifiers with RGC circuit

- Fig. 2.15: AC-coupled fully differential transimpedance amplifier

- Fig. 2.16: A typical optical transceiver model

- Fig. 2.17: Frequency response of the optical channel without equalization

- Fig. 2.18: Detection techniques, a: peak detection, b: DFE, c: Viterbi decoder

- Fig. 2.19: Frequency response for pulse slimming equalizer (symbol-rate=1GHz)

- Fig. 2.20: Frequency response for pulse slimming equalizer (symbol-rate=1GHz)

- Fig. 2.21: BER versus SNR for different detection techniques in 2-PAM scheme

- Fig. 2.22: Frequency response for pulse slimming equalizer (symbol-rate=500MHz)

- Fig. 2.23: Frequency response for 1+D equalizer (symbol-rate=500MHz)

- Fig. 2.24: SER versus SNR for different detection techniques using 4-PAM scheme

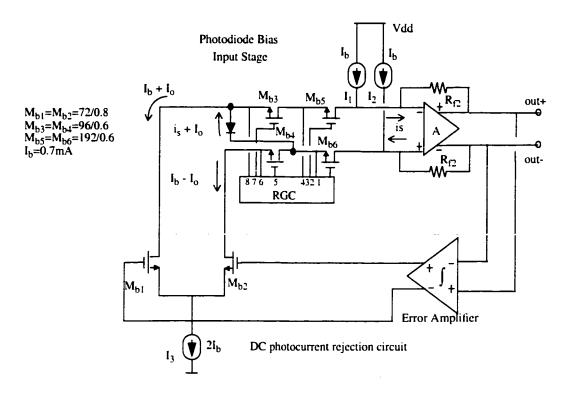

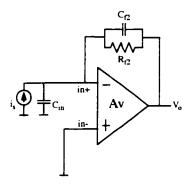

- Fig. 3.1: Basic structure of the proposed transimpedance amplifier

- Fig. 3.2: Photodiode bias input stage

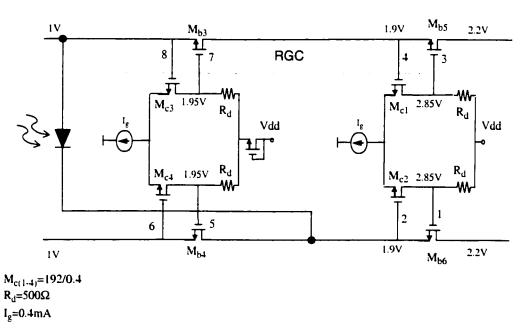

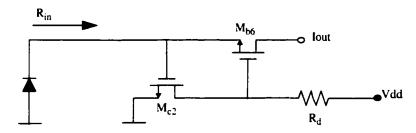

- Fig. 3.3: Equivalent half-circuit of RGC

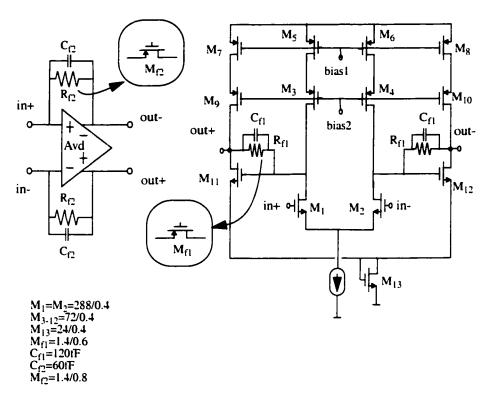

- Fig. 3.4: Differential amplifier circuit

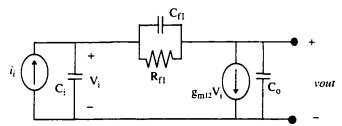

- Fig. 3.5: Single-ended circuit for frequency response calculation

- Fig. 4.Simplified model for the second stage

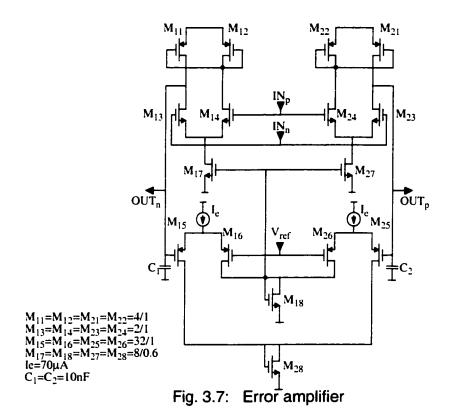

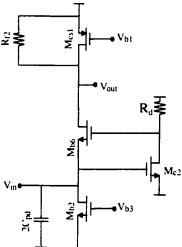

- Fig. 3.7: Error amplifier

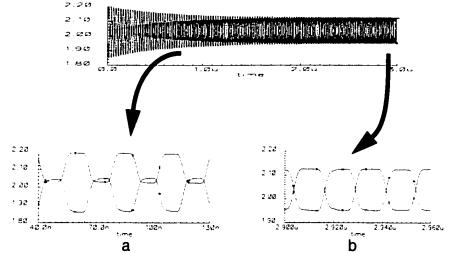

- Fig. 3.8: DC photocurrent rejection, a: dc rejection in progress, b: dc rejection completed

- Fig. 3.9: Output buffer

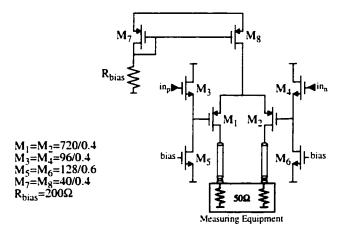

- Fig. 3.10: Frequency response of the output buffer

- Fig. 3.11: Input half-circuit used for noise calculation

- Fig. 3.12: Circuit test set-up

- Fig. 3.13: Measured preamplifier frequency response for different photodiode capacitances

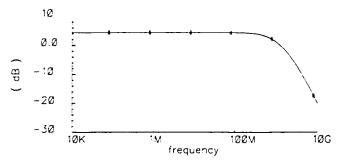

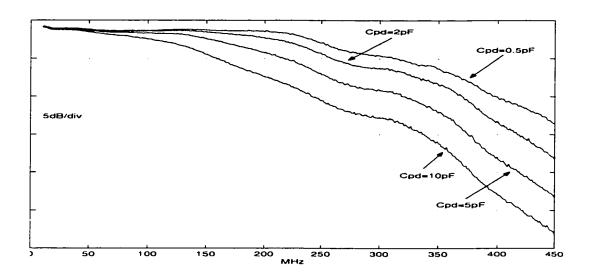

- Fig. 3.14: Measured output noise

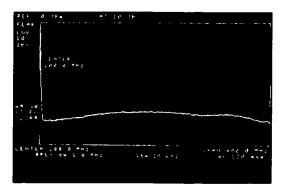

- Fig. 3.15: Eye diagrams with C<sub>pd</sub>=5pF: a) 200 Mbps, b) 400 Mbps

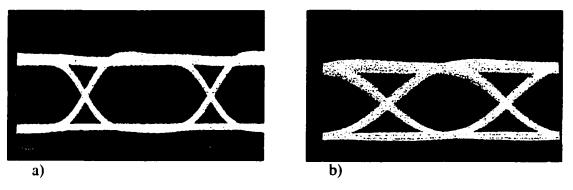

- Fig. 3.16: Chip Micrograph

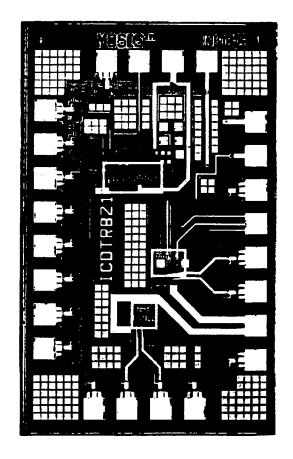

- Fig. 4.1: A two-state trellis diagram

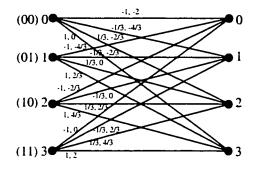

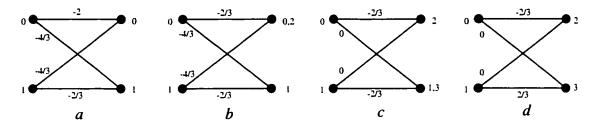

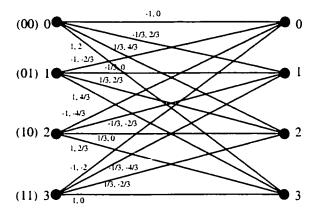

- Fig. 4.2: Full state trellis diagram for a 4-PAM duobinary PRS scheme. Branch labels represent the pairs of *uncoded* and *encoded* signals

- Fig. 4.3: Typical possible survivors in duobinary 4-PAM RSSD starting from the states (0,1)

- Fig. 4.4: Two-state reduced trellis diagram

- Fig. 4.5: Two state presentation of the categories in Fig. 4.3

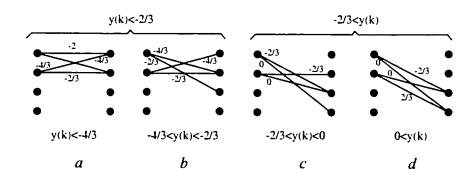

- Fig. 4.6: Typical branch metrics for the example categories (c) and (d)

- Fig. 4.7: Minimum-distance error event paths for a full-state and reduced-state detector in 4-PAM Signalling

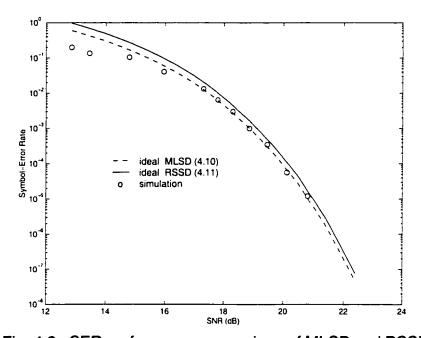

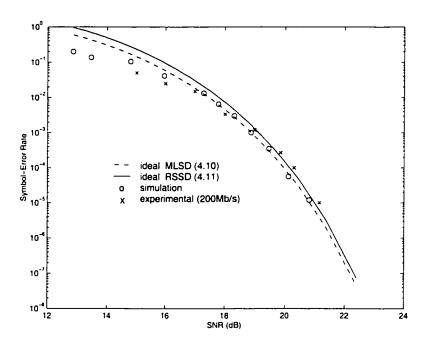

- Fig. 4.8: SER performance comparison of MLSD and RSSD

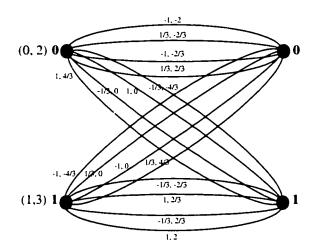

- Fig. 4.9: Full state trellis diagram for a 4-PAM dicode PRS scheme. Branch Labels represent the pairs of *uncoded* and *encoded* signals

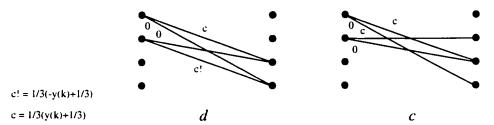

- Fig. 4.10: Front-end quantizer circuit

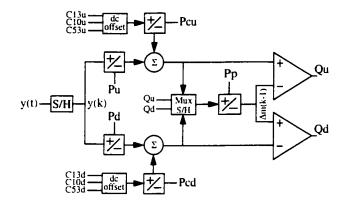

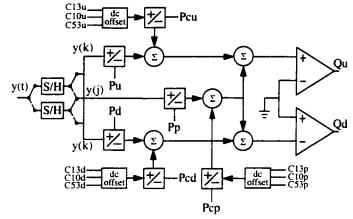

- Fig. 4.11: Analog core of the processing circuit

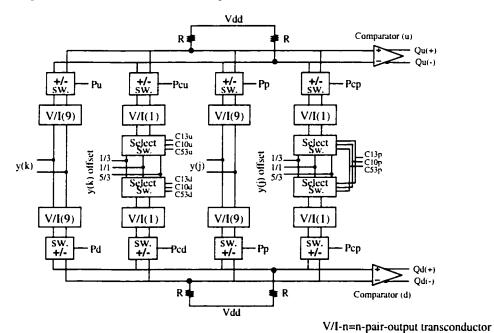

- Fig. 4.12: Improved structure for the analog core

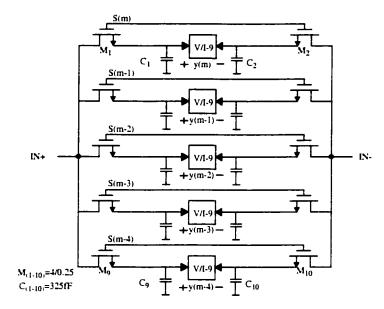

- Fig. 4.13: Practical structure for circuit realization of Fig. 4.11

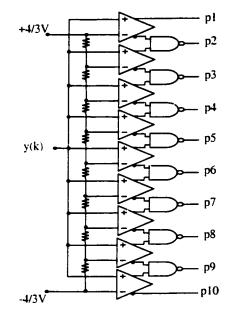

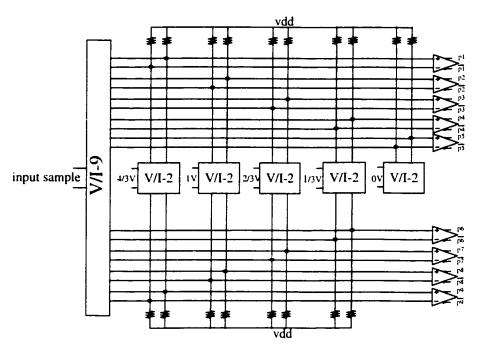

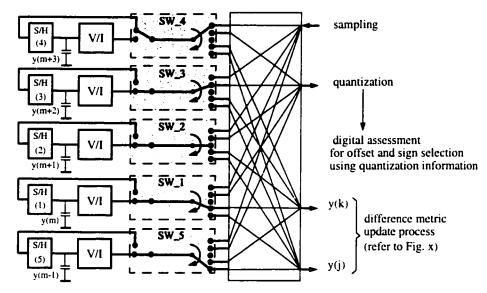

- Fig. 4.14: Current-mode realization of the front-end quantizer

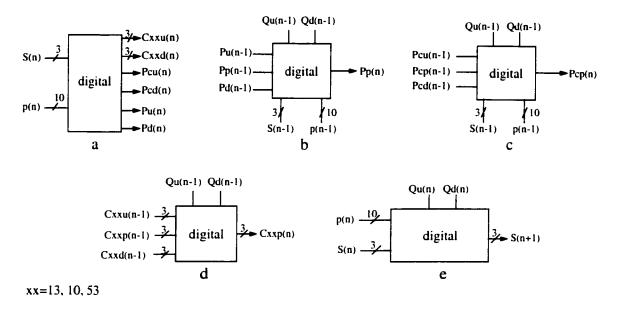

- Fig. 4.15: Digital processing blocks

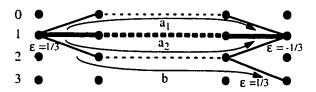

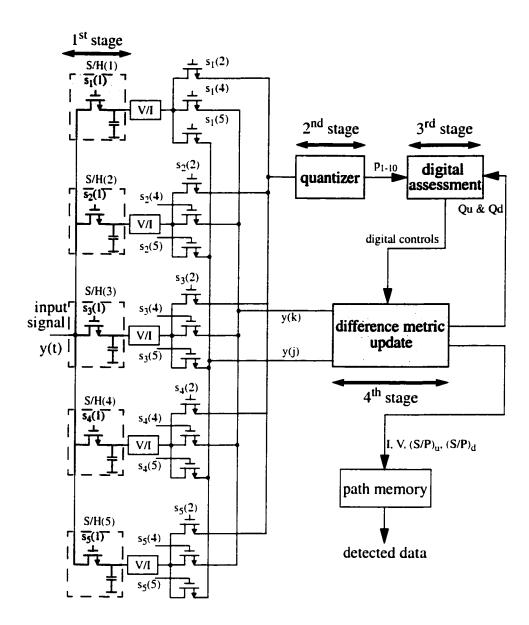

- Fig. 4.16: The circuit processing stages in pipelining structure

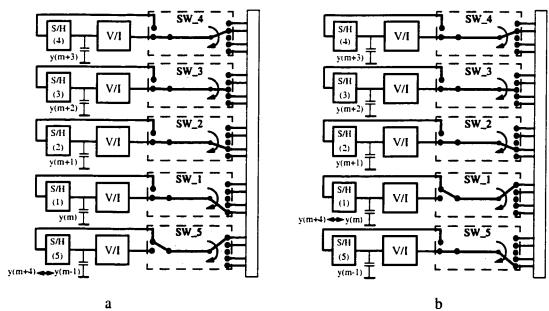

- Fig. 4.17: Selective switches and connections in the circuit pipelining configuration

- Fig. 4.18: Typical rotation of S/Hs when a: Qu or Qd =1 and b: Qu=Qd=0

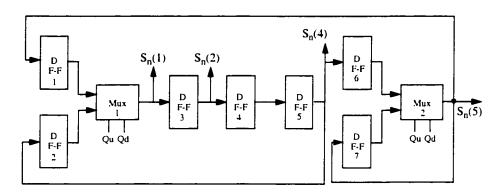

- Fig. 4.19: Rotation management digital circuit

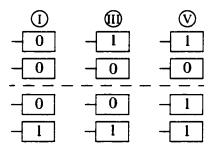

- Fig. 4.20: Three possible path memory inputs

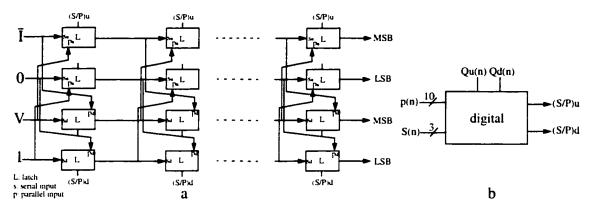

- Fig. 4.21: Path memory a: circuit, b: digital controls

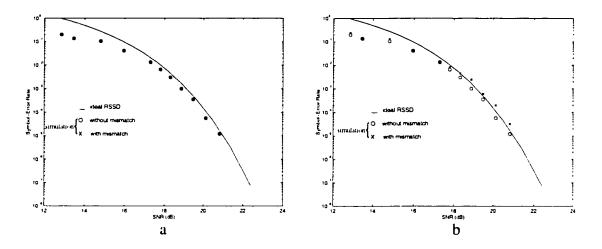

- Fig. 4.22: Simulated SER performance comparison, a: 5% dc offset in the front-endcomparators, b: the same dc offset in the back-end comparators

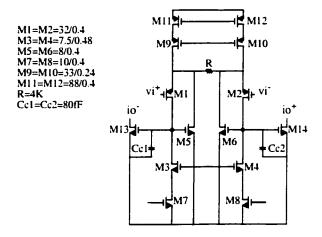

- Fig. 4.23: Transconductor circuit

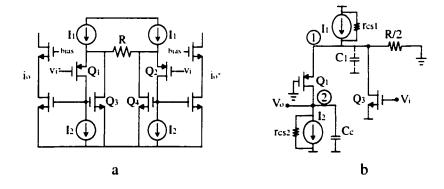

- Fig. 4.24: Transconductor a: simplified circuit, b: half-circuit open-loop circuit

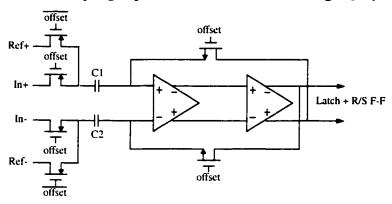

- Fig. 4.25: Front-end preamplifiers of the comparator and their connections

- Fig. 4.26: The comparator circuit

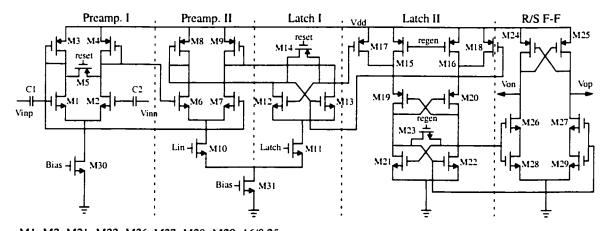

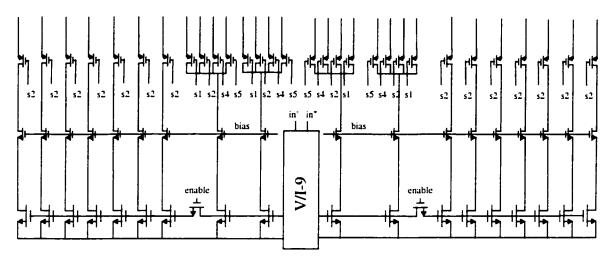

- Fig. 4.27: Nine-differential-output transconductor (V/I-9)

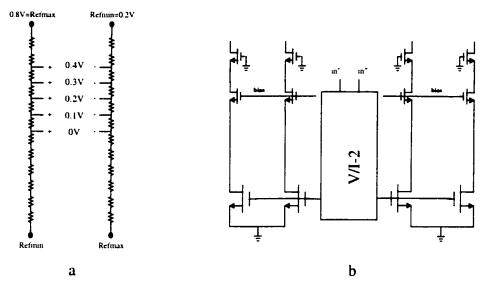

- Fig. 4.28: Reference generating circuit a: differential ladder resistors, b: two-differential-output transconductor (V/I-2)

- Fig. 4.29: Input sample-and-holds circuit

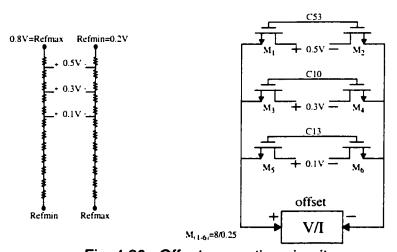

- Fig. 4.30: Offset generating circuit

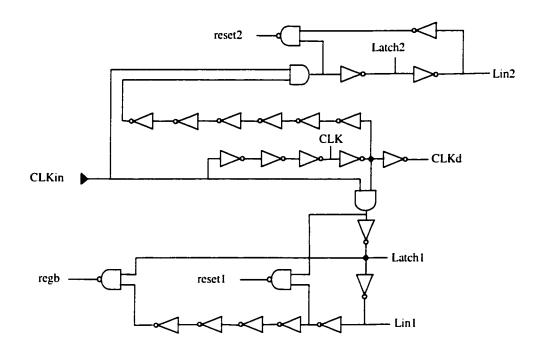

- Fig. 4.31: The clock generating circuit

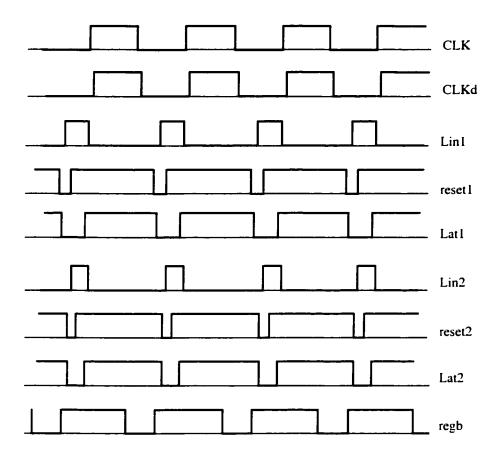

- Fig. 4.32: Output waveforms of the clock generator

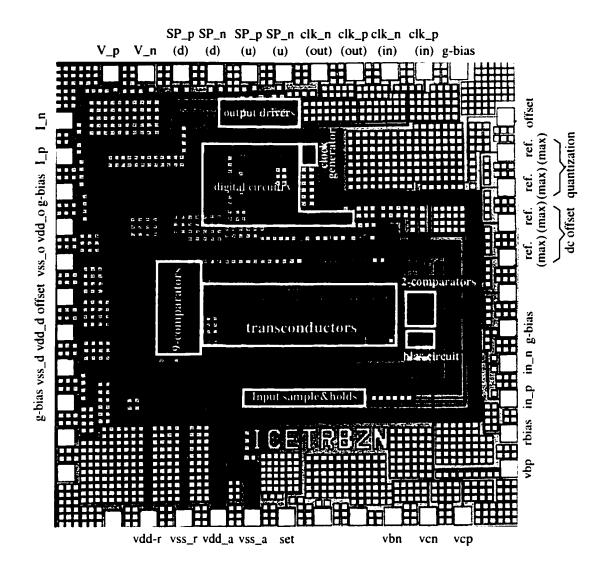

- Fig. 5.1: Chip photograph

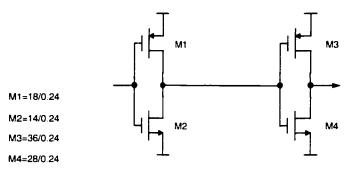

- Fig. 5.2: Digital two-stage buffer

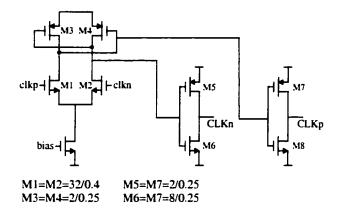

- Fig. 5.3: Differential low-swing input to full-swing output translator circuit

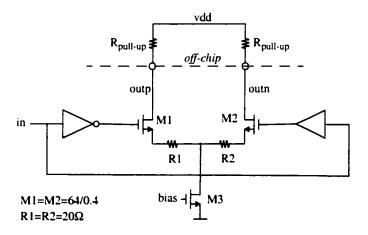

- Fig. 5.4: Full-swing input to low-swing differential output translator circuit

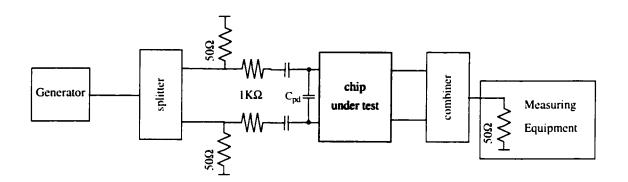

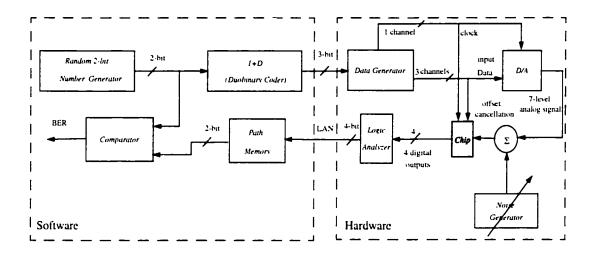

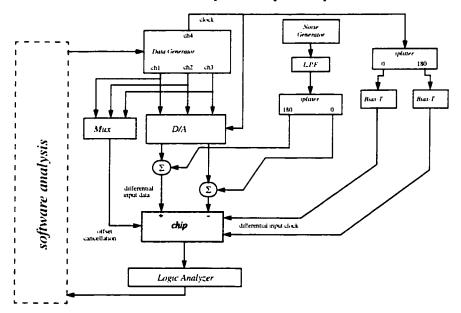

- Fig. 5.5: Test set-up

- Fig. 5.6: Input seven-level encoded signal eye diagram a: high SNR, b: low SNR

- Fig. 5.7: Input test signal and clock generator hardware

- Fig. 5.8: Measured BER performance

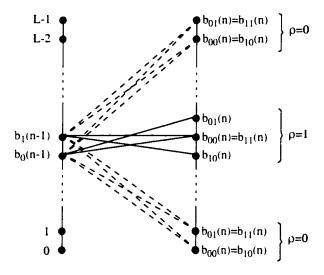

- Fig. A.1: Possible branch extensions form the adjacent states  $b_0(n-1)$  and  $b_1(n-1)$

#### **CHAPTER**

1

## Introduction

Optical Communications has revolutionized information technology in the past few years. Light beams which lend themselves admirably to the ever-increasing demand for higher data rates enjoy an unmatched channel bandwidth due to the nature of photons which constitute an optical signal and react weakly to their environment and each other as opposed to electrons [1]. Nowadays, the mention of optical communications, most-likely implies fiber optic communications. With an exponential increase in the number of nodes, a load of as high as 11 Tb/s is expected for global Internet backbone by the year 2005 [2] which has urged wide-area networks (WANs) and local-area networks (LANs) to switch their media from copper to fiber. This in return has prompted a tremendous amount of investigation for low-cost, low-power integrated fiber-optic transceivers. Despite the enormous achievements in this area, fiber optics still remain an expensive choice for network expansion mostly due to the installation and trenching costs. Alternatively, optical wireless communications offers the speed of the optics without the expense of fiber.

Optical wireless communications (known within the industry as free-space optics

(FSO)) has compelling economic advantages to be incorporated in gigabit-per-second rates over metropolitan distances of a few city blocks or as a last-mile access which connects end-users with Internet service providers [3][4]. These free-space systems which in their full-scale and reliable setup require less than one fifth of the budget needed for a ground-based fiber optics [5] possess other advantages such as fast installation and flexible configuration. Optical equipment generally work at one of two wavelengths of 850 nm and 1550 nm. Lasers for 850 nm are much less expensive and are therefore favored for applications over moderate distances. On the other hand, 1550 nm lasers are less harmful to eye as their radiation are mostly absorbed by the comea before reaching the retina and hence eye-safety regulations allow these longer wavelength beams to operate at powers of about two orders of magnitude higher than the shorter wave-length beams. Higher transmit power translates into longer range of operation at the same speed or alternatively higher rate of bits with the same distance. However, when it comes to the applications in shorter ranges within a building or a room and with multiple users, 1550 nm laser systems become unjustifiably expensive and lower 850 nm wave-length lasers face eye-safety regulations [6][7] which make it difficult for them operate efficiently.

Short-distance optical wireless communications target low-cost high-speed data exchange. Operating in 850 nm wave-length, inexpensive LEDs can produce substantial launch powers and yet be eye safe [7][8]. This is due to the fact that LEDs are not point source devices as are lasers and do not damage the retina of the eye. However, short-distance optical wireless environment is far from ideal. Optical receivers in this type of link must use photodiodes with a significantly large active area to alleviate fine-alignment problems which in turn impose a relatively large capacitance at the input of the receiver and seriously impact frequency performance. Furthermore, LEDs are slower than laser diodes and their rise and fall time are significant which also introduce a delay at the transmitter side. Stray lights such as sun beam and artificial lights result in some noise components at the received signal and are limiting factors in the receiver sensitivity and dynamic range. When dealing with a channel with these imperfections, sophisticated methods need to be employed for channel coding and data detection to maintain high data throughputs.

In band-limited channels, partial response signalling [9] and multi-level modulation schemes can be invoked to establish high data throughputs. This can be achieved by tolerating more complexity in the receiver side. Sequence detection has been proved to be the optimal technique [10] to recover the received data and the Viterbi detection is a practical algorithm to realize a maximum-likelihood sequence detection [11]. In the past few years, analog Viterbi detectors have acquired a lot of attention as they can operate with lower power compared with a traditional digital architecture mostly due to the elimination of A/Ds from the front-end [12-16]. With the increased number of the states in multi-level schemes, the complexity of the Viterbi decoders becomes more serious and utilizing an algorithm to reduce the number of states and hence complexity becomes much more appealing. Reduced-state Viterbi detection is an algorithm which reduces the number of survived states to only most probable states and hence reduces the complexity by ignoring the other states without any notable compromise in performance.

The present work studies the implementation of a 1 Gb/s optical wireless communications for short-range applications. Assuming a trivial design on the transmitter side, most attention has been paid to the receiver. A new architecture is introduced for the front-end transimpedance amplifier as well as an analog reduced-state Viterbi detector for 4-PAM duobinary partial-response signalling. The organization of this thesis is as follows:

Chapter 2 provides the basic background needed for the rest of the thesis. Two major discussions in this chapter are:

- -Partial response signallings and their detection techniques

- -Optical wireless communications

In the first section of this chapter, the general idea behind partial-response signalling and its prominent advantage over Nyquist systems in band-limited channels is given. This is followed by the discussion about two main detection techniques for this type of signalling, symbol-by-symbol and sequence detection where DFE and the Viterbi detectors have been addressed as special cases of these methods, respectively. In the next section of chapter 2, two major intensity modulation schemes, PAM and PPM are reviewed and different

preamplifier architectures as the receiver front-end module are studied. In the last section of this chapter, as a case study for a typical optical wireless channel, equalizer characteristics as well as symbol error-rate performances for different types of detection techniques and signalling schemes are investigated.

Chapter 3 describes the design and implementation of a new fully differential transimpedance amplifier. This circuit employs a dc coupling configuration to sense the photocurrent fully differentially and hence improves signal-to-noise and common-mode rejection

ratios. The proposed transimpedance amplifier uses a regulated cascode circuit at the input

to lower the input impedance and so isolates the photodiode capacitance from the rest of

the circuit. Providing this isolation, the circuit bandwidth is shown to be fairly independent

of large variation in input capacitance. An active dc rejection circuit included in this transimpedance amplifier, eliminates the effect of dc currents produced by the ambient light

and hence prevents the circuit from saturation under intense background beams. Experimental results such as frequency response, noise performance, and transient response have

also been presented in this chapter.

In chapter 4, after establishing a comprehensive basis for the system design of an analog reduced-state sequence detector, the circuit-level design of the alternative components in this detector has been elaborated. It is shown in this chapter that as the result of unavoidable delays in the analog and digital processing circuits, attaining the desired speed (1Gb/s) within a sample period is difficult and hence some techniques such as pipelining and parallel processing have been incorporated to achieve the target speed. A discussion about practical nonidealities and imperfections and the required accuracy for comparators in the front-end and back-end stages are also given in this chapter.

In chapter 5, experimental results and layout issues have been explained. In layout, matching considerations and some provision for substrate noise reduction are described. The test set-up followed by the performance evaluation are covered in the final part of this chapter.

Finally, in chapter 6, a summary of thesis contributions is given and directions for fur-

ther work are discussed.

#### References

- [1]M. Montrose, Printed Circuit Board Design Techniques for EMC Compliance, *IEEE Press*, New York, 1996.

- [2]J. Savoj, B. Razavi, "A 10-Gb/s CMOS Clock and Data Recovery Circuit with a Half-Rate Linear Phase Detector," *IEEE J. Solid-State Circuits*, Vol. 36, No. 5, May 2001, pp. 761-767.

- [3]D. W. Faulkner, D. B. Payne, J. R. Stern and J. W. Ballance, "Optical Networks for Local Loop Applications," *IEEE J. Lightway Tech.*, Vol. 7, No. 11, Nov. 1989, pp. 1741-1751.

- [4]T. Kwok, "A Vision for Residential Broadband Services: ATM-to-the-Home," *IEEE Networks*, Vol. 9, No. 5, Sep.-Oct. 1995, pp. 14-28.

- [5]H. A. Willebrand and B.S. Ghuman, "Fiber Optics without Fiber," *IEEE Spectrum*, Aug. 2001, pp. 40-45.

- [6] International Electrotechnical Commission, "Safety of Laser Products Part I: Equipment Classification, Requirements and User's Guide," *Group Safety Publication*, Ref. No. 825-1, 1993.

- [7]D. J. T. Heatly, D. R. Wisely, I. Neild, and P. Cochran, "Optical Wireless: The Story So Far," *IEEE Communications Magazine*, Dec. 1998, pp. 72-82.

- [8]J. M. Kahn and J. R. Barry, "Wireless Infrared Communications," *Proceedings of the IEEE*, Vol. 85, No. 2, Feb. 1997, pp. 263-298.

- [9]P. Kabal and S. Pasupathy, "Partial-Response Signaling," *IEEE Trans. Commun.*, Vol. 23, No. 9, Sep. 1975, pp. 921-934.

- [10]E. A. Lee and D.G. Messerschmitt, "Digital Communication," *Kluwer Academic Publishers*, 1994.

- [11]G. D. Forney, Jr., "Maximum-Likelihood Sequence Estimation of Digital Sequences in the Presence of Intersymbol Interference," *IEEE Trans. Inform. Theory*, Vol. 18, No.3, May 1972, pp. 363-378.

- [12]T. W. Matthews, R. R. spencer, "An Integrated Analog CMOS Viterbi Detector for Digital Magnetic Recording," *IEEE J. Solid-State Circuits*, Vol. 28, No. 12, Dec. 1993, pp. 1294-1302.

- [13]M. H. Shakiba, D. A. Johns and K. W. Martin, "An Integrated 200-MHz 3.3-V BICMOS Class-IV Partial-Response Analog Viterbi Decoder," *IEEE J. Solid-State Circuits*, Vol. 33, No. 1, Jan. 1998, pp. 61-75.

- [14]A. Demosthenous and J. Taylor, "Low-Power CMOS and BICMOS Circuits for Analog Convolutional Decoders," *IEEE Trans. Circuits and Systems-II*, Vol. 46, No. 8, Aug. 1999, pp. 1077-1080.

- [15]Kai He and Gert Cauwenberghs, "Performance of Analog Viterbi Decoding," *Proc. Midwest Symp. Circuits and Systems*, Vol. 1, 2000, pp. 2-5.

- [16]Kai He and Gert Cauwenberghs, "Integrated 64-State Parallel Analog Viterbi Decoder," *Proc. IEEE Int. Symp. Circuits and Systems*, Vol. 4, 2000, pp. 761-764.

#### CHAPTER

# 2

# **Background**

This chapter is a survey of the required background for the thesis. In the first section, partial response signalling schemes and their detection techniques have been reviewed. Optical wireless communications with emphasis on modulation schemes and transimpedance amplifiers has been addressed in the second section. Finally, some special application of the introduced modulation and detection techniques in optical wireless communication systems have been investigated in the last section.

#### 2.1 Partial Response Signalling and Detection Techniques

In digital data communication systems, for an interference-free data exchange, signals require a broad-spectrum channel extending from low frequencies up to high frequencies large enough to accommodate their main frequency content. Free-space wireless and twist-ed-pair wires as well as magnetic and optical storage systems are examples of popular links for data transmission. Unfortunately, many practical data communication channels are band-limited and unable to provide the required bandwidth especially for high data

rates. For example, unshielded twisted-pair (UTP) telephone copper lines which were originally intended only for voice-band communications are currently under investigation to be included in the next generation broadband access networks. Very high rate digital subscriber line (VDSL) is targeting a downstream data transmission of as high as 55 Mbps over UTPs. In the meantime, in optical storage systems, a great deal of research is underway to proliferate the existing holding capacity of DVDs from 4.7 Gbytes to 17 Gbytes [1] [2]. With the increase in the data transmission rate and the bandwidth limitation of the available channels, the effect of adjacent pulses on the received pulse is unavoidable. This effect introduces a common form of interference in band-limited channels which is called intersymbol interference (ISI). Intersymbol interference is a major source of bit errors in the recovered data at the receiver and its effect worsens when pushing the channel toward higher data rates.

ISI rejection in band-limited channels can be achieved by incorporating high-pass equalizers. However, their noise enhancement at high frequencies deteriorate the noise performance. On the other hand, there exist some equalizers with less high frequency boost that result in a controlled amount of intersymbol interference.

In this section after introducing some minimum-bandwidth communication systems such as Nyquist and partial response signalling (PRS) systems, detection techniques that can be used to retrieve the transmitted data are addressed.

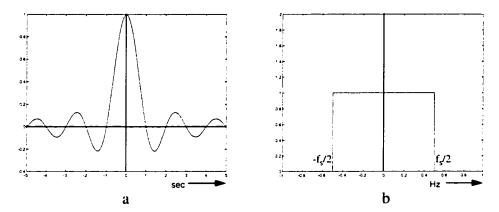

#### 2.1.1 Nyquist Systems

The fundamental idea behind Nyquist systems is that the received sample values should not be a function of other adjacent samples. This requires that the sampled values of the impulse response of the channel be zero at the non-corresponding data instants. A particular family of pulses which satisfy the Nyquist requirements and are widely used are raised cosine pulses [3]. The minimum bandwidth requirement for these pulses start from (BW=1/2T) for a symbol period of T and the excess bandwidth coefficient of O, as shown in Fig. 2.1. Since the design of brick-wall filters as shown in Fig. 2.1.b is practically impossible, it is common practice to use some excess bandwidth thereby reducing the sharpness

of the frequency transition edge.

Fig. 2.1: The minimum-bandwidth Nyquist systems with normalized  $T_s(1/f_s)=1$  sec, a: Impulse response b: Frequency

However, in this thesis, we will focus on minimum bandwidth systems (discussed below) and so the reader is referred to [3] for more information on Nyquist systems.

#### 2.1.2 Partial Response Signalling

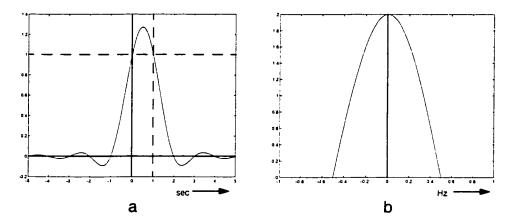

As discussed above, although the minimum channel bandwidth is half the data symbol rate for zero intersymbol interference, an excess bandwidth is always required. To maintain the same bandwidth as the brick-wall filter shown in Fig.2.1.b but with a smoother shape, one can introduce some controlled ISI in time domain. With a predictable amount of ISI, the correct transmitted data can be recovered by using a more complex design in the receiver. These minimum bandwidth filters can be realized by introducing some non-zero values for the pulse filter in non-corresponding instants. For a simple case of duobinary signalling scheme, 1+D, [4] depicted in Fig. 2.2 where *D* denotes a unit delay, in addition to the desired non-zero value at time zero in Fig. 2.2.a, a non-zero value at time *I* is also introduced as a controlled interference. The frequency response of the channel is shown in Fig. 2.2.b and demonstrates a low-pass response with a bandwidth of *1/2T*.

Fig. 2.2: The duobinary PRS system with normalized  $T_s(1/f_s)=1$  sec, a: Impulse response, b: Frequency response

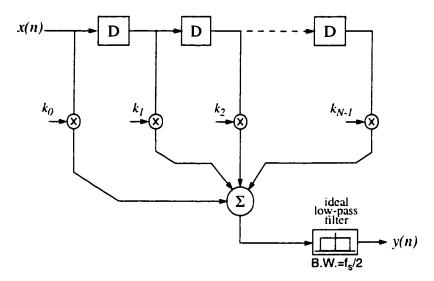

The concept of generating duobinary scheme was then generalized in [5], leading to the signalling technique named partial response signalling (PRS). The construction of PRS is illustrated in Fig. 2.3 where the filter function is a polynomial given by (2.1) which is band limited by an ideal low-pass filter to 1/2T.

$$F(D) = k_0 + \sum_{i=1}^{N-1} k_i D^i = k_0 \left[ 1 + \sum_{i=1}^{N-1} (k_i / k_0) D^i \right] = k_0 [1 + K(D)]$$

(2.1)

In practice, an appropriate polynomial which best characterizes the channel behavior is incorporated as the model. For example, in optical communications in addition to duobinary partial response, other form of polynomials representing low-pass channels such as  $(1+D)^n(1+kD+D^2)$  are also used to model fiber, wireless and recording optic channels [6][7][8]. In another applications, PRS modeling of the magnetic recording channels with some nulls at dc can be easily realized by introducing a  $(1-D)^n$  factor to the coding polynomial [9][10].

Fig. 2.3: A partial-response encoder model

#### 2.1.3 Detection Techniques in PRS

The detection of partial response signals can be accomplished by the removal of the introduced ISI based on the channel polynomial-form model. Two detection methods of symbol-by-symbol and maximum-likelihood are generally applied to retrieve the transmitted symbols. The first method normally employs a decision-feedback equalizer (DFE) to remove ISI. The latter method with a little more complexity, minimizes the probability of error by considering the sequence of symbols and takes advantage of the information embedded in ISI.

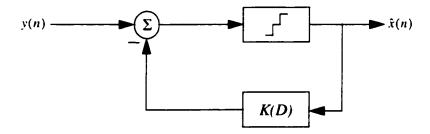

#### A. Symbol-by-Symbol Detection

DFE is a commonly used method in symbol-by-symbol detection. DFEs in comparison with linear equalizers such as zero-forcing filters operate with less noise-enhancement. In this detection method, as illustrated in Fig. 2.4, the transmitted data can be recovered by subtracting the effect of previous input symbols from the current received sample.

Fig. 2.4: Symbol-by-symbol detection using DFE

In practice, two major factors, noise and error propagation impact DFE performance. In Fig. 2.4, by applying (2.1) and assuming  $k_0=1$  for simplicity, the input sample is given by

$$y(n) = x(n) + \sum_{i=1}^{N-1} k_i x(n-i)$$

(2.2)

In the presence of additive noise, the input to the slicer can be defined by

$$s(n) = y(n) + v(n) - \sum_{i=1}^{N-1} k_i \hat{x}(n-i)$$

(2.3)

where v(n) is a noise sample. By replacing y(n) in (2.3) with its equivalent from (2.2) we will have

$$s(n) = x(n) + v(n) + \sum_{i=1}^{N-1} k_i [x(n-i) - \hat{x}(n-i)].$$

(2.4)

The above equation clarifies that the detected symbol can be affected by the added noise and the errors from the past decisions. To avoid this error propagation, as shown in Fig. 2.5, precoding can be implemented at the transmitter side.

Fig. 2.5: Symbol-by-symbol detection using precoder/slicer

To simplify the description of the precoding method, a duobinary channel has been adopted. In the receiver side, the precoder shown in Fig. 2.5, generates a new sequence defined by

$$p(n) = x(n) - p(n-1)$$

(mod 2) . (2.5)

Assuming a binary sequence x(n) of ls and ls for transmission, the resulted precoded p(n) will also be a sequence of ls and ls. Based on p(n) a stream q(n) of ls and ls is sent to the channel such that the channel input is set to ls when ls when ls and ls when ls and ls when ls and ls when ls and ls and

$$q(n) = 2p(n) - 1 (2.6)$$

The samples at the input of the slicer, r(n), are given by

$$r(n) = q(n) + q(n-1) = 2(p(n) + p(n-1) - 1)$$

(2.7)

Consequently,

$$\hat{x}(n) = p(n) + p(n-1) = \frac{1}{2}r(n) + 1 \tag{2.8}$$

The above equation implies that if  $r(n) = \pm 2$  then  $\hat{x}(n) = 0$  and if r(n) = 0 then  $\hat{x}(n) = 1$ . With the use of precoding in this technique, the detected sample at each time is independent of the previous samples and hence error propagation is avoided.

Based on the symbol-by-symbol detection techniques presented here, a lower bound for symbol error rate (SER) when error propagation is ignored can be defined by [9]

$$(SER)_{LB} = 2\left(1 - \frac{1}{M}\right)Q(1/\sigma) \tag{2.9}$$

where M is the number of modulating levels in pulse amplitude modulation (PAM) scheme,  $\sigma^2$  is the variance of the Gaussian noise v(n) and Q(x) is given by

$$Q(x) = \frac{1}{(2\pi)^{1/2}} \int_{r}^{\infty} \exp(-u^2/2) du$$

(2.10)

The upper bound when including error propagation is defined by [9]

$$(SER)_{UB} = \frac{M^{N-1}(SER)_{LB}}{\frac{M}{M-1}(M^{N-1}-1)(SER)_{LB}+1}$$

(2.11)

Equation (2.11) reveals that error propagation increases the error probability by at most a factor  $M^{N-1}$ .

Comparing DFE performance with that of an ISI-free channel shows a 3dB loss in DFE detection [11]. This is caused by the non-optimal detection technique of DFE which ignores ISI information and makes decision on the base of each received symbol. However, almost all the SNR loss in PRS symbol-by-symbol detection can be recovered by exploiting maximum-likelihood sequence detection [11].

#### B. Maximum-Likelihood Sequence Detection

For sequence detection in the presence of ISI, an optimum detection technique needs to take the full advantage of the embedded information in each sample to maximize its detection reliability because each sample contains a combined information of the corresponding symbol as well as the part of the other adjacent symbols. The maximum-likelihood sequence detection (MLSD) is an optimum detector which selects a possible sequence of samples with the highest likelihood compared to the received sequence. Partial response signalling schemes fall in the category of signals with ISI which are optimally detected using MLSD.

Although offering an optimal detection technique, a brute-force approach to implement a MLSD decoder can be complex and difficult. Moreover, ideally, the entire sequence of information should have been received before the detection process is commenced which makes this process much more complicated. The Viterbi algorithm is a practical means of implementing an optimum maximum-likelihood detection. This decoding technique was originally developed for convolutional codes and subsequently was applied to ISI channels. The number of computations in the Viterbi algorithm grows linearly with the length of the transmitted sequence and detection process can start immediately upon receipt of the first sample.

The idea behind the Viterbi detection technique is to set up a trellis diagram based on the number of coding states and search for a path in this diagram whose coded sequence differs from the received sequence in the fewest number of places. As an example, Fig. 2.6 represents a two-state trellis diagram in which  $b_{ji}(k)$  denotes the branch metric from the state j to i at time k and  $m_i(k)$  denotes the state metric for the state i at time k. Branch metrics in this diagram measure the amount of error between the expected value and the received value at each transition. The state metric for each state at time k presents the least accumulated branch metrics extended from the origin to that specific state. As illustrated in this figure, at time k=5, state 1 has obtained the smallest accumulated metric and the solid-line branches which have kept track of this state from the origin are exploited to recover the received information. The maximum number of states in an M-ary input signal and in a partial response signalling scheme depicted in Fig. 2.3 is equal to  $M^{N-1}$  and the number of branches initiating from or ending to each state can be up to M.

Fig. 2.6: A typical two-state trellis diagram

In practice, the transmission channel characteristics do not precisely match a PRS channel and the output performance degrades as a result of this improper channel. For example in read channels, peak-up head positions and hence channel specifications are prone to variation due to assembling tolerance and weariness. As a result, adaptive equalizers at the input of the Viterbi or other detector at the receiver side are usually employed to compensate for these imperfections and adjust the channel to a desired behavior (Fig. 2.7).

Fig. 2.7: A typical transceiver with adaptive equalizers at the front of the detector

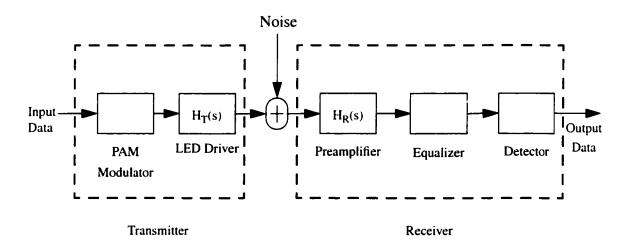

#### 2.1.4 Analog Viterbi Detectors

Although digital Viterbi detectors are often employed as digital signal processing in systems such as optical and magnetic recording channels, digital mobile radios and digital satellite TVs, it is of interest to exploit some advantages of analog circuits in these decoders. In modest-size process technologies, analog circuits offer better speed and power consumption and applying them to some applications such as recording channels and optical links can achieve a great amount of saving in power and boosting in speed. Even with the shrinkage of process technologies toward deep sub-micron sizes and the unmatched improvement of speed and power consumption in digital circuitry, A/Ds at the front-end of digital Viterbi detectors as shown in Fig. 2.8, still remain as a bottleneck in high-speed and low-power applications. The most recent papers on the design of 6-bit A/Ds [12] and [13],

report a power dissipation of about 400mW at 500MS/s and 225mW at 300MS/s with 3.3V power supply, respectively. Moreover, the power required by digital Viterbi detectors as reported in [14] and [15] are about 22mW/state at 110MS/s with 3.0V power supply. These information lead us to an estimated power consumption of about 800mW at 500 MS/s and 465 mW at 300 MS/s for a 4-state digital Viterbi detector and the required A/D. In comparison, as will be shown in chapter 5, the power dissipation of an equivalent analog Viterbi detector is experimentally measured to be 55mW at 100MS/s and is expected to be about 112 mW at 500 MS/s by simulation. Even with considering 20% more power for the path memory which was not included in the designed chip, calculations simply show at least five times power reduction in the analog version.

Fig. 2.8: The receiver architecture in the presence of digital Viterbi detector

Analog Viterbi detectors obtain their greatest benefit when used with other moderate-precision applications such as equalizers and PLLs, as illustrated in Fig. 2.9, and where the A/D can be eliminated from the front end of the receiver.

Fig. 2.9: The receiver architecture in the presence of analog Viterbi detector.

A design of analog Viterbi detector for class-IV partial response signalling was presented in [16]. This detector operated at a speed of 40 Mb/s while consuming 50 mW/state. This design was improved with a modified architecture in [17] to achieve a speed of 200 Mb/s with a reduced power dissipation of 15 mW/state. Other low-power designs [18] have reached a power consumption of about 4 mW/state at a speed of 100 Mb/s. In industry, a 72 Mb/s PRML disk-drive chip with an analog Viterbi detector was reported [19] and a 100 Mb/s read channel chip by Texas Instruments using analog Viterbi detector (SSI 32P4782A) [30] is presently available. One of the goals of this thesis is to demonstrate that with the use of an analog Viterbi detector, it is possible to achieve digital transmission speeds as high as 1Gb/s in the area of short distance optical wireless communications.

#### 2.2 Optical Wireless Communications

Optical wireless communication systems have achieved considerable market acceptance in recent years. This is primarily due to the significant reduction in optical components price and also their ease of installation and reconfiguration. Other advantages such as no requirement for frequency licensing and higher bandwidth, less vulnerability to interference and the possibility of reusing transceivers in the immediate vicinity make optical wireless in some fields more appealing than its radio frequency (RF) counterpart. In certain applications, the use of optical wireless links extend from personal appliances such as digital cameras, mobile phones and PDAs to PCs and printers and ultimately to optical wireless LANs. Indoor optical wireless systems are subject to stringent safety standards which bound their transmitted power within Class I eye safety under all conditions [20]. Indoor systems that use lasers therefore find it difficult to achieve a good power budget. However, by using LEDs instead of lasers a much higher launch power can be used and still remain in Class I eye safe [21]. Furthermore, to alleviate fine alignment complication between optical transmitters and receivers, photodiodes with large active area are needed which in turn introduce large parasitic depletion capacitors at the receiver front-end. Despite the availability of vast capacity in light communications, the aforementioned issues such as slow LEDs and photodiodes limit its operation up to few tens of MHz. While the emergence of Bluetooth and the other radio systems in the past few years has been presumed as a prevailing alternative to optical links, it is more realistic to consider them as two complementary media. Table 2.1 [21] summarizes some relevant radio and optical systems for comparison. As shown in this table, radio systems cover a larger distance whereas optical wireless links are more suitable for short distance communications. In the other words, while RF signals can cover the longer ranges between the buildings and penetrate through some opaque obstacles, wireless optical signals in contrast, are able to serve multiple users in the proximity of each other within the same building with higher throughputs. This calls for a challenging design of more sophisticated modules in an optical wireless communication system especially in the receiver side to perform at higher bit rates using low cost technologies. The scope of this chapter is to introduce a typical optical channel and its elements and put forward some existing challenges and their potential solutions to achieve higher speed.

Table 2.1: Specification for some optical wireless and RF systems

| Medium              | System    | Speed<br>(Mb/s) | Range<br>(m) |

|---------------------|-----------|-----------------|--------------|

| Optical<br>Wireless | JVC       | 10              | 10           |

|                     | Spectrix  | 4               | 10           |

|                     | IrDA      | 4               | I            |

|                     |           |                 |              |

| Radio               | WaveLAN   | 8               | 100          |

|                     | HiperLAN  | 26              | 50           |

|                     | Bluctooth | ī               | 10           |

After introducing a typical optical link in this section, different modulation schemes and noise in optical communications will be investigated. Preamplifiers followed by equalizers and detectors are then discussed.

#### 2.2.1 Optical Link

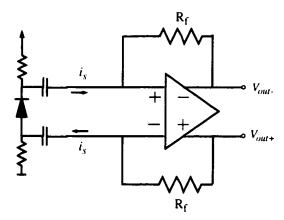

Fig. 2.10 illustrates a typical infrared link.

Fig. 2.10: A typical optical wireless transceiver system

After coding and modulating the input data in the transmitter side, LED and its driver translate the input signal to the infrared light. The optical power generated in this way is proportional to the LED current and is measured by W/Steradian. In the receiver side, the photodiode also generates a current proportional to the received optical power. The resulting signal to noise ratio is proportional to the square of the received optical power which attenuates by the square of the distance and hence poses a significant limitation on the range of this type of link. The generated current in the receiver is then amplified by a preamplifier before being equalized to a desired spectral shape for detection. The detector recovers the received data using the equalized signal and the input clock generated by the clock recovery circuit.

Opto-electronic components suitable for optical wireless data communications are the major limiting factors in achieving higher speed. Available LEDs with reasonable cost have a minimum rise and fall time of 1-1.5ns (MITEL 1A301 High-Performance LED) which impose a limitation of about 300 MHz switching speed for the transmitter. In the receiver side, to alleviate the need for a sharp alignment of the photodiode (as is done in fiber optics using costly lenses), photodiodes with a wide field of view (FOV) are used which introduce a large depletion capacitance at the input of transimpedance amplifier. Typical photodiodes present a capacitance of about 5pF at  $V_R = 0V$  (HEWLETT PACKARD HSDL-5400) which normally, along with the input impedance of the preamplifier, in-

troduce the dominant pole of the receiver.

#### 2.2.2 Modulation Schemes

Two popular intensity modulation schemes widely used in optical communications are L-PPM (L-level pulse-position modulation) and L-PAM (L-level pulse amplitude modulation). In L-PPM, the input bits with rate  $R_b$  are grouped in packages of  $log_2L$  bits as a symbol and at each period one of these symbols is chosen to transmit. In this modulation, each symbol period T is divided into L sub-intervals which each of them is allocated to one of the L different symbols. In L-PAM, the same number of symbols are translated to L different levels and at each period, one of these levels is sent. In contrast to L-PPM, L-PAM is more bandwidth efficient as the number of conveyed bits increase with the number of levels with the same symbol-rate. On the other hand, L\_PPM is more power efficient as it disperses L different symbols temporally rather than in amplitude. In Table 2.2, the power and bandwidth requirements of these two modulation schemes are compared [22]. In this table, for a given noise power and  $R_h$ , power requirement is compared with that of an on-off keying modulation (2-PAM) scheme denoted by  $P_{ook}$ . It is apparent from Table 2.2 that in limited bandwidth channels with a high bit rate, multi-level PAMs are the best choice. Moreover, as opposed to PPM, PAM is a linear modulation scheme and hence well-known and classical equalization and detection techniques can be applied.

Table 2.2: Optical power and bandwidth requirements for some intensity modulation schemes

| Modulation<br>Scheme | Average Optical Power<br>Requirement           | Bandwidth<br>Requirement |

|----------------------|------------------------------------------------|--------------------------|

| OOK (2-PAM)          | P <sub>ook</sub>                               | $R_b$                    |

| L-PAM                | $\frac{L-1}{\sqrt{\log_2 L}} P_{ooK}$          | $\frac{R_b}{\log_2 L}$   |

| L-PPM                | $\frac{1}{\sqrt{0.5L \cdot \log_2 L}} P_{ook}$ | $\frac{LR_b}{\log_2 L}$  |

#### **2.2.3** Noise

Two primary sources of noise at the optical receiver front-end are thermal and shot noise. Thermal noise sources are due to resistive elements and transistors in the preamplifier. Feedback resistors as well as other resistors such as pull-up and pull-down resistors are the main contributors to thermal noise. This noise is generated independently of the received signal and can be modeled as a Gaussian distribution. On the other hand, shot noise is the major source of noise in wireless optical links in the presence of ambient light. This noise has a white spectrum with a normalized noise power density given by

$$\overline{I_{n,sh}^2} = 2qI_s \qquad A^2/Hz \qquad (2.1)$$

where  $I_s$  is the dc component of the input signal and q is a unit electron charge equal to  $1.6 \times 10^{-19}$  C. Sunlight, incandescent light bulbs and fluorescent lamps are the principal sources of dc component of the optical signal.

#### 2.2.4 Preamplifiers

High bandwidth, low input referred noise, and wide dynamic range are the three prominent specifications for an optical preamplifier. Three principal configurations for optical preamplifiers are depicted in Fig. 2.11. In circuits a and b, photodiodes have been placed in series with the load resistor. In the former circuit,  $R_L$  is low and hence, the overall bandwidth is high as it is determined by the inverse product of  $R_L$  and  $C_{pd}$ . But, on the other hand, the input thermal current noise, mainly generated by the load resistor, is proportional to  $1/R_L$  and hence, this circuit suffers from high input referred noise. The same circuit but with a high load resistor shown in Fig. 2.11.b presents better noise performance at the expense of lower bandwidth. To compensate for their bandwidth shortage, these types of circuits are followed by equalizers. When it comes to bandwidth and noise compromise, the circuit shown in Fig. 2.11.c, or a transimpedance amplifier (TIA) becomes the best choice. In this circuit,  $R_f$  performs as a shunt-shunt feedback and can be set as large as possible (as long as stability is sustained) while still presenting a small input impedance.

Fig. 2.11: Three optical preamplifier structures, a: low input impedance, b: high input impedance, c: transimpedance amplifier

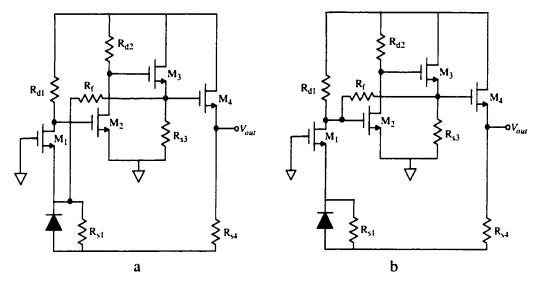

Two major candidate topologies for TIAs are common-source and common-gate. Shown in Fig. 2.12, two common-source architectures differ in the type of feedback connection [23].

Fig. 2.12: Common-source transimpedance amplifiers

In both circuits, the input referred noise is equal to

$$\overline{I^{2}_{n, in}} = \frac{4kT}{R_{f}} + \frac{\overline{V^{2}_{n, A}}}{R_{f}^{2}}.$$

(2.2)

where  $R_f$  is the feedback resistor and  $V_{n,A}$  denotes the input-referred noise voltage of the open-loop amplifier. Also, the -3dB bandwidth for the above circuits are equal to  $(2\pi)A/(R_fC_{pd})$  where Cpd is the depletion capacitance of the photodiodes and A is the open-loop gain. The circuit of Fig. 2.12.a suffers from the small headroom for  $R_B$  which is defined by  $V_{gsI}+V_{gs2}$  and makes  $R_B$  unavoidably small. This impacts both noise performance and bandwidth as it reduces the open-loop gain. Furthermore, the three poles at the input node, the drain of  $M_I$ , and the output node degrade the phase margin and hence the stability. In Fig. 2.12.b, the  $R_f$  connection node is relocated to the drain of  $M_I$  and so the output capacitance is isolated from the feedback resistor. This modification leaves greater voltage drop across  $R_B$  and the circuit has better noise and bandwidth characteristics.

Two common-gate topologies are depicted in Fig. 2.13 [24]. Due to the lower input impedance of common-gate transistors, the depletion capacitance of photodiodes are isolated from determining the dominant pole. In both circuits, the input referred noise in low frequencies can be approximated by

$$\overline{I^{2}_{n, in}} = \frac{4KT}{R_{s1}} + \frac{4KT}{R_{d1}} + \frac{4KT}{R_{f}}$$

(2.3)

and the dominant pole is determined by the input capacitance of  $M_2$ , the gate and drain capacitance of  $M_1$  and the feedback resistor  $R_f$ . In the circuit shown in Fig. 2.13.b, the feedback resistor connects the output to the drain of  $M_1$  rather than its source as in Fig. 2.13.a. This provides a complete isolation of non-dominant poles from the photodiode capacitance and hence a better frequency performance. Furthermore, since a shunt feedback is applied to the gate of  $M_2$  in Fig. 2.13.b, the input impedance at this node is low and the effect of  $R_{d1}$  in  $f_{-3dB}$  is negligible which implies that this resistor can be made larger in this upgraded design for lower input referred noise and higher open-loop gain.

Fig. 2.13: Common-gate transimpedance amplifiers

An improved version of common-gate TIAs (as shown in Fig. 2.14) employs a regulated cascode (RGC) circuit at the input to improve the input impedance for better frequency and noise performance [25]. An extra shunt feedback at the input provided by  $M_B$ , lowers the input impedance by a factor of  $(1+g_{mB}R_B)$  and so the input impedance will be equal to

$$R_{in} = \frac{1}{g_{m1}(1 + g_{mB}R_B)} \tag{2.4}$$

This configuration will be addressed in more detail in chapter 3.

Fig. 2.14: Common-gate transimpedance amplifiers with RGC circuit

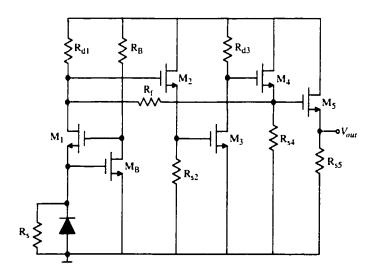

Fully-differential circuits have proven their efficiency in reducing common-mode noise injections. Transimpedance amplifiers with fully differential architectures have also been proposed in the literature. A capacitive coupled TIA illustrated in Fig. 2.15 and proposed by [26] and [27] employs two coupling capacitors to block dc current. The disadvantages of this type of topology are the complexity of layout with on-chip coupling capacitors as well as the photodiode biasing fluctuation as a result of the ambient light variation. The other fully-differential TIAs such as those proposed in [28] and [29] sense the photodiode current single-endedly at one of the inputs and use a current source or a capacitor at the other input for matching purposes. Some practical non-idealities such as process variations and temperature, prevent these circuits from being well balanced and their performance deteriorates with these imperfections. DC photocurrent induced by the ambient light can also be problematic in such dc-coupled structures as the intensity of this light can be orders of magnitude higher than that of the signal light. Inclusion of dc rejection circuits can prevent the preamplifier saturation due to background light.

Fig. 2.15: AC-coupled fully differential transimpedance amplifier

In chapter 3, a new fully differential dc-coupled transimpedance amplifier with dc photocurrent rejection circuit will be discussed.

### 2.3 Application of Modulation and Detection Techniques in Optical Wireless Communications

With the advent of high-speed optical data communications and despite the existence of a rather unlimited bandwidth in optical media, band limitation of opto-electronic components and storage devices such as CDs and DVDs call for a sophisticated method for channel equalization and detection. In short-distance wireless optical communications, the main goal is to design a low-cost transceiver with the capability of handling high data bit rates as high as 1Gb/s. Having achieved this speed, even the connections to the monitors can be operated optically and multi-user networks can benefit from it. Based on the experimental results using the existing regular LEDs and photodiodes, a typical two-pole transmitter with the poles at 250 and 400MHz and a transimpedance amplifier with two poles located at 250 MHz and 400 MHz are readily achievable. A channel model for this type of link is shown in Fig. 2.16 in which H<sub>T</sub>(s) and H<sub>R</sub>(S) represent the LED driver and the receiver preamplifier transfer function.

Fig. 2.16: A typical optical transceiver model

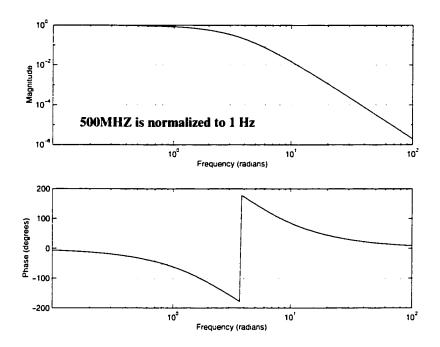

The aggregate frequency response for the introduced typical channel is depicted in Fig. 2.17 and shows that the -3dB bandwidth is about 145MHz.

Fig. 2.17: Frequency response of the optical channel without equalization

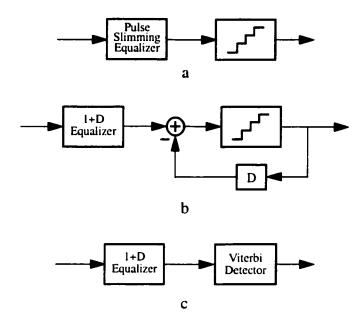

Three methods are shown in Fig. 2.18 to equalize this low-pass channel. In the first method, a pulse slimming equalizer is used to convert the existing channel to a raised-co-sine equivalent with 100% excess bandwidth before proceeding to the peak detection process. In the second method, the channel is equalized to a 1+D partial response channel and then a DFE has been exploited to detect the received data. In the last method and with the same equalization as the second method, a Viterbi detector has been deployed to extract the received information.

Fig. 2.18: Detection techniques, a: peak detection, b: DFE, c: Viterbi decoder

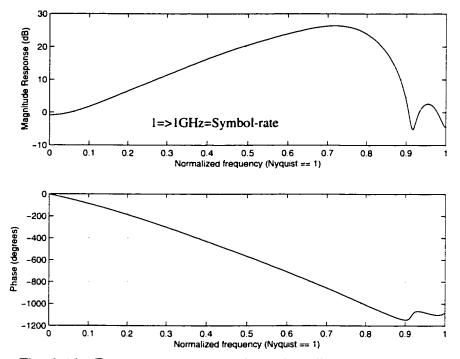

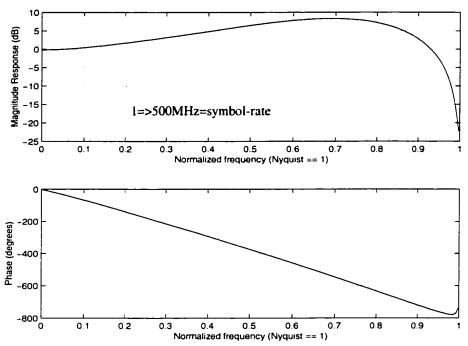

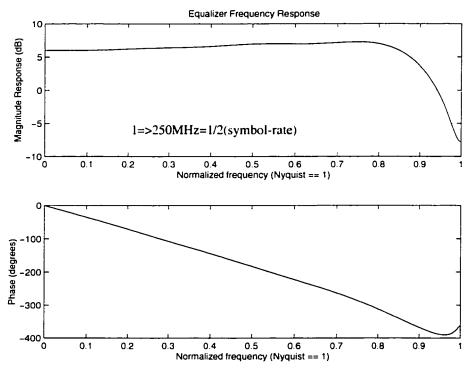

Using a 10-Tap FIR filter as the equalizer and SIMULINK as the simulator, the filter coefficients of the desired equalizers for the existing channel were defined. After fixing the filter coefficients for each channel, the symbol error rate (SER) was evaluated for performance comparison. In Fig. 2.19, the frequency response of the pulse slimming equalizer for a 2-PAM modulation scheme with a bit-rate of 1Gb/s has been depicted. The same characteristic but for a 1+D equalizer is shown in Fig. 2.20. Since in the pulse slimming equalization, the required channel bandwidth is equal to the symbol-rate (1GHz), higher frequencies in this low-pass channel have been drastically boosted. This type of equalization also enhances in-band noise power which consequently impacts SER performance. In 1+D equalization, the required bandwidth is half the symbol-rate (500MHz) and hence the required high frequency boosting and noise enhancement are less than those of the earlier equalizer.

Fig. 2.19: Frequency response for pulse slimming equalizer (symbol-rate=1GHz)

Fig. 2.20: Frequency response for 1+D equalizer (symbol-rate=1GHz)

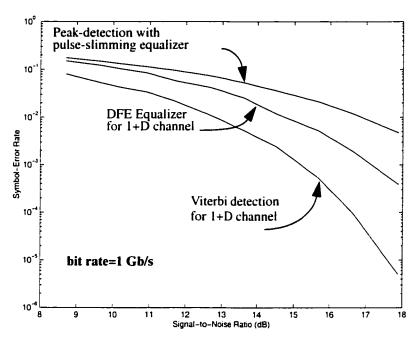

Shown in Fig. 2.21, SER performance of the three detection techniques have been compared. This figure reveals at least 4dB and 2dB better performance of the Viterbi detection over the peak and DFE detection techniques, respectively.

Fig. 2.21: BER versus SNR for different detection techniques in 2-PAM scheme

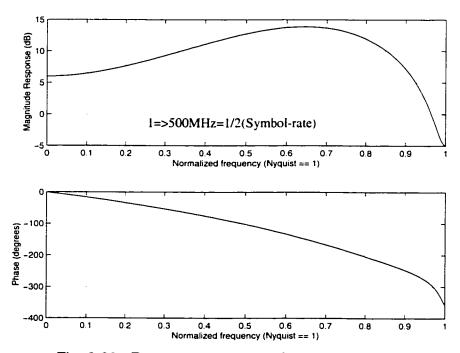

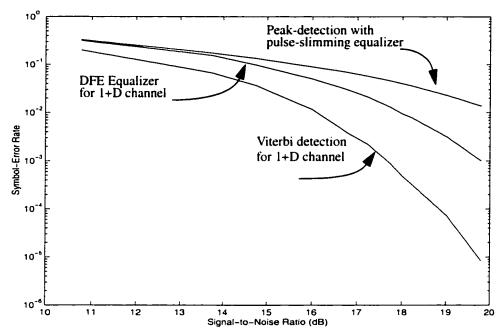

To avoid the use of high boost equalizers in Figs. 2.19 and 2.20 and also their significant noise enhancement, it was decided to investigate 4-PAM signalling to reduce the required bandwidth and equalization complexity. Each symbol in 4-PAM conveys two bits of information and hence with the same bit rate, the symbol rate will be halved. Figs. 2.22 and 2.23 illustrate the frequency characteristics of pulse slimming and 1+D equalizers, respectively. While still more than 8dB amplification variation in pulse slimming equalizer is required, a simple low-pass filter seems adequate for 1+D equalization. Fig. 2.24 shows the SER performance of three detection methods in 4-PAM scheme. With nearly the same performance as 2-PAM, the Viterbi detection outperforms peak detection and DFE SER performance by 4 and 2dB. This indicates that to achieve a speed of 1Gb/s data transmission over wireless optical links, 4-PAM can provide a viable environment to implement simple equalization and the Viterbi detection can be employed for superior performance.

Fig. 2.22: Frequency response for pulse slimming equalizer (symbol-rate=500MHz)

Fig. 2.23: Frequency response for 1+D equalizer (symbol-rate=500MHz)

Fig. 2.24: SER versus SNR for different detection techniques using 4-PAM scheme

#### 2.4 Summary

Intersymbol interference is an unavoidable perturbation in the bandwidth constrained channels. Partial-response signalling systems intentionally introduce controlled amount of ISI to spectrally push the signal toward the minimum bandwidth of the Nyquist rate. However, this requires more complexity in the receiver to extract the original data.

The task of decoding the received signal in a partial response signalling scheme is to remove the existing ISI from the original information. Symbol-by-symbol techniques such as DFE and precode/slicer techniques are straight-forward. However, they ignore the informative content of the ISI due to the adjacent samples. As such, their SNR performance fall about 3dB below the optimum maximum-likelihood sequence detectors.

The Viterbi algorithm is a practical and efficient tool to realize optimum MLSD decod-

ers. Their optimal performance stems from the fact that their detection criterion is based on the sequence of information rather than individual samples and hence take the most of information embedded in ISI.

Analog Viterbi detectors outperform their digital counterpart in lower power consumption as they eliminate the power-hungry A/D from the front-end of the receiver. Storage channels and short distance optical wireless systems are the appropriate applications to incorporate analog Viterbi detectors as they demonstrate fairly simple channels modeled by PRS coding polynomials and their required equalizers can be implemented in analog.

An optical wireless channel is more suitable for short distance data communications where multi-user LANs and computer-based systems can benefit from it without any problems of wiring and cabling. LEDs and photodiodes with large field of view are the bandwidth limitation bottlenecks in optical wireless as they impose significant delay in data exchange. Common-gate input transistors can be employed in transimpedance amplifiers to isolate the photodiode capacitors from the rest of the circuit and hence improve the bandwidth.

4-PAM modulation scheme can provide a practical means of establishing a high-speed data communications as it requires less channel bandwidth. Moreover, partial response signalling with less bandwidth requirements make equalization more viable and efficient. Finally, in the introduced optical channel it was shown that the Viterbi detector performs superior to the other detection techniques such as peak detection and DFE by at least 2dB.

#### 2.5 References

- [1]J. Taylor, DVD Demystified, McGraw Hill, 1998.

- [2] R. K. Jurgen, Digital Consumer Electronics Handbook, McGraw Hill, 1996.

- [3]J. G. Proakis and M. Salehi, "Communication Systems Engineering," *Prentice Hall*, 1994.

- [4] A. Lender, "The duobinary technique for high-speed data transmission," *IEEE Trans. Commun. Electron.*, Vol. 82, May 1963, pp. 214-218.

- [5]E. R. Kretzmer, "Generalization of a Technique for Binary Data Communication," *IEEE Trans. on commun. Technol.*, Vol. 14, No. 1, Feb. 1966.

- [6]J. M. B. Correia and A. V. T. Cartaxo, "Duobinary coding for 20 Gbit/s intensity modulated direct detection optical fiber transmission," *SPIE Proc. All-Optical Commun. Systems*, Vol. 3230, Nov. 1997, pp. 92-103.

- [7]C. H. Lee and Y. S. Cho, "A PRML Detector for a DVDR Systems," *IEEE Trans. Consumer Electronics*, Vol. 45, No. 2, May 1999, pp. 278-285.

- [8]S. H. Choi, J. J. Kong, B. G. Chung, Y. H. Kim, "Viterbi Detector Architecture for High-Speed optical Storage," *IEEE TENCON Proc. Speech and Image Technologies for Computing and Telecommunications*, Vol. 1, 1997, pp. 89-92.

- [9]P. Kabal and S. Pasupathy, "Partial-Response Signaling," *IEEE Trans. Commun.*, Vol. 23, No. 9, Sep. 1975, pp. 921-934.

- [10]H. Kobayashi, D. T. Tang, "Application of partial-response channel coding to magnetic recording systems," *IBM Journal of Research and Development*, July 1970, pp. 368-375.

- [11]J. G. Proakis, Digital Communications, McGraw Hill, 1995.

- [12]Y. Tamba, K. Yamakido, "A CMOS 6b 500MSample/s ADC for a Hard Disk Drive Read Channel," *ISSCC Dig. Tech. Papers*, Feb. 1999, pp. 324-325.

- [13]I. Mehr, D. Dalton, "A 500-MSample/s, 6-Bit Nyquist-Rate ADC for Disk-Drive Read-Channel Applications," *IEEE J. Solid-State Circuits*, Vol. 34, No. 7, July 1999, pp. 912-920.

- [14]S. Sridharan and L. R. Carley, "A 110 MHz 350mW 0.6µ CMOS 16-State Generalized-Target Viterbi detector for Disk Drive Read Channels," *IEEE J. Solid-State Circuits*, Vol. 35, No. 3, March 2000.

- [15]L. R. Carley and S. Sridharan, "A pipelined 16-State Generalized Viterbi Detector," IEEE Trans. Magnetics, Vol. 34, No. 1, Jan. 1998, pp. 181-186.

- [16]T. W. Matthews, R. R. spencer, "An Integrated Analog CMOS Viterbi Detector for

- Digital Magnetic Recording," *IEEE J. Solid-State Circuits*, Vol. 28, No. 12, Dec. 1993, pp. 1294-1302.

- [17]M. H. Shakiba, D. A. Johns and K. W. Martin, "An Integrated 200-MHz 3.3-V BICMOS Class-IV Partial-Response Analog Viterbi Decoder," *IEEE J. Solid-State Circuits*, Vol. 33, No. 1, Jan. 1998, pp. 61-75.

- [18]A. Demosthenous and J. Taylor, "Low-Power CMOS and BICMOS Circuits for Analog Convolutional Decoders," *IEEE Trans. Circuits and Systems-II*, Vol. 46, No. 8, Aug. 1999, pp. 1077-1080.

- [19]R. G. Yamasaki, T. Pan, M. Palmer, D. Browning, "A 72Mb/s PRML Disk-Drive Channel Chip with an analog Sampled-Data Signal Processor," *ISSCC Dig. Tech. Papers*, Feb. 1994, pp. 278-279.

- [20]IEC825:1993, "Safety of Laser Products. Equipment classification, requirements and users guide."

- [21] David J. Heatley and Ian Neild, "Optical Wireless the promise and the reality," *IEE Colloquium on Optical Wireless Communications*, pp. 1/1-1/6, 1999.

- [22]J.R. Barry, "Wireless Infrared Communications," Kluwer Academic Publishers, Boston, 1994.

- [23]B. Razavi, "Design of High-Speed Circuits for Optical Communication Systems," *IEEE Proc. CICC*, pp. 315-322, May 2001.

- [24]S.M. Park and C. Toumazou, "Gigahertz Low Noise CMOS Transimpedance Amplifier," *IEEE Proc. ISCAS*, pp. 209-212, June 1997.

- [25]S.M. Park and C. Toumazou, "Low Noise Current-Mode CMOS Transimpedance Amplifier for Giga-Bit Optical Communication," *IEEE Proc. ISCAS*, Vol. 1, pp. 293-296, June 1998.

- [26]T. Ruotsalainen, P. Palojarvi, and J. Kostamovaara, "A Current-Mode Gain-Control Scheme with Constant Bandwidth Delay for a Transimpedance Preamplifier," *IEEE J. Solid-State Circuits*, Vol. 34, No. 2, pp. 253-258, February 1999.

- [27]M. B. Ritter, F. Gfeller, W. Hirt, D. Rogers, S. Gowda, "Circuit and System Challenges in IR Wireless Communication," *Proc. ISSCC*, pp. 398-399, February 1996.

- [28]K. Phang and D.A. Johns, "A CMOS Optical Preamplifier for Wireless Infrared Communications," *IEEE Trans. Circuits and Systems-II: Analog and Digital Signal Processing*, Vol. 46, No. 7, pp. 852-859, July 1999.

- [29]R. Coppoolse, J. Verbeke, P. Lambrecht, J. Codenie, and J. Vandewege, "Comparison of a Bipolar and a CMOS Front End in Broadband Optical Transimpedance Amplifiers," *Proc. 38th Midwest Symp. on Cir. and Sys.*, pp. 1026-1029, Aug. 1996.

- [30]www.ti.com

#### **CHAPTER**

## 3

# Fully Differential DC-Coupled Transimpedance Amplifier

High-speed free-space optical receivers require a transimpedance amplifier (TIA) at their front-end to accommodate photodiodes with a wide field of view and hence a large depletion capacitance (1-10pF). Despite this significant capacitive node at the input, the desired TIAs should still provide wide bandwidth, high gain, and good sensitivity. These receivers find their application in laptop computers, personal digital assistants (PDAs), digital cameras and many other equipment supplied with a short distance infrared communication port. CMOS is the preferred technology for its low cost and ease of integration. However, building single-chip optical receivers in CMOS technology is challenging because of low supply voltages, small transistor transconductances, and large substrate noise making it difficult to achieve high bandwidth and good sensitivity. In wireless optical communications, TIAs also encounter ambient light perturbation. Intense background light can reduce output swing or even saturate the front-end preamplifiers.

Different architectures have been proposed to improve the sensitivity at the input of the transimpedance amplifiers. Reported designs in [1], [3] and [7] have introduced a fully dif-