# ARCHITECTURE ALTERNATIVES FOR TIME-INTERLEAVED AND INPUT-FEEDFORWARD DELTA-SIGMA MODULATORS

by

Ahmed Gharbiya

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy Graduate Department of Electrical and Computer Engineering University of Toronto

© Copyright by Ahmed Gharbiya 2008

## Architecture Alternatives for Time-Interleaved and Input-Feedforward Delta-Sigma Modulators

Ahmed Gharbiya

Doctor of Philosophy Department of Electrical and Computer Engineering University of Toronto 2008

### Abstract

This thesis provides architecture alternatives for delta-sigma modulators in two areas: high-speed operation based on time-interleaving and low-voltage environment by exploiting the input-feedforward concept.

Parallelism based on time-interleaving can be used to increase the speed of delta-sigma modulators. A novel single-path time-interleaved architecture is derived and analyzed. Finite opamp gain and bandwidth result in a mismatch between the noise transfer functions of the internal quantizers which degrades the performance of the new modulator. Two techniques are presented to mitigate the mismatch problem: a hybrid topology where the first stage uses multiple integrators while the rest of the modulator uses a single path of integrators and a digital calibration method.

The input-feedforward technique removes the input-signal component from the internal nodes of delta-sigma modulators. The removal of the signal component reduces the signal swing and distortion requirements for the opamps. These characteristics enable the reliable implementation of delta-sigma modulators in modern CMOS technology. Two implementation issues for modulators with input-feedforward are considered. First, the drawback of the analog adder at the quantizer input is identified and the capacitive input feedforward technique is introduced to eliminate the adder. Second, the double sampled input technique is proposed to remove the critical path generate by the input feedforward path.

Novel input-feedforward delta-sigma architecture is proposed. The new digital input feedforward (DIFF) modulator maintains the low swing and low distortion requirements of the input feedforward technique, it eliminates the analog adder at the quantizer input, and it improves the achievable resolution. To demonstrate these advantages, a configurable delta-sigma modulator which can operate as a feedback topology or in DIFF mode is implemented in 0.18µm CMOS technology. Both modulators operate at 20MHz clock with an oversampling ratio of 8. The power consumption in the DIFF mode is 22mW and in feedback mode is 19mW. However, the DIFF mode achieves a peak SNDR of 73.7dB (77.1dB peak SNR) while the feedback mode achieves a peak SNDR of 64.3dB (65.9dB peak SNR). Therefore, the energy required per conversion step for the DIFF architecture (2.2 pJ/step) is less than half of that required by the feedback architecture (5.7 pJ/step).

### Acknowledgments

First and foremost, I would like to express my gratitude to my advisor Prof. David Johns. Your insight and suggestions were invaluable in every step of the way. Your emphasis on the three pillars of comprehensive research: the detailed theoretical development supported by extensive simulations and explained through intuitive reasoning was instrumental in developing my research skills.

To Prof. Ken Martin, I wish to express my thanks for your advice and suggestions during several years of the joint weekly meetings.

I would like to thank the members of my Ph.D. supervising committee, Prof. Sorin P. Voinigescu, Prof. Tony Chan Carusone, and Prof. Frank R. Kschischang for their input and feedback. I would like to express my thanks to Prof. Gordon Roberts (McGill University) for his interest in my research and for joining my Ph.D. examination committee.

I am grateful to the professors at Simon Fraser University for their guidance, kindness, and the opportunities they offered me. In particular, I would like to thank my master's thesis advisor Prof. Marek Syrzycki and Prof. Ash M. Parameswaran for their technical knowledge and friendship.

To Prof. Mo El-Hawary (Dalhousie University), thank you for inspiring and encouraging me to pursue my graduate studies. I appreciate that you have always been there for me throughout my academic career.

I wish to thank the supporting staff at the Department of Electrical and Computer Engineering at the University of Toronto for all the help and support.

I would like to thank current and former members of the electronics group at the University of Toronto. For their technical insight and friendship, I would like to thank Dr. Anas Hamoui, Mohamed Abdulla, Trevor Caldwell, Stephen Liu, Kentaro Yamamoto, Samir Parikh, Pradip Thachile, Imran Ahmed, Robert Wang, Dave Alldred, Babak Javid, Afshin Haftbaradaran, Mohammad Hajirostam, and Bupesh Pandita. I have also been fortunate to have enjoyed the friendship of Oleksiy Tyshchenko, Masum Hossain, Kevin Banovic, Joseph Aziz, Bert Leesti, Akram Nafee, Nasim nikkhoo, and Jeff Chow.

Words can never express my gratitude to my parents for their infinite support and unlimited love. To them, I owe all. I thank my sister and her family for putting a smile on my face and bringing happiness to my heart. Finally, to taw'am rouhy, my brother and best friend, thank you for your encouragement and advice.

# **Table of Contents**

| ABSTRACT                                                                            | II  |

|-------------------------------------------------------------------------------------|-----|

| ACKNOWLEDGMENTS                                                                     | IV  |

| TABLE OF CONTENTS                                                                   | VI  |

| LIST OF FIGURES                                                                     | IX  |

| LIST OF TABLES                                                                      | XIV |

| LIST OF ABBREVIATIONS                                                               | XV  |

| CHAPTER 1: INTRODUCTION                                                             | 1   |

| 1.1 Motivation                                                                      | 1   |

| 1.2 Thesis Outline                                                                  | 2   |

| Chapter 2: Fundamentals of $\Delta\Sigma$ Modulators                                | 4   |

| 2.1 Single Loop $\Delta\Sigma$ Modulators                                           | 4   |

| 2.1.1 Feedback $\Delta\Sigma$ modulators                                            | 5   |

| 2.1.2 Feedforward $\Delta\Sigma$ modulators                                         | 7   |

| 2.1.3 Feedback $\Delta\Sigma$ modulators with input-feedforward                     | 9   |

| 2.1.4 Feedforward $\Delta\Sigma$ modulators with input-feedforward                  | 11  |

| 2.2 Multistage Noise Shaping Modulators                                             | 12  |

| 2.3 Time-Interleaved $\Delta\Sigma$ Modulators                                      | 14  |

| 2.4 Summary                                                                         |     |

| Appendix A: Modeling Non-Idealities in Switched-Capacitor $\Delta\Sigma$ Modulators |     |

| Chapter 3: Time-Interleaved $\Delta\Sigma$ Modulators                               |     |

| 3.1 Single-Path Time-Interleaved $\Delta\Sigma$ Modulator Concept                   |     |

| 3.2 Effects of Removing the Demux                                                   |     |

| 3.3 Evaluation of the SPTI $\Delta\Sigma$ Modulator                                 |     |

| 3.4 Mixed Multi-Path and Single-Path Time-Interleaved $\Delta\Sigma$ Modulator      |     |

| 3.5 (     | Calibration of the SPTI $\Delta\Sigma$ Modulator                      | 35  |

|-----------|-----------------------------------------------------------------------|-----|

| 3.6 N     | Aismatch Shaping for Multi-Bit DAC in SPTI $\Delta\Sigma$ Modulator   |     |

| 3.7 \$    | Summary                                                               | 40  |

| Appendix  | x A: A Mathematical Approach for the SPTI Derivation                  | 40  |

| CHAPTER 4 | : INPUT-FEEDFORWARD $\Delta\Sigma$ MODULATORS                         | 44  |

| 4.1 I     | nput-Feedforward $\Delta\Sigma$ Modulators                            | 44  |

| 4.1.1     | Input-feedforward timing issues                                       | 45  |

| 4.1.2     | Relaxed timing input-feedforward architecture                         | 48  |

| 4.1.3     | Input-feedforward topologies without the adder at the quantizer input | 50  |

| 4.2 I     | Digital Input-Feedforward $\Delta\Sigma$ Modulators                   | 54  |

| 4.2.1     | Digital input-feedforward $\Delta\Sigma$ modulator concept            | 55  |

| 4.2.2     | Generalized DIFF $\Delta\Sigma$ modulator                             | 57  |

| 4.2.3     | Evaluation of the DIFF $\Delta\Sigma$ Modulator                       | 61  |

| 4.2.4     | Practical Considerations                                              | 64  |

| 4.3 \$    | Summary                                                               | 70  |

| CHAPTER 5 | DESIGN OF THE EXPERIMENTAL MODULATOR                                  | 72  |

| 5.1 \$    | System Level Design                                                   | 72  |

| 5.2 \$    | Structural Level Design                                               |     |

| 5.3 (     | Circuit Level Design                                                  | 82  |

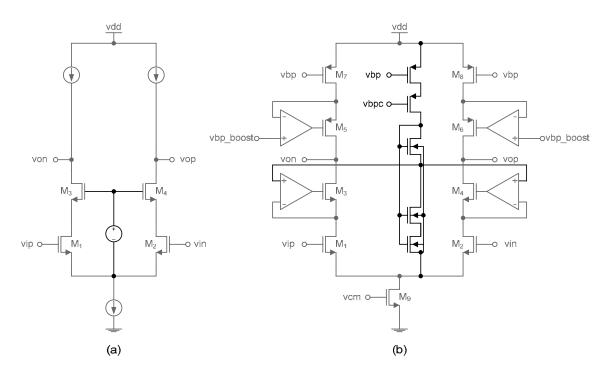

| 5.3.1     | Operational amplifiers                                                | 82  |

| 5.3.2     | Quantizers                                                            | 87  |

| 5.3.3     | Switches                                                              | 90  |

| 5.3.4     | Data weighted averaging                                               |     |

| 5.3.5     | Clock generator                                                       |     |

| 5.3.6     | Simulation Results                                                    |     |

| 5.4 H     | Experimental Results                                                  |     |

| 5.4.1     | Test chip                                                             |     |

| 5.4.2     | Test setup                                                            |     |

| 5.4.3     | Measured performance                                                  | 101 |

| 5.5 \$    | Summary                                                               | 113 |

| CHAPTER 6 | CONCLUSION                                                            | 115 |

| 6.1 \$    | Summary                                                               | 115 |

| 6.2       | Contributions   | 115 |

|-----------|-----------------|-----|

| 6.3       | Future research | 116 |

| Reference | CES             | 118 |

# List of Figures

| Fig. 2.1: Second-order CIFB modulator                                                                  | 5  |

|--------------------------------------------------------------------------------------------------------|----|

| Fig. 2.2: Signal swing at Opamp outputs and sample output spectrum for CIFB                            | 6  |

| Fig. 2.3: Second-order CIFF modulator                                                                  | 7  |

| Fig. 2.4: Signal swing at Opamp outputs and sample output spectrum for CIFF                            | 8  |

| Fig. 2.5: Second-order CIFB-IF modulator                                                               | 9  |

| Fig. 2.6: Signal swing at Opamp outputs and sample output spectrum for CIFB-IF                         | 10 |

| Fig. 2.7: Second-order CIFF-IF modulator                                                               | 11 |

| Fig. 2.8: Signal swing at Opamp outputs and sample output spectrum for CIFF-IF                         | 12 |

| Fig. 2.9: The L-0 multistage modulator                                                                 | 13 |

| Fig. 2.10: H(z) and its blocked version with block length J                                            | 14 |

| Fig. 2.11: Second-order time-interleaved by 2 CIFB $\Delta\Sigma$ modulator                            | 15 |

| Fig. 2.12: Second-order ZITI with J=2 CIFB $\Delta\Sigma$ modulator                                    | 16 |

| Fig. 3.1: MPTI $\Delta\Sigma$ modulator without input demux                                            | 21 |

| Fig. 3.2: (a) MPTI $\Delta\Sigma$ modulator without input demux rearranged (b) with top and bottom pat | hs |

| split                                                                                                  | 22 |

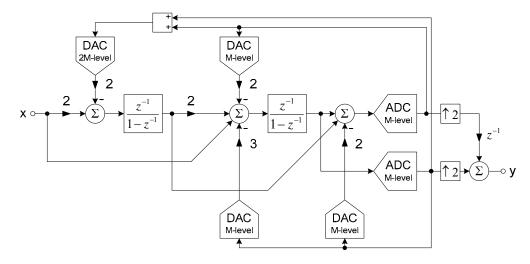

| Fig. 3.3: SPTI $\Delta\Sigma$ modulator with an interleaving factor of 2                               | 22 |

| Fig. 3.4: SPTI $\Delta\Sigma$ modulator with an interleaving factor of 2                               | 23 |

| Fig. 3.5: SPTI $\Delta\Sigma$ modulators with an interleaving factor of 2                              | 24 |

| Fig. 3.6: SPTI $\Delta\Sigma$ modulators with an interleaving factor of 2                              | 25 |

| Fig. 3.7: STF and imaging issue for SPTI                                                               | 26 |

| Fig. 3.8: Sample output spectrum for the SPTI of Fig. 3.3                                              | 27 |

| Fig. 3.9: Second-order SPTI $\Delta\Sigma$ modulator with interleaving factor of 2                     | 28 |

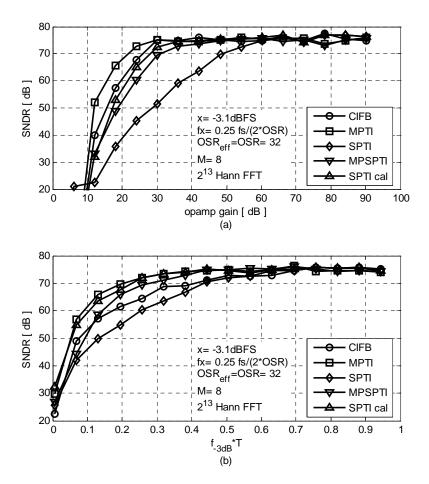

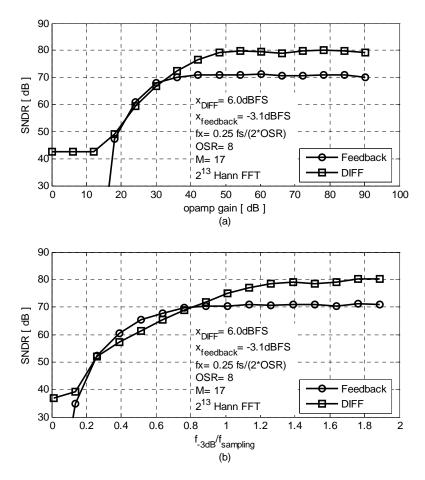

| Fig. 3.10: SNDR versus (a) opamp gain (b) normalized bandwidth                                         | 29 |

| Fig. 3.11: NTFs of the SPTI with gain and phase errors (a) ideal NTF and modified $NTF_1$ (b)          |    |

| ideal NTF and modified $NTF_2$ (c) $NTF_1$ and $NTF_2$ error at low frequencies                        | 30 |

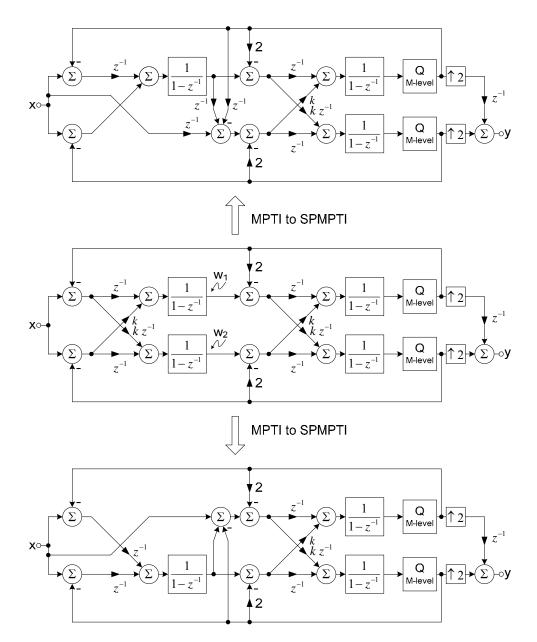

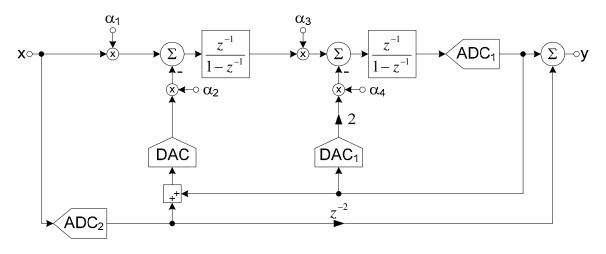

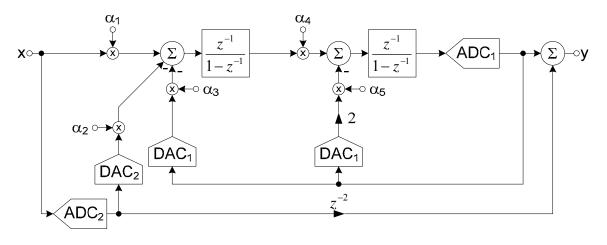

| Fig. 3.1 | 12: MPTI and MPSPTI modulators                                                                       | 32 |

|----------|------------------------------------------------------------------------------------------------------|----|

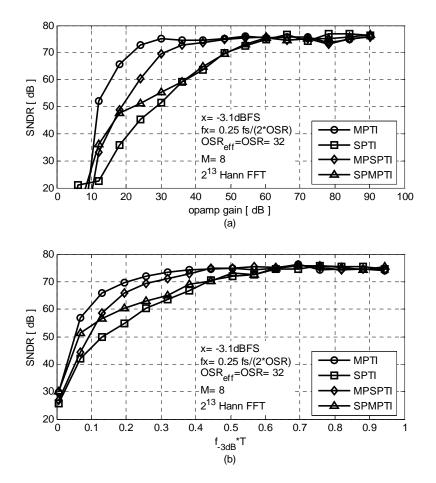

| Fig. 3.1 | 13: SNDR versus (a) opamp gain (b) normalized bandwidth                                              | 33 |

| Fig. 3.1 | 14: MPTI and SPMPTI modulators                                                                       | 34 |

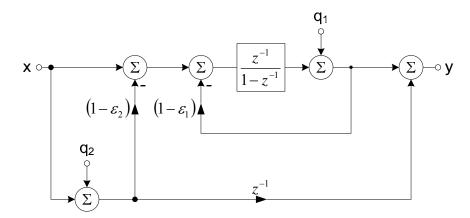

| Fig. 3.1 | 15: SNDR versus (a) opamp gain (b) normalized bandwidth                                              | 35 |

| Fig. 3.1 | 16: SPTI modulator linearized model with gain and phase errors                                       | 36 |

| Fig. 3.1 | 17: SNDR versus (a) opamp gain (b) normalized bandwidth                                              | 37 |

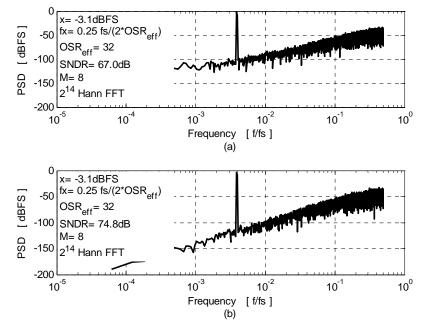

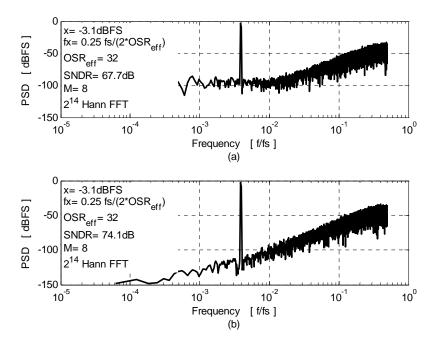

| Fig. 3.1 | 18: Sample output spectrum (a) without calibration (b) with calibration                              | 38 |

| Fig. 3.1 | 19: Sample output spectrum with $\sigma$ =0.5% DAC mismatch (a) two 7-level DWA (b) one 1            | 4- |

|          | level DWA                                                                                            | 39 |

| Fig. 3.2 | 20: SPTI modulator with digital domain addition of the feedback signal in the first                  |    |

|          | integrator                                                                                           | 40 |

| Fig. 4.1 | 1: General input-feedforward $\Delta\Sigma$ modulator                                                | 44 |

| Fig. 4.2 | 2: A first-order switched-capacitor $\Delta\Sigma$ modulator without input-feedforward and its timin | -  |

|          | diagram                                                                                              | 46 |

| Fig. 4.3 | 3: A first-order switched-capacitor $\Delta\Sigma$ modulator with input-feedforward and its timing   |    |

|          | diagram                                                                                              |    |

| -        | 4: Proposed relaxed timing input-feedforward architecture and its timing diagram                     |    |

| -        | 5: Relaxed timing input-feedforward architecture using only the sampling capacitors                  |    |

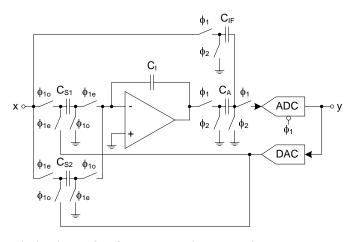

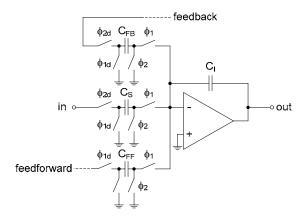

|          | 6: Proposed CIFB-CIF topology                                                                        |    |

| -        | 7: Switched-capacitor implementation of CIFB-CIF                                                     |    |

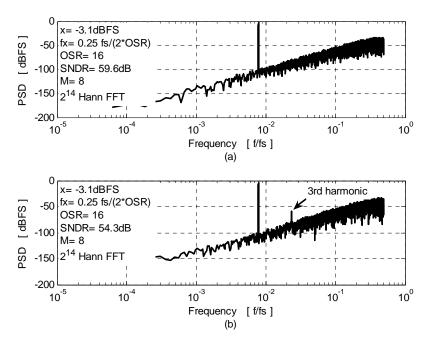

| Fig. 4.8 | 8: Sample output spectrum (a) with input-feedforward (b) without input-feedforward                   | 52 |

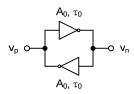

| Fig. 4.9 | 9: Regenerative latch with back-to-back amplifiers of gain $A_0$ and time constant $\tau_0$          | 53 |

| Fig. 4.1 | 10: Proposed CIFF CIF topology                                                                       | 54 |

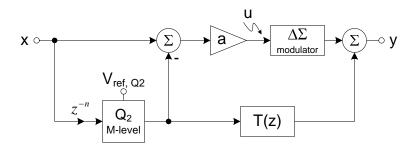

| Fig. 4.1 | 11: Digital input-feedforward $\Delta\Sigma$ modulator                                               | 54 |

| Fig. 4.1 | 12: Mixed-mode input-feedforward $\Delta\Sigma$ modulator                                            | 55 |

| Fig. 4.1 | 13: First-order Digital input-feedforward $\Delta\Sigma$ modulator                                   | 56 |

| Fig. 4.1 | 14: Modified first-order DIFF $\Delta\Sigma$ modulator                                               | 56 |

| Fig. 4.1 | 15: DIFF $\Delta\Sigma$ modulator with the blocks rearranged                                         | 57 |

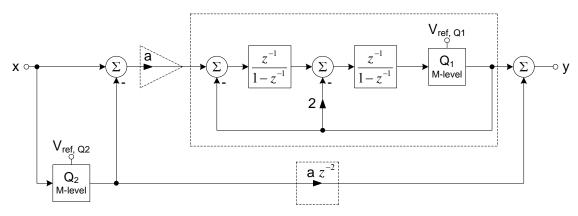

| Fig. 4.1 | 16: Generalized DIFF $\Delta\Sigma$ modulator                                                        | 57 |

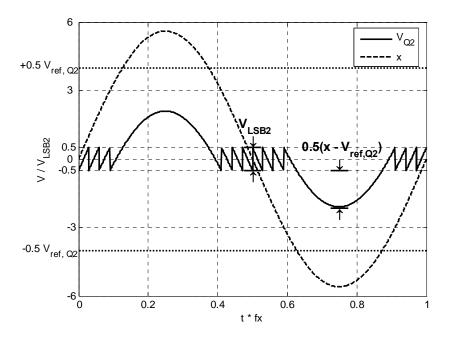

| Fig. 4.1 | 17: Input and output waveforms of the first stage in the DIFF $\Delta\Sigma$ modulator               | 58 |

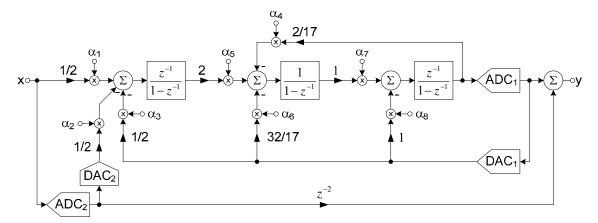

| Fig. 4.1 | 18: Second-order DIFF $\Delta\Sigma$ modulator                                                       | 61 |

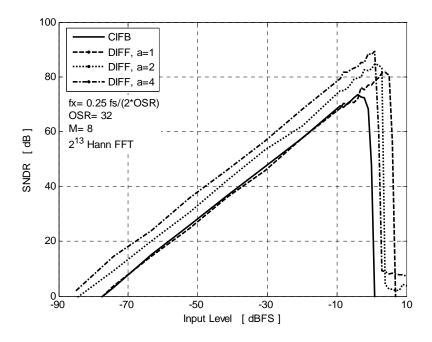

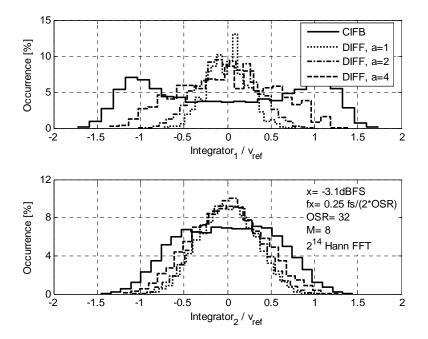

| Fig. 4.19 SNDR versus input-signal amplitude for various inter-stage gains                                      | . 62 |

|-----------------------------------------------------------------------------------------------------------------|------|

| Fig. 4.20: Output probability densities for the first and second integrators with sinusoidal input              | t    |

| and for various inter-stage gains                                                                               | . 63 |

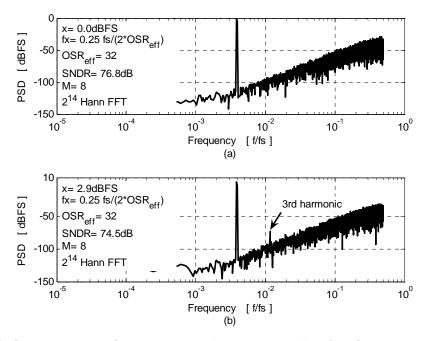

| Fig. 4.21: Output spectrum for second-order $\Delta\Sigma$ modulator (a) before $Q_2$ saturates (b) after $Q_2$ |      |

| saturates                                                                                                       | . 64 |

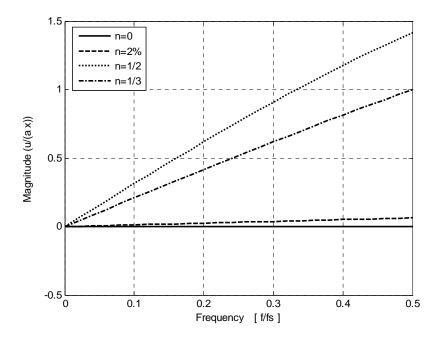

| Fig. 4.22: Generalized DIFF $\Delta\Sigma$ modulator with delay in ADC <sub>2</sub> path                        | . 65 |

| Fig. 4.23: Frequency shaping of the input-signal at the output of first stage for different skew                |      |

| values                                                                                                          | . 66 |

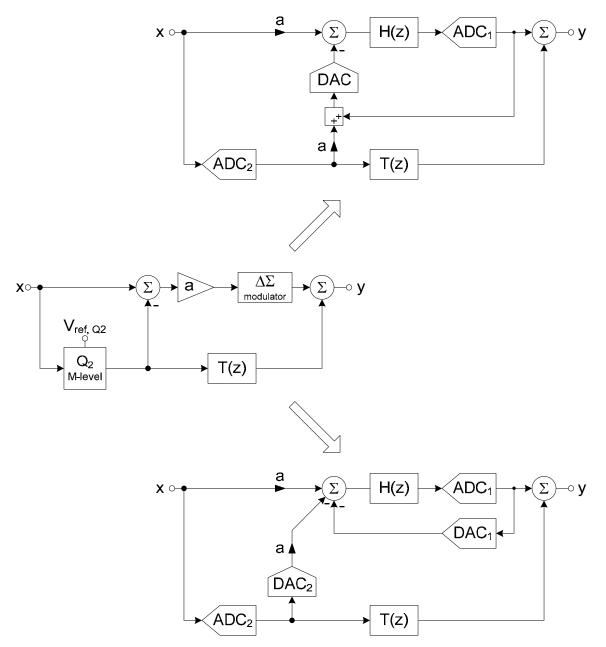

| Fig. 4.24: Generalized DIFF $\Delta\Sigma$ modulator with two possible implementations                          | . 67 |

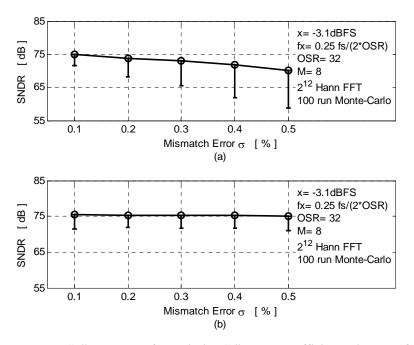

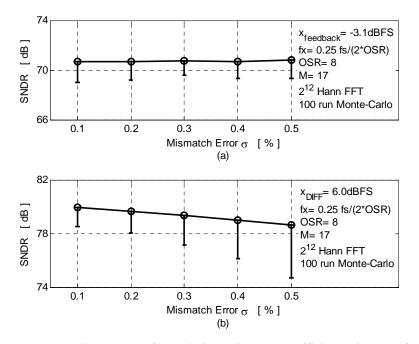

| Fig. 4.25: System level of the $\Delta\Sigma$ modulator for Monte-Carlo simulations (a) digital                 |      |

| implementation (b) analog implementation                                                                        | . 68 |

| Fig. 4.26: SNDR mean "o" and lower $3\sigma$ variation "-" due to coefficient mismatch for a                    |      |

| sinusoidal input (a) analog implementation (b) digital implementation                                           | . 69 |

| Fig. 4.27: Linearized first-order modulator with DAC errors                                                     | . 70 |

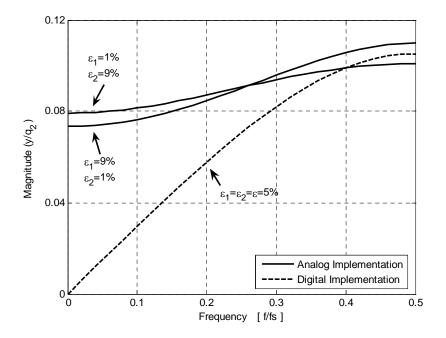

| Fig. 4.28: Magnitude response for the external quantizer with DAC error using analog and dig                    | ital |

| implementations                                                                                                 | . 70 |

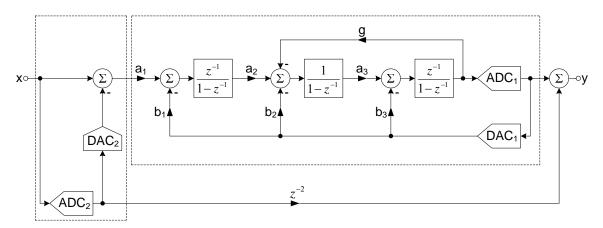

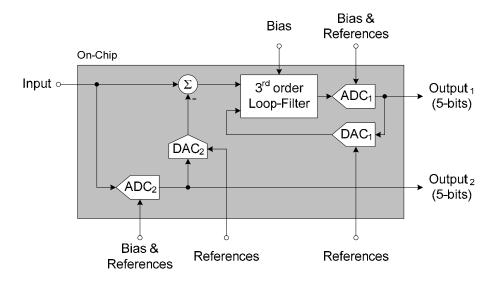

| Fig. 5.1: System level of the experimental $\Delta\Sigma$ modulator                                             | . 73 |

| Fig. 5.2: Block diagram illustrating the parts of the experimental $\Delta\Sigma$ modulator that are            |      |

| implemented on-chip                                                                                             | . 73 |

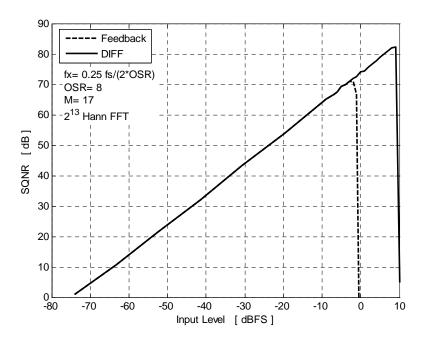

| Fig. 5.3: SQNR versus input-signal amplitude                                                                    | . 75 |

| Fig. 5.4: SNDR versus (a) opamp gain (b) normalized bandwidth                                                   | . 76 |

| Fig. 5.5: System level of the experimental $\Delta\Sigma$ modulator for Monte-Carlo simulations                 | . 77 |

| Fig. 5.6: SNDR mean " $\sigma$ " and lower $3\sigma$ variation "-" due to coefficient mismatch for a sinusoi    | dal  |

| input (a) feedback $\Delta\Sigma$ (b) DIFF $\Delta\Sigma$                                                       | . 77 |

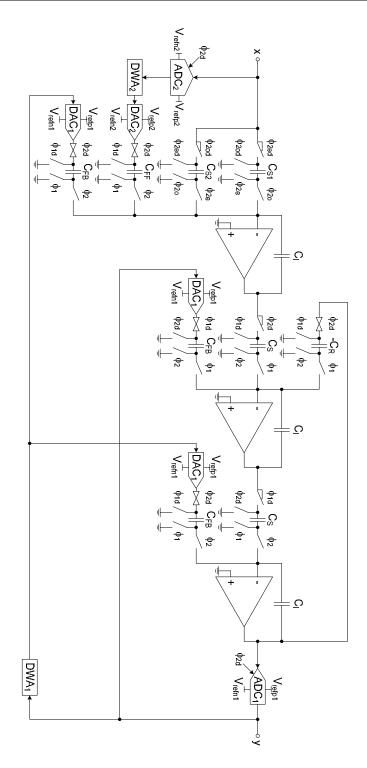

| Fig. 5.7: $\Delta\Sigma$ modulator structural level                                                             | . 79 |

| Fig. 5.8: Input referred noise from a general integrator                                                        | . 81 |

| Fig. 5.9: Telescopic opamp                                                                                      | . 83 |

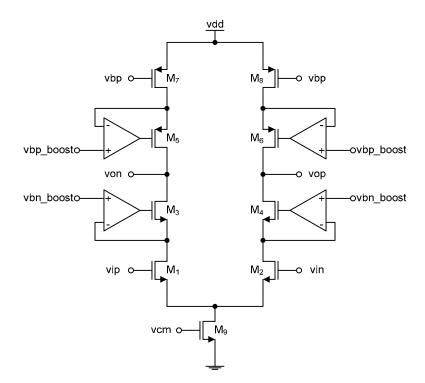

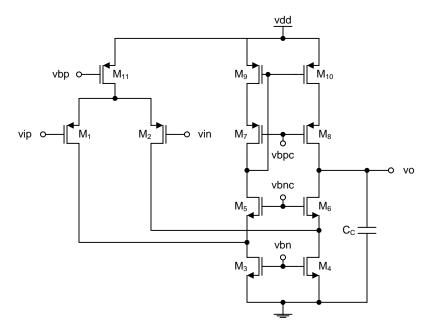

| Fig. 5.10: NMOS cascodes gain booster                                                                           | . 85 |

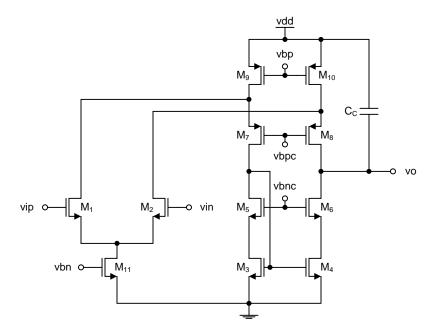

| Fig. 5.11: PMOS cascodes gain booster                                                                           | . 86 |

| Fig. 5.12: The cascode gain booster reference voltage (a) principle of operation (b)                            |      |

| implementation                                                                                                  | . 87 |

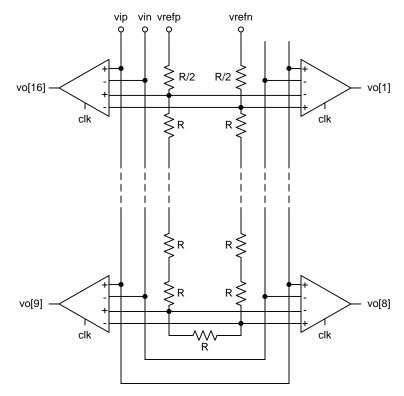

| Fig. 5.13: 17-level flash ADC                                                                                   | . 88 |

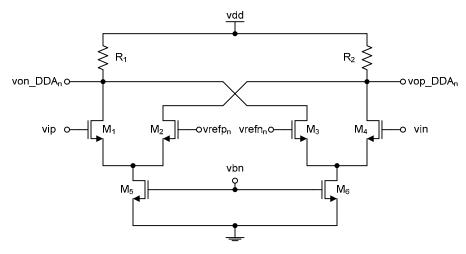

| Fig. | 5.14: Preamplifier                                                                                 | 88     |

|------|----------------------------------------------------------------------------------------------------|--------|

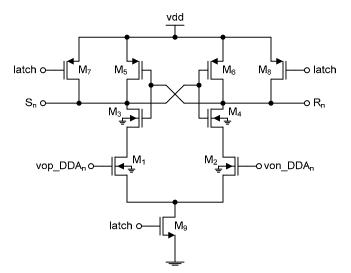

| Fig. | 5.15: Regenerative latch                                                                           | 89     |

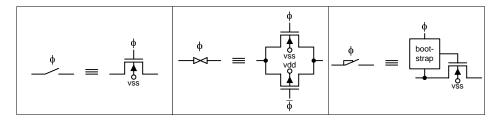

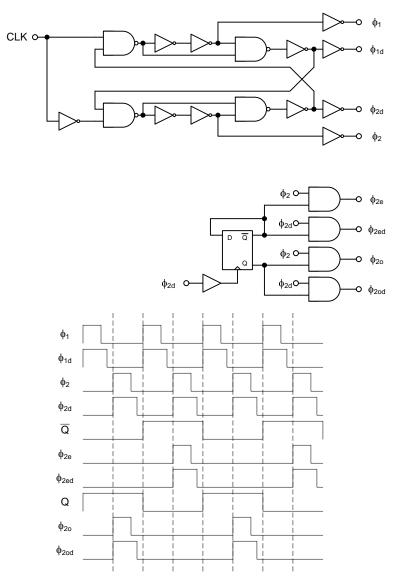

| Fig. | 5.16: Switches used in the modulator                                                               | 90     |

| Fig. | 5.17: Bootstrapped switch                                                                          | 91     |

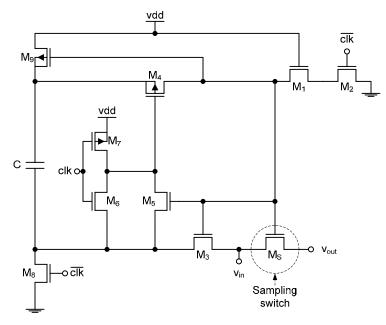

| Fig. | 5.18: Data weighted averaging                                                                      | 92     |

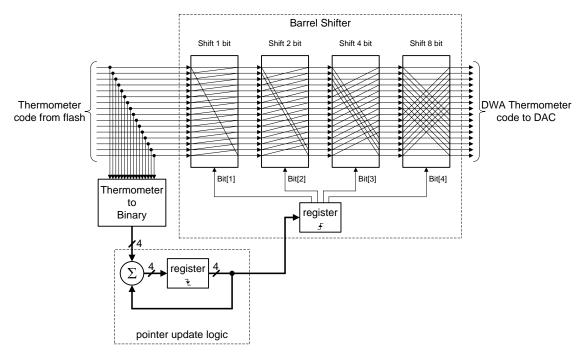

| Fig. | 5.19: Non-overlapping clock generator and its timing diagram                                       | 93     |

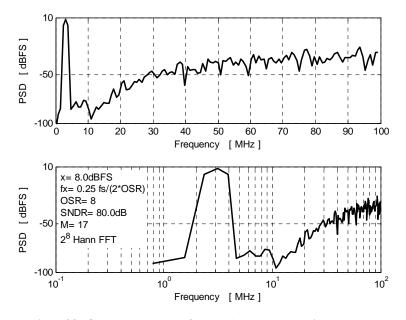

| Fig. | 5.20: Spectrum for the single-ended sampled signal on C <sub>S1</sub>                              | 94     |

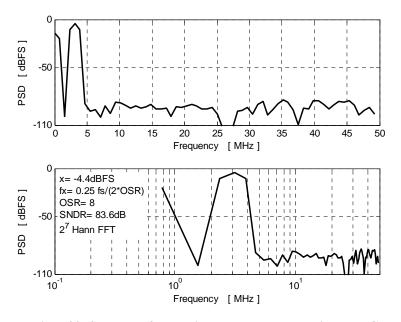

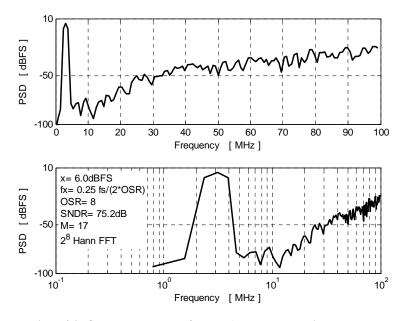

| Fig. | 5.21: Output spectrum for the $\Delta\Sigma$ modulator in feedback mode                            | 94     |

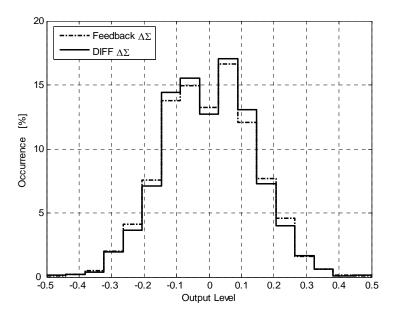

| Fig. | 5.22: Single-ended output level distribution for the integrators (same specifications as in        | n Fig. |

|      | 5.21)                                                                                              | 95     |

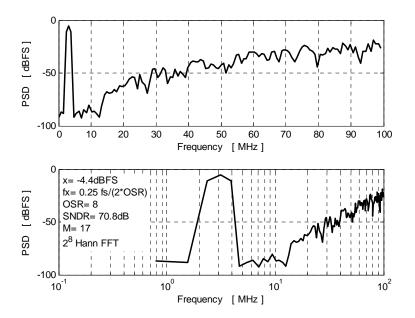

| Fig. | 5.23: Spectrum for the single-ended sampled signal on C <sub>S1</sub>                              | 95     |

| Fig. | 5.24: Output spectrum for the $\Delta\Sigma$ modulator in DIFF mode                                | 96     |

| Fig. | 5.25: Single-ended output level distribution for the integrators (same specifications as in        | n Fig. |

|      | 5.24)                                                                                              | 96     |

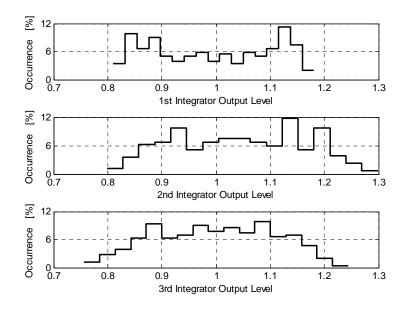

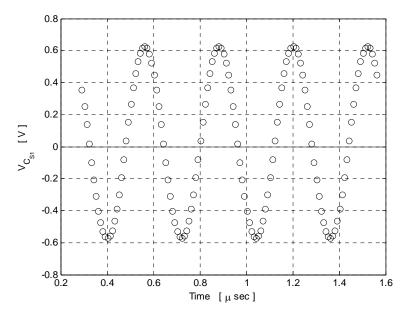

| Fig. | 5.26: Sampled signal on C <sub>S1</sub> (single-ended)                                             | 97     |

| Fig. | 5.27: Spectrum for the single-ended sampled signal on C <sub>S1</sub>                              | 97     |

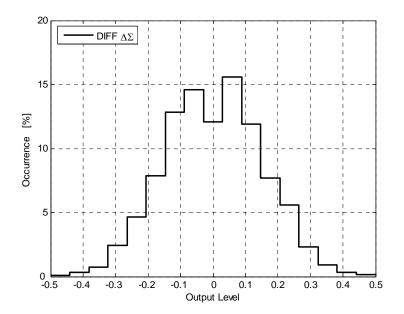

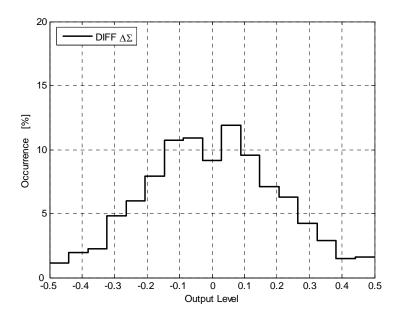

| Fig. | 5.28: Output spectrum for the $\Delta\Sigma$ modulator in DIFF mode                                | 98     |

| Fig. | 5.29: Single-ended output level distribution for the integrators (same specifications as in        | n Fig. |

|      | 5.28)                                                                                              | 98     |

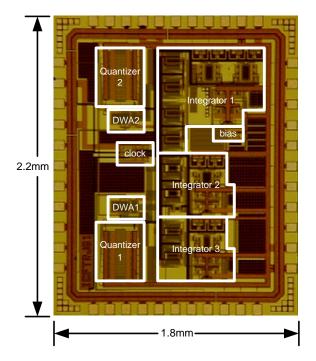

| Fig. | 5.30: Die photo                                                                                    | 99     |

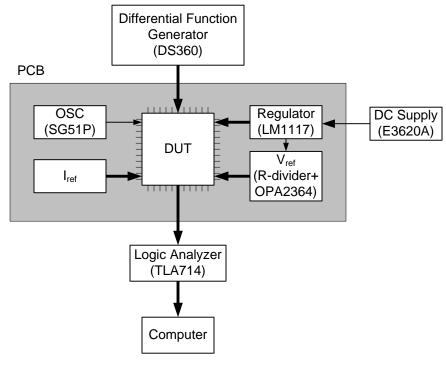

| Fig. | 5.31: Test setup                                                                                   | 100    |

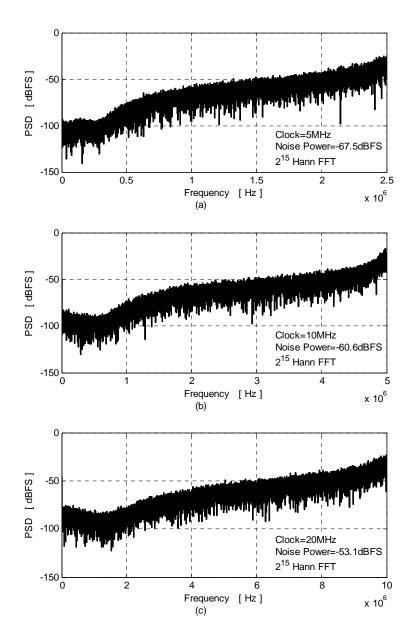

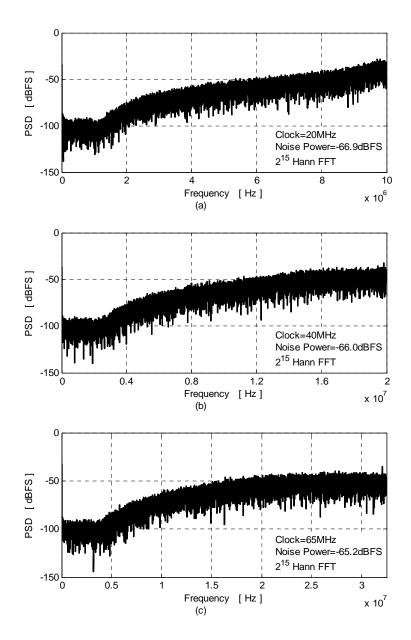

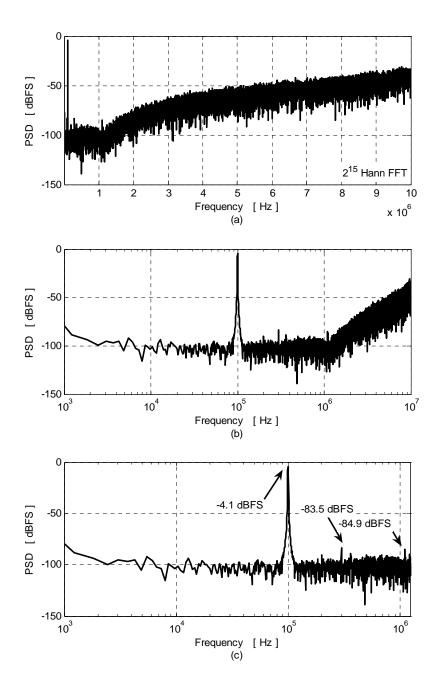

| Fig. | 5.32: Output spectrum before improving the decoupling on the DAC references for zero               | )      |

|      | input-signal with a sampling clock at (a) 5MHz (b) 10MHz (c) 20MHz                                 | 102    |

| Fig. | 5.33: Output spectrum after improving the decoupling on the DAC references for zero i              | nput-  |

|      | signal with a sampling clock at (a) 20MHz (b) 40MHz (c) 65MHz                                      | 103    |

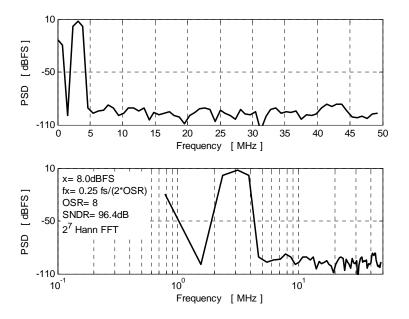

| Fig. | 5.34: Sample output spectrum for the $\Delta\Sigma$ modulator in DIFF mode (a) linear scale (b) lo | Эg     |

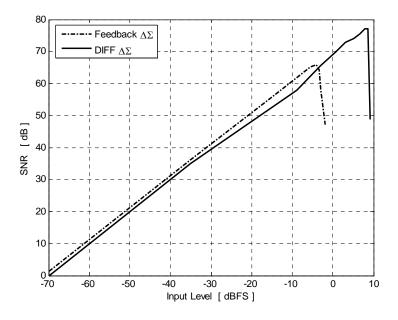

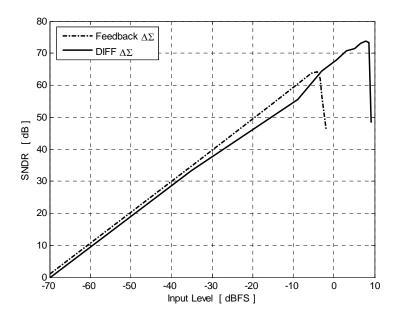

|      | scale                                                                                              | 104    |

| Fig. | 5.35: Measured SNR versus input-signal level                                                       | 106    |

| Fig. | 5.36: Measured SNDR versus input-signal level                                                      | 106    |

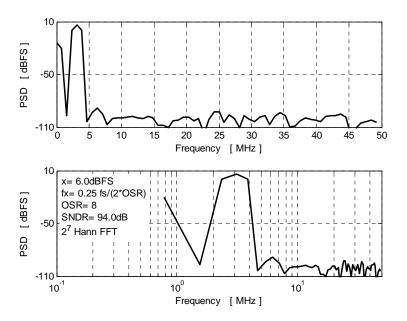

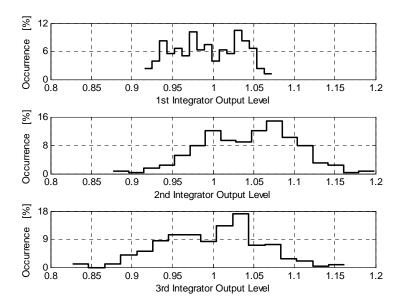

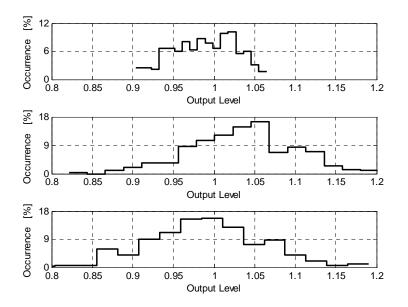

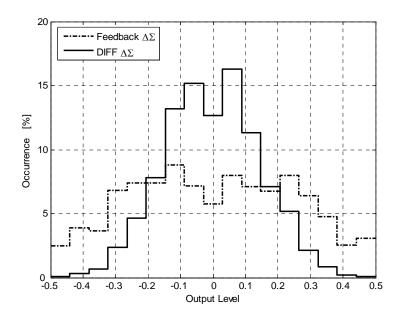

| Fig. | 5.37: Measured output level distribution for zero input-signal                                     | 107    |

| Fig. 5.38: Measured output level distribution for -4.1 dBFS input-signal (maximum SNR point                   |    |

|---------------------------------------------------------------------------------------------------------------|----|

| for the feedback modulator)                                                                                   | )8 |

| Fig. 5.39: Measured output level distribution for 6.0 dBFS input-signal (maximum level before                 |    |

| the external quantizer is overloaded in the DIFF modulator)10                                                 | 18 |

| Fig. 5.40: Measured output level distribution for 8.3 dBFS input-signal (maximum SNR point fo                 | r  |

| the DIFF modulator)10                                                                                         | 19 |

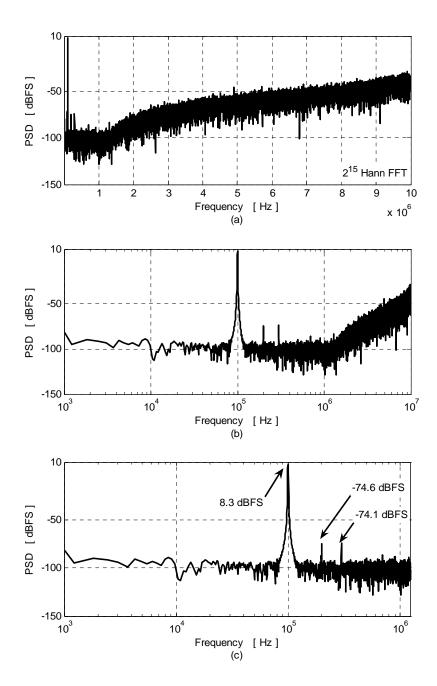

| Fig. 5.41: Sample output spectrum at peak SNR and SNDR for the feedback $\Delta\Sigma$ modulator (a)          |    |

| linear scale (b) log scale (c) signal band in log scale 11                                                    | 0  |

| Fig. 5.42: Sample output spectrum at peak SNR and SNDR for the DIFF $\Delta\Sigma$ modulator (a) linear       | [  |

| scale (b) log scale (c) signal band in log scale 11                                                           | 1  |

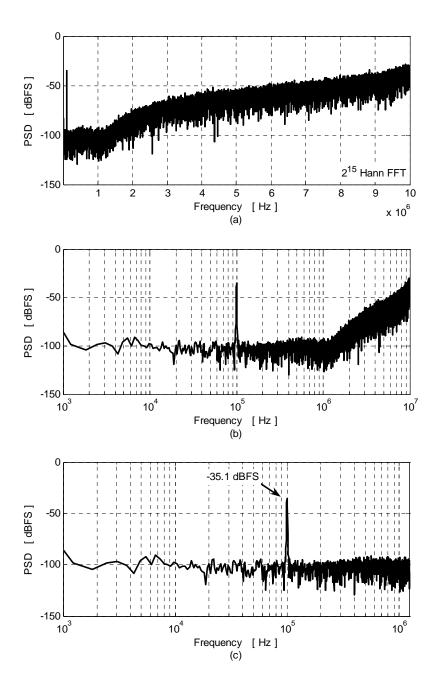

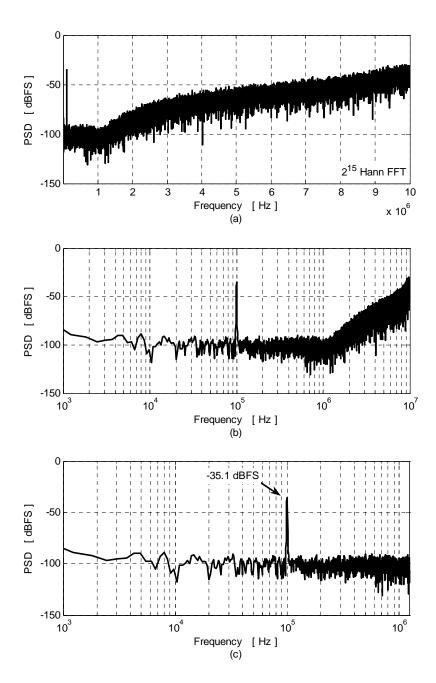

| Fig. 5.43: Sample output spectrum for the feedback $\Delta\Sigma$ modulator (a) linear scale (b) log scale (c | :) |

| signal band in log scale 11                                                                                   | 2  |

| Fig. 5.44: Sample output spectrum for the DIFF $\Delta\Sigma$ modulator (a) linear scale (b) log scale (c)    |    |

| signal band in log scale 11                                                                                   | 3  |

# List of Tables

| Table 3.1: Non-ideal and ideal transfer functions of the SPTI modulator                       | 36  |

|-----------------------------------------------------------------------------------------------|-----|

| Table 5.1: Coefficients for the $\Delta\Sigma$ modulator                                      | 74  |

| Table 5.2: $3\sigma$ signal swings at the output of the integrators and SNDR at maximum input | 74  |

| Table 5.3: Capacitor sizes used in the experimental modulator                                 | 82  |

| Table 5.4: Component sizes for the opamp in the first stage                                   | 84  |

| Table 5.5: Component sizes for the NMOS cascodes gain booster                                 | 85  |

| Table 5.6: Component sizes for the PMOS cascodes gain booster                                 | 86  |

| Table 5.7: Component sizes for the preamplifier                                               | 89  |

| Table 5.8: Component sizes for the regenerative latch                                         | 89  |

| Table 5.9: Component sizes for the bootstrapped switch                                        | 91  |

| Table 5.10: Summary of the measured performance for the $\Delta\Sigma$ modulator              | 105 |

# List of Abbreviations

| ADC      | Analog-to-Digital Converter                                |

|----------|------------------------------------------------------------|

| CDM      | Code Division Multiplexing                                 |

| CIFB     | Cascade of Integrators with distributed FeedBack           |

| CIFB-CIF | CIFB with Capacitive Input-Feedforward                     |

| CIFB-IF  | CIFB with Input-Feedforward                                |

| CIFF     | Cascade of Integrators with weighted FeedForward summation |

| CIFF-CIF | CIFF with Capacitive Input-Feedforward                     |

| CIFF-IF  | CIFF with Input-Feedforward                                |

| CMC      | Canadian Microelectronics Corporation                      |

| CQFP     | Ceramic Quad Flat Pack                                     |

| DAC      | Digital-to-Analog Converter                                |

| dBFS     | DeciBel with respect to Full-Scale                         |

| DDA      | Differential Difference Amplifier                          |

| DEM      | Dynamic Element Matching                                   |

| DIFF     | Digital Input-FeedForward                                  |

| DSP      | Digital Signal Processing                                  |

| DUT      | Device Under Test                                          |

| DWA      | Data Weighted Averaging                                    |

| FDM      | Frequency Division Multiplexing                            |

| FOM      | Figure of Merit                                            |

| LSB      | Least Significant Bit                                      |

| LTI      | Linear Time Invariant                                      |

| MASH     | Multi-stAge noise SHaping                                  |

| MIM      | Metal-Insulator-Metal                                      |

| MPSPTI   | mixed Multi-Path Single-Path Time-Interleaved              |

| MPTI     | Multi-Path Time-Interleaved                                |

| NTF      | Noise Transfer Function                                    |

| PCB    | Printed Circuit Board                           |

|--------|-------------------------------------------------|

| SISO   | . Single Input Single Output                    |

| SNDR   | . Signal to Noise plus Distortion Ratio         |

| SNR    | . Signal to Noise Ratio                         |

| SPMPTI | . mixed Single-Path Multi-Path Time-Interleaved |

| SPTI   | . Single-Path Time-Interleaved                  |

| SQNR   | . Signal to Quantization Noise Ratio            |

| STF    | . Signal Transfer Function                      |

| TDM    | . Time Division Multiplexing                    |

| TI     | . Time-Interleaving                             |

| ZITI   | . Zero-Insertion Time-Interleaved               |

Chapter 1:

### Introduction

#### 1.1 Motivation

THE phenomenal advances in CMOS integrated circuit technology coupled with the development of sophisticated *digital signal processing* (DSP) algorithms have shifted more of the signal processing from the analog to the digital domain, and have fueled the development of a wide range of new applications. In many applications, digital circuits still need to communicate with the real world, which is inherently analog. Therefore, the links between the analog and digital domains are of great importance. The analog information coming from the real world is filtered and converted into digital bits by an *analog-to-digital converter* (ADC). The data processed in the digital domain is fed back to the analog world using a *digital-to-analog converter* (DAC) and an analog post filter.

The technological advances in CMOS allow digital circuits to run faster and to consume less power. Also, the increase in integration allows an entire system to be fabricated on a single chip. Therefore, digital circuits are benefiting tremendously from advances in CMOS technology. Conversely, these advances make it more difficult to design analog circuits due to diminishing voltage supplies and smaller transistor intrinsic gain; moreover, many of the new DSP algorithms have placed more stringent requirements on the analog-digital interface. Therefore, the interface between the digital world and the analog world is becoming the bottleneck in the achievable performance of modern systems.

In this thesis, a specific part of the analog-digital interface is investigated, namely the ADC. Although there are a number of methods to design an ADC, delta-sigma ( $\Delta\Sigma$ ) converters have many advantages that make them great candidates for such environments. Their tolerance to component mismatches and circuit non-idealities relaxes the requirements placed on the analog building blocks. Furthermore, they simplify the anti-aliasing filter design requirements by potentially moving most of the filtering operations into the digital domain. Therefore,  $\Delta\Sigma$  modulators are widely used for high-resolution and low-bandwidth analog-to-digital converters.

Their dominance in such applications stems from the inherent trade-off in the way they operate. They sample the input-signal at a rate much higher than the Nyquist rate. Then, they process the high-speed low-resolution digital signal to generate a high-resolution low-speed representation of the analog input. The intensive digital post-processing makes CMOS a great technology for implementing  $\Delta\Sigma$  converters, however, the low voltage environment of modern CMOS makes the design of the analog part more challenging.

The challenge today is to develop new architectures and circuits for implementing the ADCs under the increasing technological difficulties and rising demands from DSP algorithms. Specifically, increasing the speed of  $\Delta\Sigma$  modulators and enabling the reliable operation in low-voltage environments are investigated.

Parallelism can be exploited as a method to increase the speed of  $\Delta\Sigma$  modulators. Parallelism by time-interleaving, based on the block filtering theory, is a candidate to achieve higher speeds [1]. In this thesis, new time-interleaved topologies are introduced and evaluated.

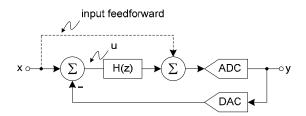

The idea of controlling the internal states of  $\Delta\Sigma$  modulators to reduce the signal swing and linearity requirements is a significant development [2]. It makes the design of  $\Delta\Sigma$  based ADCs in low-voltage environments reliable, and sets it farther apart from other ADC techniques. Therefore, the state control achieved by the input-feedforward is investigated thoroughly. Furthermore, the capacitive-input feedforward and the double sampled input are proposed to simplify input-feedforward modulators. Finally, a new input-feedforward technique is proposed and a prototype chip is implemented in CMOS technology.

#### **1.2 Thesis Outline**

This dissertation is organized in six chapters including this introduction. Chapter 2 provides a brief overview of  $\Delta\Sigma$  modulators. It discusses the most common single-loop topologies and analyzes the tradeoffs involved in their design. Next, multi-stage noise shaping modulators are discussed. Finally, time-interleaved  $\Delta\Sigma$  modulators are reviewed.

Chapter 3 introduces a new time-interleaved  $\Delta\Sigma$  modulator topology. The proposed architecture requires a single modulator with extra quantizers and interconnects to achieve an arbitrary time-interleaving factor. Finite opamp gain and bandwidth result in a mismatch between the noise transfer functions of the internal quantizers which degrades the performance of the new modulator. Two techniques are presented to mitigate the mismatch problem. First, a hybrid topology where the first stage uses multiple integrators while the rest of the modulator uses a single path of integrators is presented. Second, a digital calibration method reduces the mismatch and relaxes the requirements on the analog components. The issue of multi-bit digital-to-analog nonlinearity is discussed for the new topology and a method to minimize its effect is proposed.

Chapter 4 analyzes the input-feedforward modulator's advantages and complications. It introduces the double sampling input as a method of mitigating the timing constraint due to the critical path of the input-feedforward path. The capacitive-input-feedforward is introduced to eliminate the problematic adder at the quantizer input. Finally, a new digital input-feedforward  $\Delta\Sigma$  modulator is proposed and evaluated in this chapter.

Chapter 5 discusses the design of a configurable  $\Delta\Sigma$  modulator. The configurability allows the modulator to operate in the single-loop mode or in the digital input-feedforward mode. The implementation of the modulator in 0.18µm CMOS technology is discussed. Finally, the test chip and the test set-up are described and measured results are provided.

Chapter 6 summarizes the thesis, highlights its research contributions, and suggests areas of research for future exploration.

Chapter 2:

### Fundamentals of ΔΣ Modulators

**D**ELTA-SIGMA modulation is a popular method for achieving high-resolution data converters. Their popularity is due to the relaxed requirements they place on analog circuits. Furthermore, the evolution of new  $\Delta\Sigma$  architectures reduces the analog complexity and makes their implementation in nano-scale CMOS technology feasible.

This chapter is not intended to be a comprehensive background to  $\Delta\Sigma$  modulation, instead, it provides the important aspects necessary to understand the subsequent chapters. The technical literature contains a wealth of information on  $\Delta\Sigma$  modulation, the most thorough and up to date is presented in [3].

The outline of this chapter is as follows: Section 2.1 reviews single-loop  $\Delta\Sigma$  modulators. Section 2.2 provides an overview of the multistage noise shaping architectures. In Section 2.3, time-interleaving  $\Delta\Sigma$  modulators are reviewed.

#### 2.1 Single Loop ΔΣ Modulators

The architectural level development of  $\Delta\Sigma$  modulators involves the design of three components: the *noise transfer function* (NTF), the *signal transfer function* (STF), and the internal states of the modulator.

Traditionally, designers concentrated on the design of the NTF because it determines the achievable *signal to quantization noise ratio* (SQNR). Topologies suitable for ADC applications which evolved from the early days can be classified in two categories based on their loop filter implementation: feedback  $\Delta\Sigma$  modulators and feedforward  $\Delta\Sigma$  modulators [4]. The feedback and feedforward topologies provide the designer with one degree of freedom. Therefore, the STF and the states are fixed by the choice of the NTF.

Recently, the input-feedforward concept is used to control the states of the modulator [2]. The input-feedforward path alleviated some of the drawbacks of the feedback and feedforward topologies, however, it has added a few complications. These issues are discussed later in this chapter.

In general, the design of the STF is not of significant concern as long as it does not degrade the modulator stability. In some circumstances however, the control of the STF could be of interest. For example, an ADC at a receiver input with large channel interference requires significant continuous-time analog filtering. This can be relaxed if the STF is designed to attenuate the out of band spectrum [5].

To keep the scope of the analysis focused; this discussion is limited to  $\Delta\Sigma$  modulators with pure differentiator type NTFs that employ internal quantizers with a sufficient number of levels to keep the modulator stable for any NTF out of band gain. The relation of the topologies to their integrated circuit implementation is emphasized.

#### 2.1.1 Feedback ΔΣ modulators

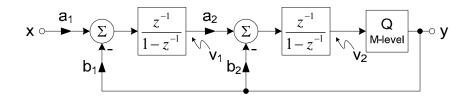

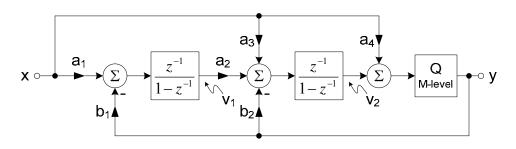

The simplest method to construct high order  $\Delta\Sigma$  modulators is to cascade several integrators in the forward path, with each integrator receiving feedback from the quantizer to ensure stability. Such a structure is called the *cascade of integrators with distributed feedback* (CIFB). The CIFB topology is illustrated for a second-order modulator in Fig. 2.1.

Fig. 2.1: Second-order CIFB modulator

Analysis of the linearized system with  $a_1 = a_2 = b_1 = 1$ ,  $b_2 = 2$  leads to the following results:

$$STF = \frac{y}{x} = z^{-2}$$

(2-1)

$$NTF = \frac{y}{q} = (1 - z^{-1})^2$$

(2-2)

$$v_1 = z^{-1} (1 + z^{-1}) x - z^{-1} (1 - z^{-1}) q$$

(2-3)

$$v_2 = z^{-2}x - z^{-1}(2 - z^{-1})q$$

(2-4)

where q is the quantization noise from the internal quantizer, and  $v_1$  and  $v_2$  are the signals at the outputs of the first and second integrators, respectively. The STF exhibits an all-pass response and the NTF provides a second-order pure differentiator type high-pass response.

The main advantage of the CIFB topology is that it is easy to implement with low sensitivity to component variations. The main disadvantage of this topology is that the signals at the output of the integrators are a function of the input-signal as given in Eqs. (2-3) and (2-4), resulting in two effects. First, the signal swing at the output of the opamps is large which makes their implementation in the low-voltage, nano-scale CMOS technology difficult. Second, opamp nonlinearities generate distortion that is a function of the input-signal. The opamp distortion can severely limit the achievable SNDR. Another disadvantage of the CIFB topology is that the NTF, STF, and states cannot be set independently. Therefore, if we pick a certain NTF, then the STF and states are fixed.

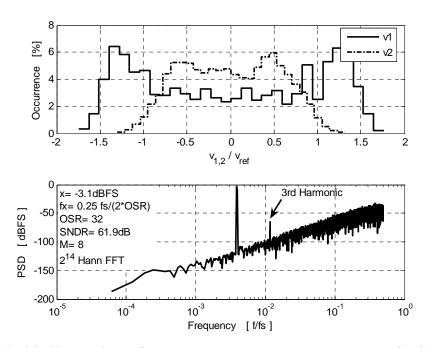

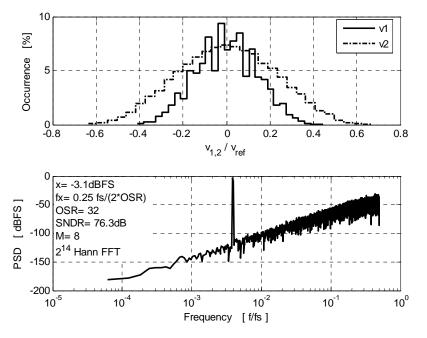

The CIFB topology is simulated using Matlab and Simulink. The probability density function of integrator outputs and a sample output spectrum including opamp third-order distortion are shown in Fig. 2.2 for a sinusoidal input signal which parameters are specified in the figure. The third-order distortion is modelled as a power series with the third-order term corresponding to 1% third-order harmonic distortion for a full scale signal.

Fig. 2.2: Signal swing at Opamp outputs and sample output spectrum for CIFB

Simulations indicate that the signal swings at the internal nodes can be over 1.5 times larger than the internal quantizer reference voltage. On the other hand, the input-signal range is from 50 to 80% of the quantizer reference voltage and depends on the loop order and number of bits in the quantizer [4]. Therefore, the input-signal is going to be relatively small when compared

to other topologies, and to meet thermal noise requirements the capacitor sizes must be larger, leading to greater power dissipation. The third harmonic generated by the opamp nonlinearity is clear in the output spectrum shown in Fig. 2.2. Distortion severely reduces the SNDR of the CIFB topology from the ideal 76 dB to 62 dB for the example shown in Fig. 2.2.

The CIFB is the most commonly used topology for  $\Delta\Sigma$  modulators. An example of the CIFB topology is implemented as a third-order CIFB  $\Delta\Sigma$  modulator using a 4-bit internal quantizer and operating with a sampling frequency of 100 MHz at an OSR of 8 [6]. The modulator achieves a *signal to noise plus distortion ratio* (SNDR) of 67 dB and a peak *signal to noise ratio* (SNR) of 68 dB with a 12.5 MS/s conversion rate. The modulator is implemented in 0.65µm technology and powered with 5 V supply while consuming 380mW.

#### 2.1.2 Feedforward ΔΣ modulators

Distributed feedback is used to ensure stability of the cascade of integrators in the forward path of the CIFB topology. Alternatively, weighted feedforward paths can be used to establish stability. Such a structure is called the *cascade of integrators with weighted feedforward summation* (CIFF). The resulting CIFF topology for a second-order modulator is shown in Fig. 2.3.

Fig. 2.3: Second-order CIFF modulator

Analysis of the linearized system with  $a_1 = a_2 = b_1 = 1$ ,  $a_3 = 2$  leads to the following results:

$$STF = \frac{y}{x} = z^{-1} \left( 2 - z^{-1} \right)$$

(2-5)

$$NTF = \frac{y}{q} = (1 - z^{-1})^2$$

(2-6)

$$v_1 = z^{-1} (1 - z^{-1}) x - z^{-1} (1 - z^{-1}) q$$

(2-7)

$$v_2 = z^{-2}x - z^{-2}q \tag{2-8}$$

where q is the quantization noise from the internal quantizer, and  $v_1$  and  $v_2$  are the signals at the outputs of the first and second integrators, respectively.

The CIFF improves the performance of CIFB in terms of the signals at the output of the integrators. As can be seen from Eq. (2-7), the signal at the output of the first opamp contains a first-order noise shaped input-signal component in addition to shaped quantization noise. This reduces signal swing and reduces dependence of the distortion on the input-signal. Both of these benefits are illustrated in Fig. 2.4 for a sinusoidal input signal which parameters are specified in the figure. The signal swing at the output of the first opamp is significantly reduced and the output spectrum does not show harmonic distortion. The second opamp output still contains an input-signal component as can be seen from Eq. (2-8); however, nonlinearities at this stage are not as important since they are second-order noise shaped when referred back to the input.

Fig. 2.4: Signal swing at Opamp outputs and sample output spectrum for CIFF

The main disadvantage of the CIFF topology can be seen by investigating its STF given in Eq. (2-5). The STF has a high frequency boost with a gain of one at low frequencies and a gain of three at half the sampling frequency. The amplification of the out-of-band frequencies due to the high frequency boost can overload the quantizer and drive the modulator into instability. Unfortunately, the NTF, STF, and modulator states are not independent. Selection of the NTF fixes the magnitude of the high frequency boost in the STF. One of the fastest CMOS  $\Delta\Sigma$  modulators reported in literature is implemented using the CIFF topology where a fifth-order CIFF  $\Delta\Sigma$  modulator uses a 4-bit internal quantizer and operates at a 200 MHz sampling frequency at an OSR of 8 [7]. The modulator achieves an SNDR of 72 dB with a peak SNR of 82 dB at a conversion rate of 25 MS/s. The differential input signal range is 1.6 V<sub>pp,diff</sub>. This performance is achieved in 0.18µm CMOS technology and powered with 1.8 V supply while consuming 200mW.

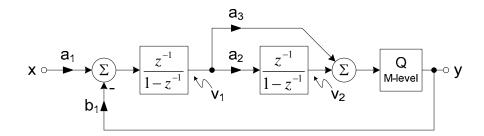

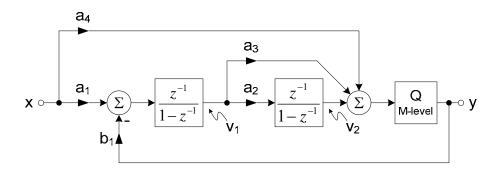

#### 2.1.3 Feedback ΔΣ modulators with input-feedforward

The input-signal component at the opamp outputs in the CIFB topology can be eliminated by feeding the input-signal forward such that the input-signal components cancel out. The resulting *CIFB with input feedforward* (CIFB-IF) topology is illustrated for a second-order modulator in Fig. 2.5.

Fig. 2.5: Second-order CIFB-IF modulator

Analysis of the linearized system with  $a_1 = a_2 = a_4 = b_1 = 1$ ,  $a_3 = b_2 = 2$  leads to the following results:

$$STF = \frac{y}{x} = 1 \tag{2-9}$$

$$NTF = \frac{y}{q} = (1 - z^{-1})^2$$

(2-10)

$$v_1 = -z^{-1} (1 - z^{-1}) q$$

(2-11)

$$v_2 = -z^{-1} \left( 2 - z^{-1} \right) q \tag{2-12}$$

where q is the quantization noise from the internal quantizer, and  $v_1$  and  $v_2$  are the signals at the outputs of the first and second integrators, respectively.

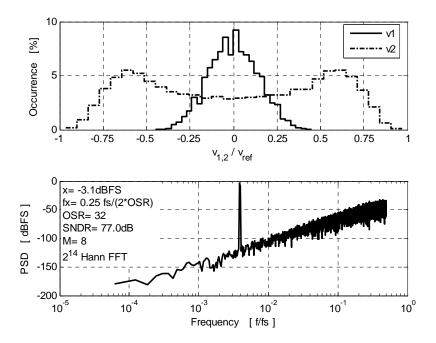

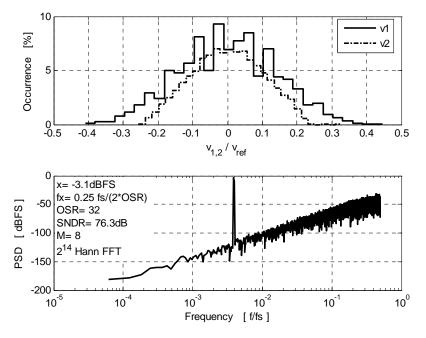

The input-feedforward modifies  $v_1$ ,  $v_2$ , and the STF without affecting the NTF. The signals  $v_1$  and  $v_2$  are free of the input-signal component. Therefore, the signal swings are smaller and the distortion generated by the opamp is independent of the input-signal. These advantages

are illustrated in Fig. 2.6 for a sinusoidal input signal which parameters are specified in the figure. The STF magnitude response maintains its all pass response, however, its phase response changes.

Fig. 2.6: Signal swing at Opamp outputs and sample output spectrum for CIFB-IF

The disadvantage of the CIFB-IF topology is the increased loading that the input has to drive, which can be particularly large for higher order modulators. This is because of the distributed feedforward paths that are needed to achieve the input-signal cancellation. In the second-order case, for example, there is the main sampling capacitor at the input as well as two extra sampling capacitors to feed the input-signal forward. It should be mentioned that the extra capacitors are usually smaller than the input sampling capacitor because the thermal noise on these capacitors is noise shaped when referred back to the input and therefore, their size can be smaller. Another disadvantage of the CIFB-IF topology is the delay-free path from the input, through the quantizer, and back to the modulator input. This delay-free path imposes implementation complications that are significant for high speed modulators. This problem and a possible solution are investigated thoroughly in Chapter 4.

An example of the CIFB-IF topology is demonstrated in [8] for a second-order modulator using a single-bit internal quantizer and operating with a sampling frequency of 105 MHz. For a signal bandwidth of 300 kHz (1.1 MHz), the modulator achieves an SNDR of 80 dB (78 dB) with a peak SNR of 82 dB (76 dB). The differential input signal range is 1.4  $V_{pp,diff}$ . The modulator is

implemented in 0.13µm CMOS technology and powered with a 1.5 V supply while consuming only 8mW of power.

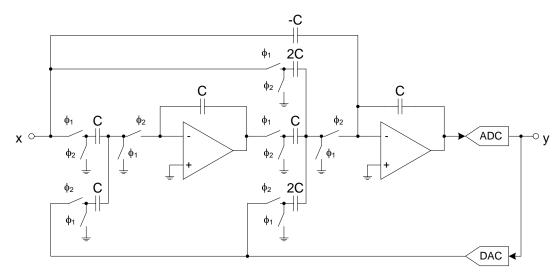

#### 2.1.4 Feedforward ΔΣ modulators with input-feedforward

The input-feedforward concept can be used to modify the STF of the CIFF topology without affecting its NTF. Therefore, the high frequency boost in the STF of the CIFF topology can be eliminated. The resulting *CIFF with input feedforward* (CIFF-IF) topology is illustrated in Fig. 2.7 for a second-order modulator [2].

Fig. 2.7: Second-order CIFF-IF modulator

Analysis of the linearized system with  $a_1 = a_2 = a_4 = b_1 = 1$ ,  $a_3 = 2$  leads to the following results:

$$STF = \frac{y}{x} = 1 \tag{2-13}$$

$$NTF = \frac{y}{q} = (1 - z^{-1})^2$$

(2-14)

$$v_1 = -z^{-1} (1 - z^{-1}) q$$

(2-15)

$$v_2 = -z^{-2}q \tag{2-16}$$

where q is the quantization noise from the internal quantizer, and  $v_1$  and  $v_2$  are the signals at the outputs of the first and second integrators respectively.

The input-feedforward changes the problematic high frequency boost in the STF of the CIFF topology to an all-pass STF in the CIFF-IF topology with no effect on the NTF. In addition the signals  $v_1$  and  $v_2$  are free of the input-signal component. It is interesting to note that this modulator achieves the smallest signal swings at the output of the opamps among the topologies discussed, as seen in Fig. 2.8 for a sinusoidal input signal which parameters are specified in the

figure. Specifically, comparing the CIFF-IF and the CIFB-IF topologies,  $v_1$  is similar. However,  $v_2$  is smaller in the CIFF-IF topology since it contains quantization noise only in contrast to the CIFB-IF topology where  $v_2$  contains shaped quantization noise.

Fig. 2.8: Signal swing at Opamp outputs and sample output spectrum for CIFF-IF

The disadvantage of the CIFF-IF is the delay-free path from the input, through the quantizer, and back to the modulator input. This is the same problem as the CIFB-IF and is discussed further in Chapter 4.

#### 2.2 Multistage Noise Shaping Modulators

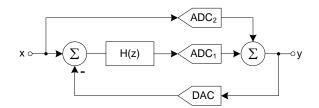

The single loop topologies presented in the previous section operate on the principle of filtering the quantization noise out of the signal band and are called noise shapers. Another useful method for reducing quantization noise depends on noise cancellation, in addition to noise shaping. *Multistage noise shaping* (MASH) modulators fall under the noise cancellers category.

Multistage modulators allow the designer to build high order structures by cascading low order modulators. They have two advantages: using first and second-order modulators in each stage ensure stability of the overall modulator and they are more attractive for low OSR implementation. The low OSR advantage stems from the fact that in single-loop topologies the marginal improvement of the SQNR diminishes as the OSR decreases. The diminishing return makes the high-order single-loop topologies less attractive for high speed applications. The drawback of MASH is that noise cancellation requires good matching between the analog and the digital circuits. Matching can be achieved by imposing higher requirements on the analog blocks to make them more ideal. Alternatively, digital circuits can be calibrated to match the analog ones and hence maintain the relaxed requirements on the analog components.

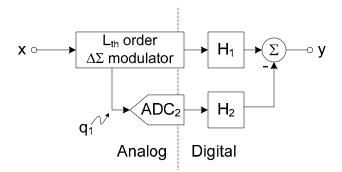

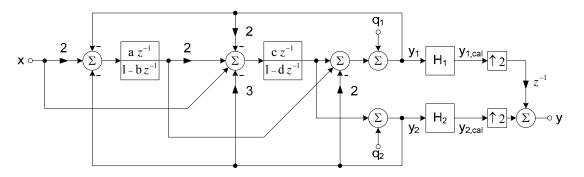

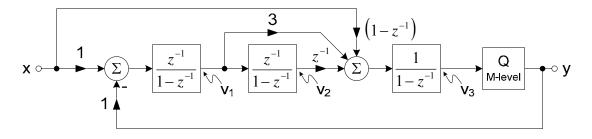

The multistage topology is illustrated using a cascade of two stages as shown in Fig. 2.9. The first stage is a general  $\Delta\Sigma$  modulator of order L and the second stage is a general static (i.e. zero-order) ADC, hence, the name of this modulator is L-0 (also commonly known as the Leslie-Singh structure). In general, the multistage modulator can include any number of stages and each stage can be of different order. In the L-0 modulator, the second stage processes the quantization noise from the first stage (q<sub>1</sub>). Then, the output from both stages is processed by the digital filters H<sub>1</sub> and H<sub>2</sub> and finally subtracted to produce the final output. H<sub>1</sub> is simply unit delays equal to the latency of the second stage while H<sub>2</sub> is equal to the NTF of the first stage.

Fig. 2.9: The L-0 multistage modulator

Analysis of the linearized system leads to the following results assuming no latency in ADC<sub>2</sub>:

$$y = STF_1 x - NTF_1 q_2 \tag{2-17}$$

where  $q_2$  is the quantization noise from ADC<sub>2</sub>, and STF<sub>1</sub> and NTF<sub>1</sub> are the signal and noise transfer functions of the first stage.

The difference between the L-0 multistage and a single loop modulator of order L is that the output contains the shaped quantization noise from the second stage instead of the first stage. Therefore, the quantization noise from the first stage is completely cancelled at the output. By making  $q_2$  smaller than  $q_1$ , the SQNR is improved.

An example of the multistage topology is presented in [9] where a 2-0 structure is used operating at 20 MHz clock rate. The first stage is a second-order modulator with a five-bit internal quantizer and the second stage is a four-stage 12 bit pipeline ADC. The modulator achieves a SNR of 89 dB at an OSR of 8 (1.25 MHz signal bandwidth) and 82 dB at an OSR of 4 (2.5 MHz signal bandwidth). The modulator is implemented in 0.6µm CMOS technology and powered with a 5 V analog supply and 3 V digital supply while consuming 550mW of power.

#### 2.3 Time-Interleaved ΔΣ Modulators

The usual system level design parameters for  $\Delta\Sigma$  modulators are the shape and order of the loop-filter, the OSR, and the number of bits in the internal quantizer. High-speed applications require low OSRs thereby limiting the choices available for the designer. One way of adding another degree of freedom is to use parallel  $\Delta\Sigma$  structures. The simplest method of making parallel converters is through the use of *time-interleaving* (TI) which is simply a time-division multiplexing scheme where an array of individual converters are clocked at different instants in time. Unfortunately, exploiting simple time-interleaved parallelism is not a straightforward process for  $\Delta\Sigma$  modulators due to their recursive nature. Straightforward TI adaptation to  $\Delta\Sigma$ modulators results in a 3 dB improvement in the SNR for each doubling of converters regardless of the order of the modulator. To overcome this problem, different schemes of parallel modulators have been devised. They can be classified in one of three main categories: *frequency division multiplexing* (FDM) [10], *code division multiplexing* (CDM) [11], and *time division multiplexing* (TDM) [1].

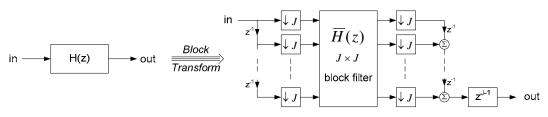

TDM can be implemented by deploying the theory of block digital filtering. The principle of block digital filtering is based on transforming a *linear time-invariant* (LTI) *single-input* single-output (SISO) system with transfer function H(z) to an equivalent multi-input multi-output system with transfer function  $\overline{H}(z)$ , as shown in Fig. 2.10.

Fig. 2.10: H(z) and its blocked version with block length J

The internal circuitry of the block filter operates in parallel and at a reduced rate by the factor J. For example, using this transformation for a  $\Delta\Sigma$  modulator with J=2 allows the internal modulators to either operate at half-speed for the same resolution, or at enhanced resolution for the same speed. This improvement is significant in wide bandwidth applications where the sampling speed is limited by the technology and resolution requirements.

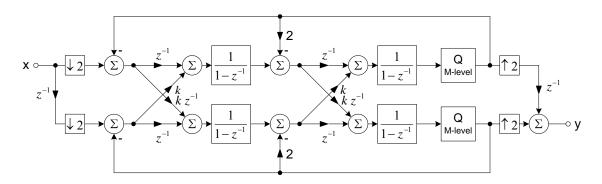

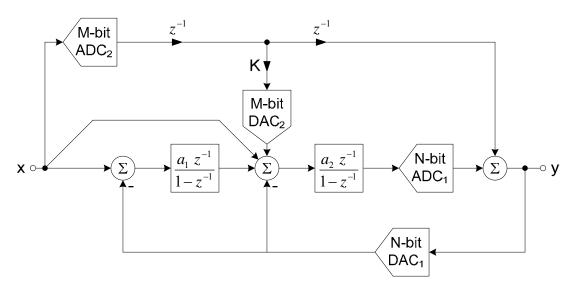

The block digital filtering has facilitated the design and construction of a true TI  $\Delta\Sigma$  modulator [1]. A second-order, time-interleaved by 2 (J=2), CIFB  $\Delta\Sigma$  modulator is shown in Fig. 2.11 as an example of the technique.

Fig. 2.11: Second-order time-interleaved by 2 CIFB  $\Delta\Sigma$  modulator

The k-factor shown in Fig. 2.11 is used to deal with the issue of opamp DC offsets [1]. DC offsets are problematic in time-interleaved modulators because the difference in offset between the two branches drives the modulator to instability. Reducing the cross-coupling coefficients gives more control to each parallel  $\Delta\Sigma$  modulator, thus enabling the negative feedback loop to adjust, which maintains DC stability. However, reducing k from unity modifies the STF and results in an increase of the quantization noise in the signal band, thereby reducing the SNDR. The choice of k is a tradeoff between the offset value that the modulator can tolerate and the achievable SNR. A significant advantage of the k-factor is the creation of a notch at half the sampling frequency. This notch attenuates the aliasing that occurs due to component mismatches [1]. There are two potential limiting factors in the time-interleaving modulators especially for an interleaving factor larger than two. First, the analog demux at the modulator input. This limitation is discussed in more detail below and in Chapter 3. Second, the critical path created due to the lack of delays between the output of a quantizer and the input of another.

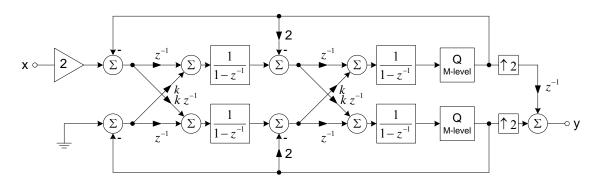

A high-speed demux is needed at the input of the modulator to sample the input-signal and distribute it to the individual internal modulators. The demux operates at the full speed of the overall TI structure. For example, for a time-interleaving factor of 4, the demux operates at four times the speed of the individual  $\Delta\Sigma$  modulators. The high-speed demux can become the limiting factor in the performance especially for higher-order TI structures (J>2). A solution to the demux problem for J=2 is to sample each branch at a different phase of the two non-overlapping clocks [1]. Therefore, the demux is inherent in the operation of the modulator. Another more general solution that can be used for any J is called the zero-insertion interpolation technique [12], which is shown in Fig. 2.12 for J=2 second-order CIFB topology. The *zero-insertion time-interleaved* (ZITI)  $\Delta\Sigma$  samples the input-signal at the operating frequency of the individual  $\Delta\Sigma$  modulator and applies these samples to one branch only with the inputs to the others grounded.

Fig. 2.12: Second-order ZITI with J=2 CIFB  $\Delta\Sigma$  modulator

The sampled input must be amplified (by J) to compensate for the lost signal power resulting from supplying zero input instead of the input-signal to the other branches. However, the input signal amplification causes the ZITI modulator to become unstable at smaller input levels than the traditional TI modulator. In addition, The ZITI modulator still suffers from DC offsets and therefore the cross-coupling coefficient k must be set appropriately.

#### 2.4 Summary

The design of  $\Delta\Sigma$  modulators involves tradeoffs between the NTF, STF, and internal states. Different topologies provide different degrees of freedom in the determination of these three parameters. The NTF determines the achievable SNDR for a given modulator. The internal states are significant from the analog circuit standpoint; therefore, the design of the states is critical for the reliable implementation of  $\Delta\Sigma$  modulators in the nano-scale CMOS technology.

$\Delta\Sigma$  modulators can be classified in two broad categories: noise shapers and noise cancellers. Multi-stage  $\Delta\Sigma$  modulators are noise cancellers. For the noise cancellation to work properly, good matching between the analog part and the digital part is required.

Parallelism can be used to improve the speed of oversampled modulators. Specifically, time-interleaving based on the block filtering theory can increase the attainable bandwidth of a given modulator.

## Appendix A: Modeling Non-Idealities in Switched-Capacitor ΔΣ Modulators

Behavioral simulations provide a convenient way to understand the operation of systems and offer a quick method to evaluate the tradeoffs involved in their design. High-level simulations are particularly useful in the design of  $\Delta\Sigma$  modulators because of the strong non-linear nature of these modulators. Since linearized models provide a qualitative understanding of  $\Delta\Sigma$  modulators only, a full time-domain simulation of the modulators is necessary to verify their operation. Matlab and Simulink is the tool of choice for performing system level simulations due to its extensive number of toolboxes and ease of use.

This appendix focuses on the simulation of non-idealities in switched-capacitor circuits that are critical to the operation of  $\Delta\Sigma$  modulators. In particular, the settling behavior of switched-capacitor integrators is studied to assist in the development of a Simulink model that takes settling errors into account. With this model, initial estimates of the required opamp specifications can be determined and used in the circuit level design.

There are two strategies for determining the opamp requirements in the design of  $\Delta\Sigma$  modulators. The first strategy is to design the integrators to settle to the full accuracy of the overall modulator. In this case, analytical methods can be used to determine the opamp specifications directly. In the second strategy, the integrators are allowed to settle to less than the full accuracy, however, their settling must be linear. The incomplete linear settling changes the coefficient value of the integrators which alters the NTF and the STF. The changes in the transfer functions have an insignificant effect on the performance of  $\Delta\Sigma$  modulators, especially for single loop topologies. Consequently, if slewing in the opamp is guaranteed not to occur, a more power efficient modulators can be obtained by following the second design strategy. Therefore, the non-linear nature of  $\Delta\Sigma$  modulators in addition to its relaxed settling requirements makes system level time-domain simulations a desirable step in the design process.

The settling behavior of a switched-capacitor integrator can be divided into static settling and dynamic settling. The static settling is determined by the finite gain of the opamp and is independent of time. The dynamic settling is a function of the speed of the modulator and is limited by the finite unity-gain frequency and the slew rate of the opamp.

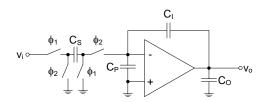

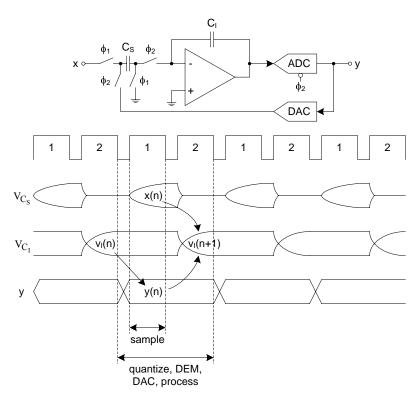

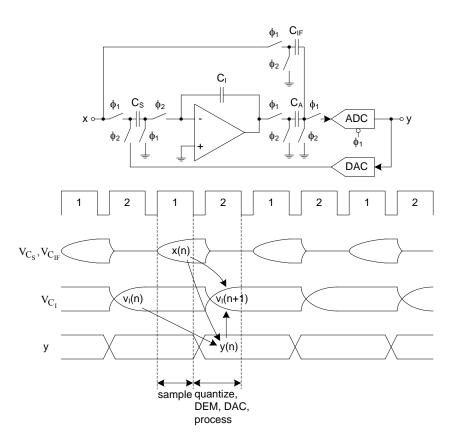

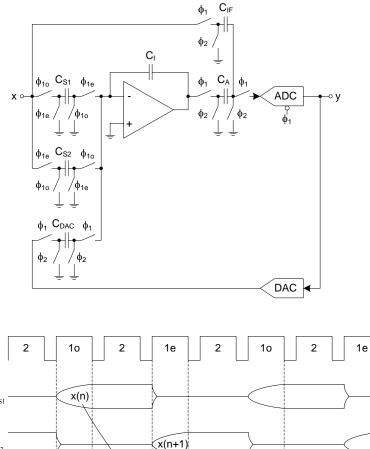

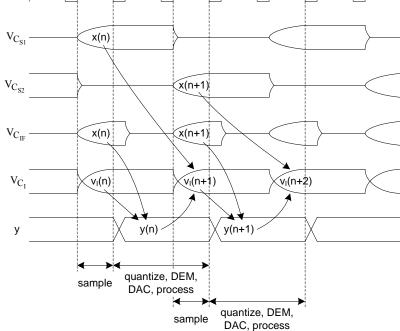

Consider the parasitic-insensitive switched-capacitor delaying integrator shown in Fig. A.1 where  $C_S$  is the sampling capacitor,  $C_I$  is the integrating capacitor,  $C_O$  is the total capacitor connected at the integrator output, and  $C_P$  is the total parasitic capacitor at the opamp input.

Fig. A.1: Switched-capacitor delaying integrator

With infinite opamp gain, bandwidth, and slew rate, the integrator has the following transfer function assuming ideal switches and with the output taken at the end of phase 1:

$$\frac{v_o}{v_i} = \frac{a \ z^{-1}}{1 - z^{-1}}$$

where a is the integrator coefficient  $(C_S/C_I)$ .

Finite opamp gain (A) introduces a gain error ( $\epsilon_a$ ) and a phase error ( $\epsilon_{\theta}$ ) which modifies the integrator transfer function as following:

$$\frac{v_o}{v_i} = \frac{a\left(1-\varepsilon_a\right)z^{-1}}{1-\left(1-\varepsilon_\theta\right)z^{-1}}$$

where:

$$\varepsilon_{a} = \frac{C_{I} + C_{S} + C_{P}}{(A+1)C_{I} + C_{S} + C_{P}} \approx \frac{1}{A\beta}$$

$$\varepsilon_{\theta} = \frac{C_{S}}{(A+1)C_{I} + C_{S} + C_{P}} \approx \frac{a}{A}$$

and  $\beta$  is the feedback factor  $C_I/(C_I+C_S+C_P)$ .

Next, consider finite opamp unity-gain frequency for a single stage opamp. A gain error  $(\varepsilon_u)$  is introduced in response to a step input:

$$\frac{v_o}{v_i} = \frac{a(1 - \varepsilon_u) z^{-1}}{1 - z^{-1}}$$

where:

$$\mathcal{E}_{u} = \left(1 + \frac{\tau_{z}}{\tau}\right) e^{-t_{settle}/\tau} \approx e^{-t_{settle}/\tau}$$

and:

$$\tau = 1/\omega_{-3dB}$$

$$\omega_{-3dB} = \beta \ \omega_u = \beta \ g_m/C_L$$

$$C_L = C_O + \beta \left(C_S + C_P\right)$$

$$\tau_z = C_I/g_m$$

where  $t_{settle}$  is the available settling time which is approximately half the period,  $g_m$  and  $\omega_u$  are the transconductance and the unity-gain frequency of the opamp respectively,  $\omega_{-3dB}$  is the integrator closed-loop bandwidth, and  $\tau_z$  is the time constant of the feedforward zero.

The phase error due to finite opamp gain and the gain error due to dynamic linear settling and static settling can be incorporated into the Simulink model for system level simulations. Circuit level design should make sure that slewing does not occur. Modern  $\Delta\Sigma$  modulators usually employ multi-bit internal quantizers, therefore, they are much less prone to get into slew limited region. Therefore, the incomplete linear settling strategy works well with multi-bit modulators. Furthermore, input-feedforward topologies have the least slew-rate requirement due to their small signal swings at the integrator outputs. Chapter 3:

### Time-Interleaved ΔΣ Modulators

**T**IME-INTERLEAVING is discussed in Chapter 2 as a method to add another degree of freedom to the design of  $\Delta\Sigma$  modulators. In this chapter a modified time-interleaved  $\Delta\Sigma$  modulator is introduced. The new modulator requires the same number of opamps used by traditional modulators but with more quantizers and interconnects paths. Since the new topology requires the same number of opamps regardless of the interleaving order, it is called the *single-path time-interleaved* (SPTI)  $\Delta\Sigma$  modulator. In contrast, traditional time-interleaved modulators require J-paths for an interleaving factor of J; therefore, they are referred to as the *multi-path time-interleaved* (MPTI)  $\Delta\Sigma$  modulators.

The SPTI modulator eliminates some of the problems the MPTI topology suffered from which are discussed in chapter 2. Specifically, the opamp DC offsets problem and the high speed demux at the modulator input are not present in the SPTI architecture. However, the critical path created due to the lack of delays between the output of a quantizer and the input of another is still present. A prediction technique to deal with the critical path in time-interleaved modulators was presented in [13]. This technique can be utilized in conjunction with the topologies in this chapter to alleviate the critical path problem.

The outline of this chapter is as follows: Section 3.1 introduces the derivation of the new time-interleaved modulator. Section 3.2 discusses the consequences of removing the analog demux at the input. Section 3.3 evaluates the new modulator. Section 3.4 investigates the mixed multi-path and single-path time-interleaved modulator as a possibility to alleviate some issues in the SPTI topology. Section 3.5 investigates a partial calibration scheme for the SPTI  $\Delta\Sigma$  modulator. Section 3.6 analyzes mismatch shaping in multi-bit SPTI modulators. Finally, the timing constraint in the SPTI is discussed in Section 3.7 and a possible solution is proposed.

#### 3.1 Single-Path Time-Interleaved ΔΣ Modulator Concept

The first SPTI modulator was reported in [14] where the concept of removing the high-speed input demux and feeding the input to all paths in the time-interleaved modulator was proposed. It

was shown later that removing the demux modifies the STF of the SPTI architecture [15]. More recently, a discrete-time SPTI modulator was reported in [13]. In addition to the single-path feature, some of the analog processing was transferred into the digital domain. This transfer eliminated the critical path issue discussed later in this chapter at the expense of requiring finer resolution quantizers.

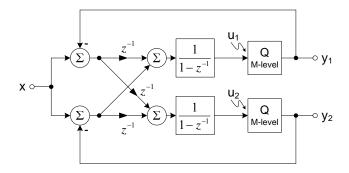

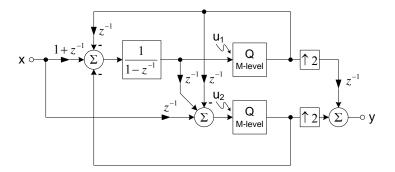

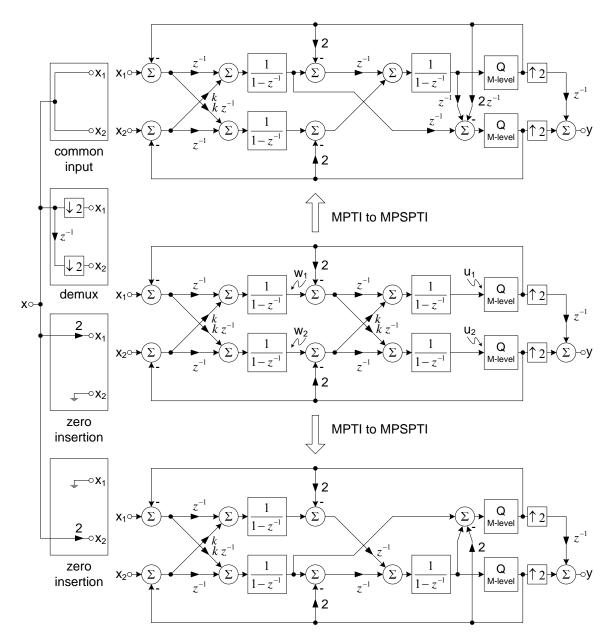

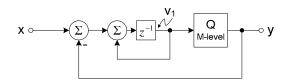

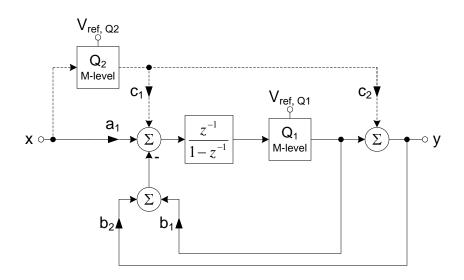

In this section, new SPTI discrete-time  $\Delta\Sigma$  modulators are presented. First-order SPTI modulators with an interleaving factor of 2 are developed as an illustration of the derivation procedure. The starting point of the derivation is the MPTI modulator [1] with the input demux removed and the input signal fed to both branches of the modulator [14] as shown in Fig. 3.1.

Fig. 3.1: MPTI  $\Delta\Sigma$  modulator without input demux

The inputs to the quantizers are needed later in the derivation process. They can be determined directly from the block diagram in Fig. 3.1:

$$u_{1} = \frac{1}{1 - z^{-1}} \left[ \left( 1 + z^{-1} \right) x - z^{-1} y_{1} - y_{2} \right]$$

(3-1)

$$u_{2} = \frac{1}{1 - z^{-1}} \Big[ 2z^{-1}x - z^{-1}y_{1} - z^{-1}y_{2} \Big]$$

(3-2)

The next step is to combine the two adders in the top path into a single adder as well as combining the two adders in the bottom path. With the combined adders, the modulator can be redrawn as shown in Fig. 3.2a. The rearranged modulator is split into two separate entities as shown in Fig. 3.2b. Therefore, if we can generate  $y_2$  from x,  $y_1$ , and  $u_1$ , the top branch can operate as a stand alone time-interleaved modulator. Similarly, if we can generate  $y_1$  from x,  $y_2$ , and  $u_2$ , the bottom branch can operate as a stand alone time-interleaved modulator.

Fig. 3.2: (a) MPTI  $\Delta\Sigma$  modulator without input demux rearranged (b) with top and bottom paths split

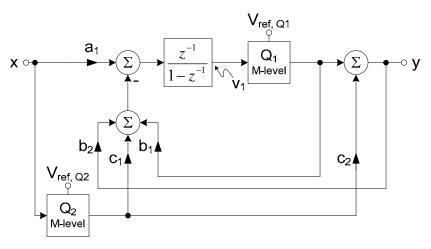

To generate a SPTI modulator from the bottom path, we can manipulate Eqs. (3-1) and (3-2). First, Solve Eq. (3-2) for  $y_1$ :

$$y_1 = z \left( 2z^{-1}x - z^{-1}y_2 - (1 - z^{-1})u_2 \right)$$

Next, substitute  $y_1$  into Eq. (3-1):

$$u_1 = x - y_2 + u_2$$

Since  $y_1$  is the quantized value of  $u_1$ :  $y_1$  can be generated from x,  $y_2$ , and  $u_2$  as desired. Therefore, the bottom path of Fig. 3.2b can be used as a time-interleaved modulator as shown in Fig. 3.3.

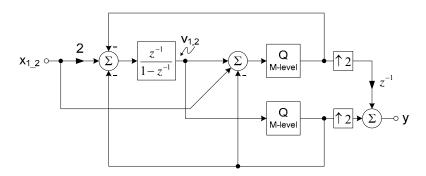

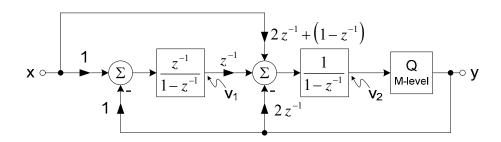

Fig. 3.3: SPTI  $\Delta\Sigma$  modulator with an interleaving factor of 2

Similarly, to generate a SPTI modulator from the top path, we solve Eq. (3-1) for  $y_2$  and substitute it into Eq. (3-2) to obtain:

$$u_2 = z^{-1}x - z^{-1}y_1 + z^{-1}u_1$$

Since  $y_2$  is the quantized value of  $u_2$ :  $y_2$  can be generated from x,  $y_1$ , and  $u_1$  as desired. Therefore, the top path of Fig. 3.2b can be used as a time-interleaved modulator as shown in Fig. 3.4.

Fig. 3.4: SPTI  $\Delta\Sigma$  modulator with an interleaving factor of 2

The input of the SPTI modulator in Fig. 3.4 can be simplified further by modifying the bilinear discrete-integrator to a delaying discrete-integrator. This means a loss of half the input signal and therefore must be compensated by increasing the input gain to 2. Using extensive Matlab simulations, the modulators in Fig. 3.3 and Fig. 3.4 have similar performance with and without non-idealities in their building blocks.

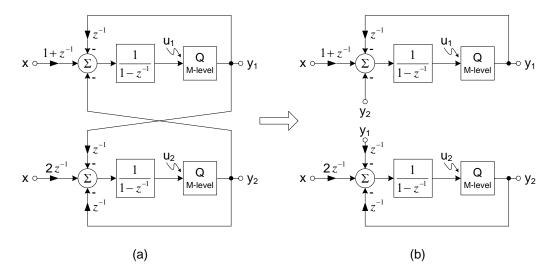

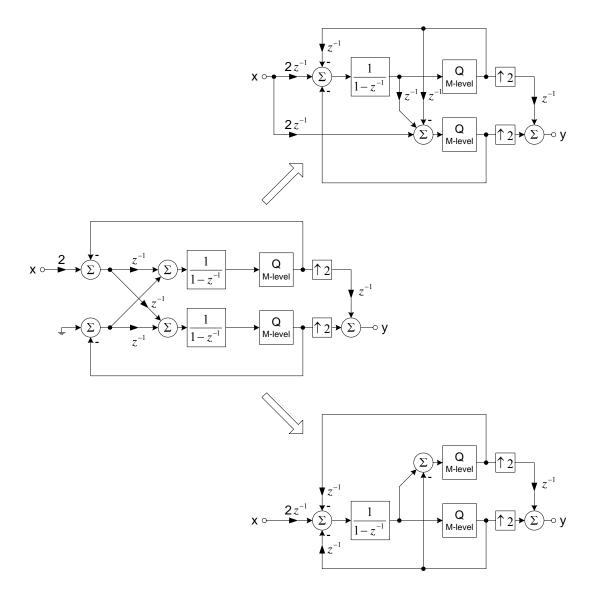

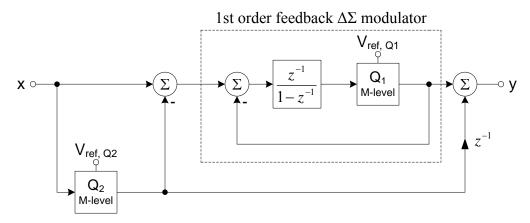

Additional SPTI discrete-time  $\Delta\Sigma$  modulators can be developed using the method presented above. The starting point of the derivation is the MPTI modulator [1] with the zero-insertion concept [12]. First-order SPTI modulators with an interleaving factor of 2 are derived as shown in Fig. 3.5 and Fig. 3.6. As discussed in chapter 2 however, the stable input-signal level is smaller for modulators with zero-insertion due to the amplification at the input by the interleaving factor.

Fig. 3.5: SPTI  $\Delta\Sigma$  modulators with an interleaving factor of 2

Fig. 3.6: SPTI  $\Delta\Sigma$  modulators with an interleaving factor of 2

The SPTI modulator has several advantages when compared to the MPTI modulator. First, it does not suffer from the DC offset problem like the traditional time-interleaved  $\Delta\Sigma$  modulator. In addition, the SPTI eliminates the high-speed analog demux at the input of the modulator while also using fewer opamps.

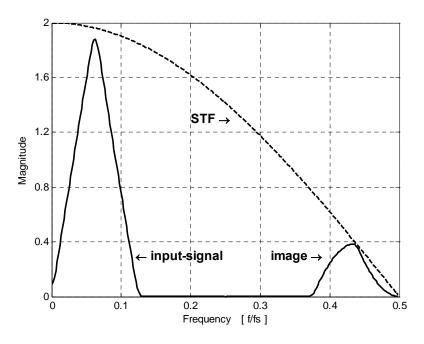

# 3.2 Effects of Removing the Demux

Removing the analog demux at the input has some consequences [15]. Analysis of the linearized system of Fig. 3.3 leads to the following results:

$$y = z^{-1} (1 + z^{-1}) x + z^{-1} (1 - z^{-1}) q_1 + (1 - z^{-1}) q_2$$

where  $q_1$  and  $q_2$  are the quantization noise from the top and bottom quantizers respectively. Due to the output mux, the quantization noise  $q_1$  is only added to the output once for every two samples, which is also true for  $q_2$ . Therefore, the overall noise contribution can be rewritten as:

$$NTF = \frac{y}{q} = \left(1 - z^{-1}\right)$$

which is simply first-order noise shaped. Clearly, the removal of the demux does not affect the NTF, however the STF is affected. The first term in the STF is  $z^{-1}$ , which is the expected STF of a first-order CIFB modulator. The second term  $(1 + z^{-1})$  resulted from the removal of the input demux. The extra term adds a notch at half the sampling frequency and filters the amplitude response of the STF as shown in Fig. 3.7. Due to oversampling, the frequency variation is not significant within the signal band.

Fig. 3.7: STF and imaging issue for SPTI

Another effect of removing the demux is that the signal is under the influence of the upsamplers only. The effect of upsampling by J is J-fold compression and repetition of the frequency-domain magnitude response [16]. The process generates images shaped by the STF at frequencies less than half the sampling frequency as shown in Fig. 3.7.

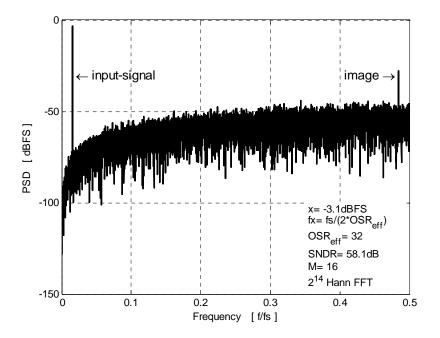

Fig. 3.8: Sample output spectrum for the SPTI of Fig. 3.3

A sample output spectrum of the SPTI modulator in Fig. 3.3 is shown in Fig. 3.8. It also highlights the shaped image of the input-signal.

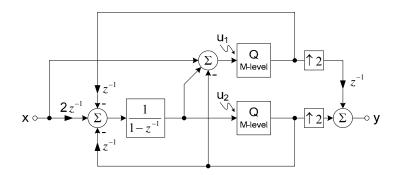

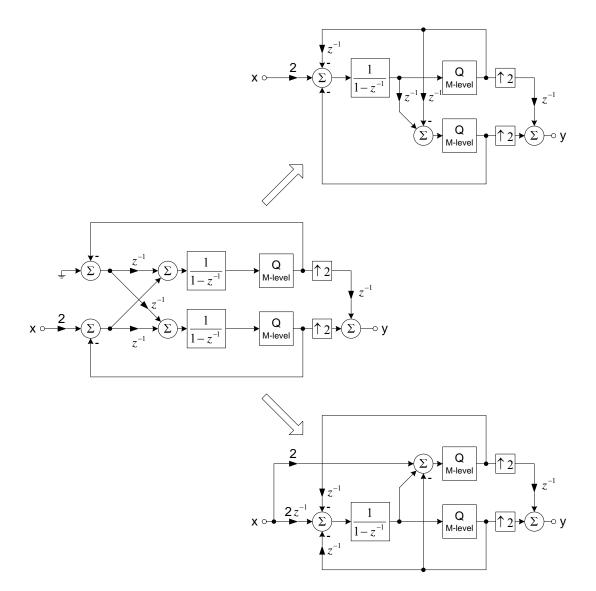

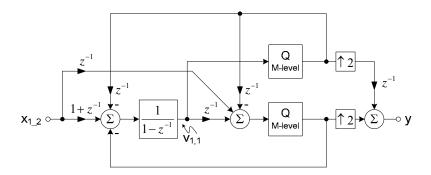

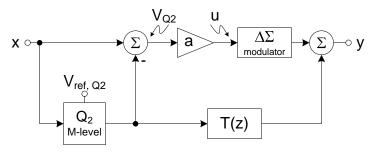

# 3.3 Evaluation of the SPTI ΔΣ Modulator

Several simulations using Matlab and Simulink are used to evaluate the performance of the new SPTI modulator and to compare it to traditional structures. The simulations use the second-order SPTI modulator shown in Fig. 3.9, the MPTI modulator shown in Fig. 2.11 with a k-factor of 1, and the traditional CIFB modulator shown in Fig. 2.1. The time-interleaved by 2 modulators are clocked at half the rate of the CIFB modulator. In other words, the oversampling ratio of the CIFB (OSR) and the effective oversampling ratio of the SPTI and MPTI (OSR<sub>eff</sub>) are equal, hence, their expected SNDR is the same.

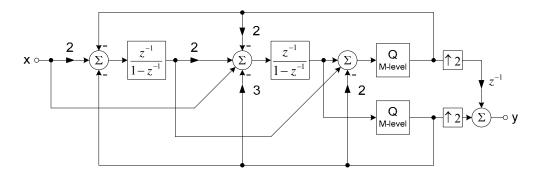

Fig. 3.9: Second-order SPTI  $\Delta\Sigma$  modulator with interleaving factor of 2

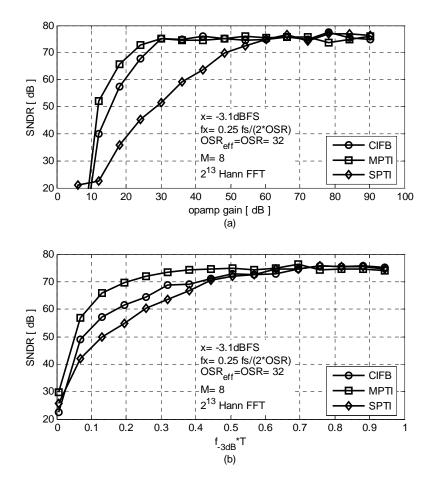

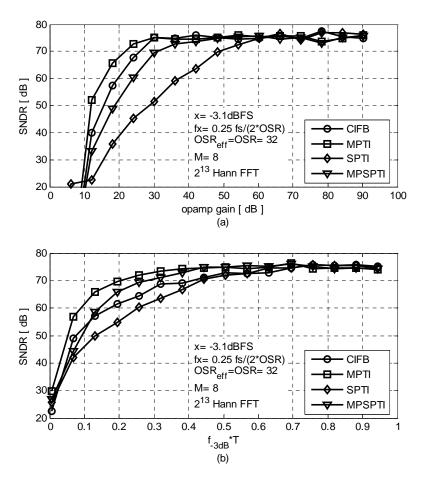

The modulators are simulated taking into account the effects of finite gain and bandwidth in the opamps. The second stage integrator opamp has 5% less gain and bandwidth than those in the first stage. In addition, a 2% mismatch between the two paths of the MPTI modulator is considered. The results are summarized in Fig. 3.10 where  $f_{-3dB}$  is the closed-loop -3 dB bandwidth of the opamp.

Fig. 3.10: SNDR versus (a) opamp gain (b) normalized bandwidth

We can observe that the MPTI requires less opamp gain and bandwidth than the CIFB which is close to the prediction in [1]. On the other hand, the SPTI requires much larger opamp gain and bandwidth to achieve the same SNDR as the CIFB even though it is clocked at half the clock speed.