### VLSI Architectures for Multi-GBPS Low-Density Parity-Check Decoders

by

Ahmad Darabiha

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy Graduate Department of Electrical and Computer Engineering University of Toronto

© Copyright by Ahmad Darabiha 2008

#### VLSI Architectures for Multi-GBPS Low-Density Parity-Check Decoders

Ahmad Darabiha

Doctor of Philosophy, 2008 Graduate Department of Electrical and Computer Engineering University of Toronto

#### Abstract

Near-capacity performance and parallelizable decoding algorithms have made Low-Density Parity Check (LDPC) codes a powerful competitor to previous generations of codes, such as Turbo and Reed Solomon codes, for reliable high-speed digital communications. As a result, they have been adopted in several emerging standards. This thesis investigates VLSI architectures for multi-Gbps power and area-efficient LDPC decoders.

To reduce the node-to-node communication complexity, a decoding scheme is proposed in which messages are transferred and computed bit-serially. Also, a broadcasting scheme is proposed in which the traditional computations required in the sum-product and min-sum decoding algorithms are repartitioned between the check and variable node units. To increase decoding throughput, a block interlacing scheme is investigated which is particularly advantageous in fully-parallel LDPC decoders. To increase decoder energy efficiency, an efficient early termination scheme is proposed. In addition, an analysis is given of how increased hardware parallelism coupled with a reduced supply voltage is a particularly effective approach to reduce the power consumption of LDPC decoders.

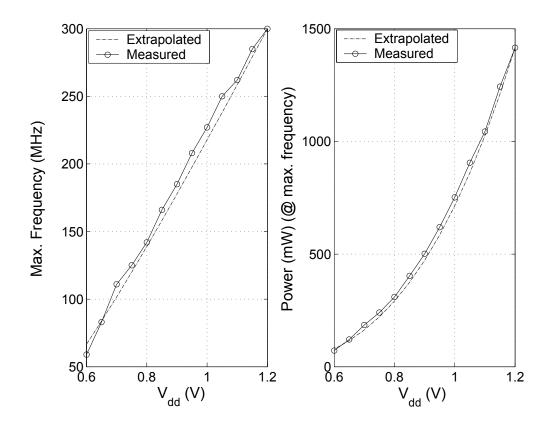

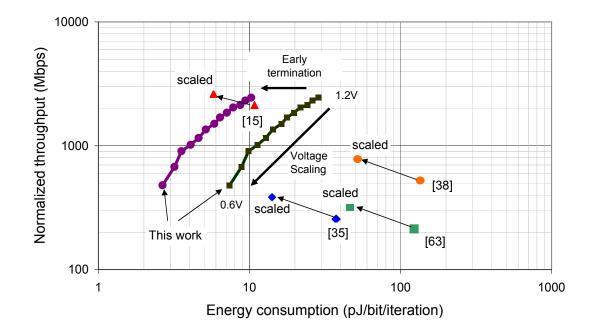

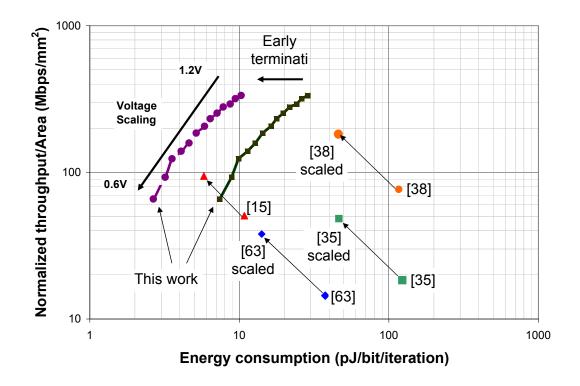

These architectures and circuits are demonstrated in two hardware implementations. Specifically, a 610-Mbps bit-serial fully-parallel (480, 355) LDPC decoder on a single Altera Stratix EP1S80 device is presented. To our knowledge, this is the fastest FPGA-based LDPC decoder reported in the literature. A fabricated 0.13- $\mu$ m CMOS bit-serial (660, 484) LDPC decoder is also presented. The decoder has a 300 MHz maximum clock frequency and a 3.3 Gbps throughput with a nominal 1.2-V supply and performs within 3 dB of the Shannon limit at a BER of  $10^{-5}$ . With more than 60% power saving gained by early termination, the decoder consumes 10.4 pJ/bit/iteration at  $E_b/N_0$ =4dB. Coupling early termination with supply voltage scaling results in an even lower energy consumption of 2.7 pJ/bit/iteration with 648 Mbps decoding throughput.

The proposed techniques demonstrate that the bit-serial fully-parallel architecture is preferred to memory-based partially-parallel architectures, both in terms of throughput and energy efficiency, for applications such as 10GBase-T which use medium-size LDPC code (e.g., 2048 bit) and require multi-Gbps decoding throughput.

#### Acknowledgment

I feel truly honored for having the chance to work with Prof. Anthony Chan Carusone and Prof. Frank R. Kschischang as my Ph.D. advisors. I would like to thank them both for their academic and personal mentorship throughout this work. The completion of this project would not have been possible without Tony's continuous support, guidance, dedication and friendship. I have also learned so much from Frank's insightful research approach, skillful teaching methods, and his inspiring weekly group meetings.

I thank the members of my PhD supervising committee, Prof. Glenn Gulak and Prof. Roman Genov, for their insightful suggestions during the entire course of this work. I also thank the external members of my final oral examination, Prof. Wei Yu and Prof. Bruce F. Cockburn, for their time and for their valuable comments.

I gratefully acknowledge access to fabrication and CAD tools from Gennum Corporation. I also thank the FPGA research group at UofT for providing access to the Transmogrifier-4 prototype board.

I am grateful beyond measures to my dear parents, Mohammad Karim and Saeedeh, who have been my best teachers in countless ways. This thesis is dedicated to them, in the hope to acknowledge a tiny fraction of their unconditional and everlasting love and support.

I thank my lovely sister, Ladan, and my dear brothers, Mehdi and Majid, who have been my constant source of encouragement even though we have been more than eight time zones away for most of the past few years. I also thank my uncles and their dear families in Mississauga. Their kindness and hospitality have always made me feel like being close to home.

And last, but definitely not least, I feel blessed for getting to know so many good friends during my studies at UofT. I have learned a lot from them and I am grateful to them all. I thank Kostas Pagiamtzis, for being the most fun and knowledgeable cubicle mate I could ever hope for. Special thanks to Samira Naraghi for her invaluable and friendly consultations when they were badly needed. Many thanks to Amir Azarpazhooh for his true friendship (and for paying (most of) his dues in 'The wood game'!). Special thanks goes to Farsheed Mahmoudi for his energizing 'Zoor Khooneh' spirit. I also thank other friends from LP392, BA5000, BA5158, Tony's group, Frank's group, and those from outside the department. In particular, I would like to thank Rubil Ahmadi, Mohamed Ahmed Youssef Abdulla, Masoud Ardakani, Navid Azizi, Mike Bichan, Horace Cheng, Yadi Eslami, Tooraj Esmailian, Vincent Gaudet, Amir Hadji-Abdolhamid, Afshin Haftbaradaran, Mohammad Hajirostam, Meisam Honarvar, Farsheed Mahmoudi, Mahsa Moallem, Alireza Nilchi, Ali Pakzad, Peter Park, Jennifer Pham, Mohammad Poustinchi, Saman Sadr, Sanam Sadr, Siamak Sarvari, Mahdi Shabany, Mehrdad Shahriari, Farzaneh Shahrokhi, Tina Tahmoures-zadeh, Maryam Tohidi, Alexi Tyshchenko, Marcus van Ierssel, and Kentaro Yamamoto, in the alphabetical order.

# Contents

| Lis | st of Figures                                                                                                                                                                                                                                                                                                                                                           | ix                                                      |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Lis | st of Tables                                                                                                                                                                                                                                                                                                                                                            | xiii                                                    |

| 1   | Introduction1.1Error Control Codes1.2Outline                                                                                                                                                                                                                                                                                                                            |                                                         |

| 2   | Low-Density Parity-Check (LDPC) Codes         2.1       Code Structure         2.2       LDPC Decoding Algorithms         2.2.1       Sum-product algorithm         2.2.2       Min-sum algorithm         2.3       Capacity-Approaching LDPC Codes         2.4       Decoder Implementation         2.5       Architecture-Aware LDPC Codes         2.6       Overview | 9         9         11         12         13         11 |

| 3   | Reducing Interconnect Complexity         3.1       Half-broadcasting                                                                                                                                                                                                                                                                                                    | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$   |

| 4   | Block-Interlaced Decoding         4.1       Background         4.2       Interlacing         4.3       Implementations         4.3.1       Design 1: (2048, 1723) RS-based LDPC decoders         4.3.2       Design 2: (660, 484) PEG LDPC decoders         4.3.3       Results                                                                                         |                                                         |

| 5   | Power-Saving Techniques for LDPC Decoders5.1Parallelism and Supply-Voltage Scaling5.1.1Background                                                                                                                                                                                                                                                                       |                                                         |

| Re | References          |                                                         |            |  |  |

|----|---------------------|---------------------------------------------------------|------------|--|--|

| В  | Pari                | ty-Check Matrix for 0.13- $\mu$ m CMOS Decoder          | 103        |  |  |

| Α  | Pari                | ty-Check Matrix for FPGA-Based Decoder                  | 97         |  |  |

| Ap | ppend               | lices                                                   | 97         |  |  |

|    |                     | 7.3.5 Adjustable message word length                    | 95         |  |  |

|    |                     | 7.3.4 Hardware-based Gaussian noise generation          | 95         |  |  |

|    |                     | 7.3.3     Custom layout for sub-blocks                  | 94<br>94   |  |  |

|    |                     | 7.3.2 Multi-rate and multi-length decoders              | 93<br>94   |  |  |

|    | 6.5                 | Future Work    7.3.1      Technology scaling    7.1     | 93<br>93   |  |  |

|    | $7.2 \\ 7.3$        | Conclusions                                             | $92 \\ 93$ |  |  |

|    | 7.1                 | Summary                                                 | 91         |  |  |

| 7  |                     | clusions and Future Work                                | 91         |  |  |

|    |                     | 6.4.2 A 0.13- $\mu$ m CMOS 660-bit bit-serial decoder   | 79         |  |  |

|    |                     | 6.4.1 An FPGA 480-bit LDPC decoder                      | 77         |  |  |

|    | 6.4                 | Implementations                                         | 77         |  |  |

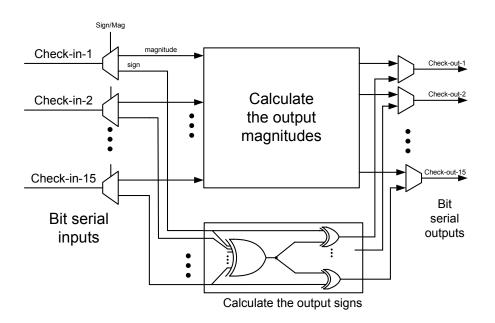

|    |                     | 6.3.2 CNU architecture for approximate Min-Sum decoding | 75         |  |  |

|    |                     | 6.3.1 Approximate Min-Sum decoding                      | 73         |  |  |

|    | 6.3                 | Bit-Serial Blocks for Approximate Min-Sum Decoding      | 73         |  |  |

|    |                     | 6.2.2 VNU architecture                                  | 70         |  |  |

|    | 0.2                 | 6.2.1 CNU architecture                                  | 66         |  |  |

|    | 6.2                 | Bit-serial Blocks for Conventional Min-Sum Decoding     | 66         |  |  |

| 6  | <b>Б</b> ІІ-<br>6.1 | Serial Message-Passing Motivation                       | 63         |  |  |

| 6  | D:+                 | Seviel Messere Dessing                                  | 63         |  |  |

|    | 5.3                 | Power vs. BER Performance                               | 59         |  |  |

|    |                     | 5.2.3 Hardware implementation                           | 57         |  |  |

|    |                     | 5.2.2 Early termination                                 | 53         |  |  |

|    | 0.2                 | 5.2.1 Background                                        | 52         |  |  |

|    | 5.2                 | LDPC Decoding With Early Termination                    | 40<br>52   |  |  |

|    |                     | 5.1.2 Analysis                                          | 48         |  |  |

# List of Figures

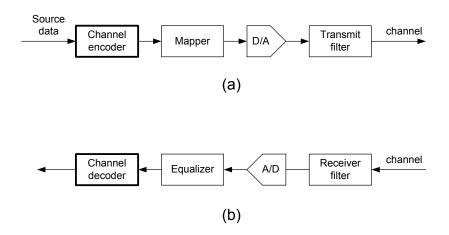

| 1.1          | An example communication system with ECC coding: (a) the trans-<br>mitter, (b) the receiver                                                                                                         | 2                   |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

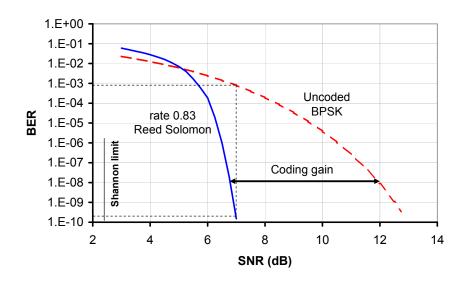

| 1.2          | The effect of ECC on BER performance.                                                                                                                                                               | 3                   |

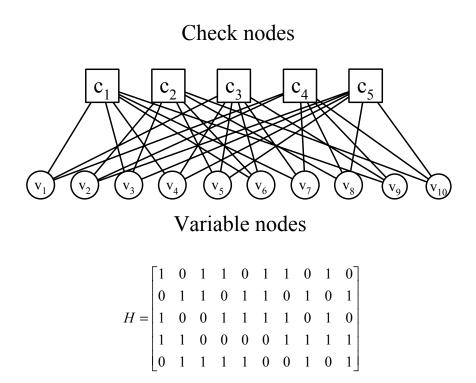

| 2.1          | Tanner graph for a (3,6)-regular LDPC code and the corresponding parity check matrix.                                                                                                               | 8                   |

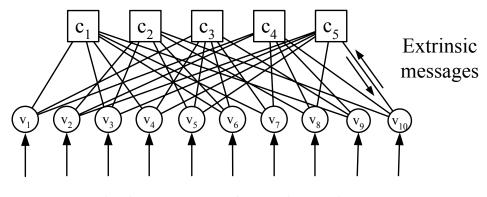

| $2.2 \\ 2.3$ | <ul><li>Exchange of information in a message-passing decoding algorithm</li><li>(a) Conventional receiver with digital ECC decoder, (b) An alternative</li></ul>                                    | 10                  |

| 2.4          | receiver with analog decoder.       A partially-parallel LDPC decoder.                                                                                                                              | 13<br>16            |

| 2.5          | The fully-parallel iterative LDPC decoder architecture.                                                                                                                                             | 16                  |

| 3.1          | A conventional fully-parallel message-passing LDPC decoder with generic functions for check and variable nodes.                                                                                     | 20                  |

| 3.2          | A half-broadcast architecture. The check node $c_m$ broadcasts a single message, $P_m$ , to all neighboring variable nodes.                                                                         | 22                  |

| 3.3          | Broadcasting reduces the total top-level wirelength by sharing the wires. (a) Output messages of a check node without broadcasting (b) Sharing interconnect wires of a check node with broadcasting | 23                  |

| 3.4          | A small section of interconnects for a length-2048 LDPC code (a) before broadcast (b) after broadcast. There is 40% reduction in total wirelength.                                                  | 23                  |

| 3.5          | The routed nets for one check node output highlighted in a fully-<br>parallel LDPC decoder layout: (a) without broadcasting and (b) with                                                            |                     |

| 3.6          | (a) The CNU and (b) the VNU architectures for a conventional hard                                                                                                                                   | 24                  |

|              | decision message-passing decoder with no broadcasting                                                                                                                                               | 26                  |

| 3.7          | (a) The CNU and (b) the VNU architectures for a hard decision message-<br>passing decoder with half broadcasting                                                                                    | 27                  |

| 3.8          | A full-broadcast architecture. The check node $c_m$ broadcasts $P_m$ to the neighboring variable nodes. The variable node $v_n$ broadcasts $S_n$                                                    | 29                  |

| 4.1          | An example of row/column permutation of $H$ matrix in overlapped<br>message-passing [1]: (a) the original $H$ matrix, (b) the permuted $H$                                                          | <i>c</i> , <i>i</i> |

|              | matrix                                                                                                                                                                                              | 34                  |

| 4.2  | Message-passing timing diagram for (a) the original matrix of Fig. 4.1.a<br>(b) for the permuted matrix of Fig. 4.1.b.               | 35 |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----|

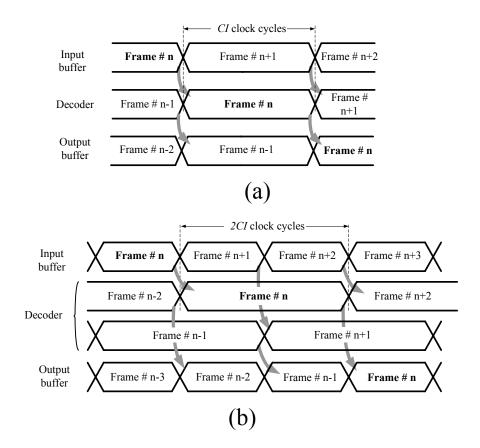

| 4.3  | A timing diagram for the message-passing algorithm: (a) conventional<br>(b) overlapped message passing [1] (c) block interlacing     | 36 |

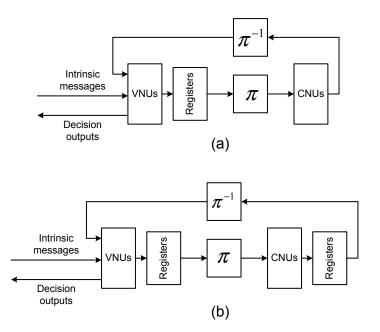

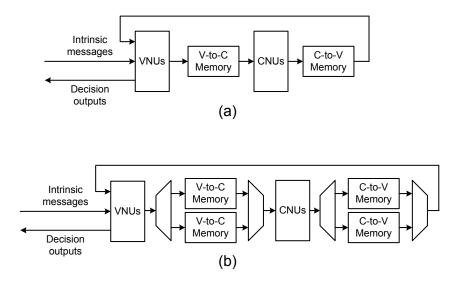

| 4.4  | (a) conventional, and (b) block-interlaced architecture for fully-parallel LDPC decoders.                                            | 37 |

| 4.5  | (a) conventional, and (b) block-interlaced architecture for partially-<br>parallel LDPC decoders.                                    | 38 |

| 4.6  | (a) CNU, and (b) VNU for the block-interlaced LDPC decoder in Design 1B.                                                             | 40 |

| 4.7  | Timing diagram for (a) Design 1A, (b) Design 1B (with block interlacing).                                                            | 41 |

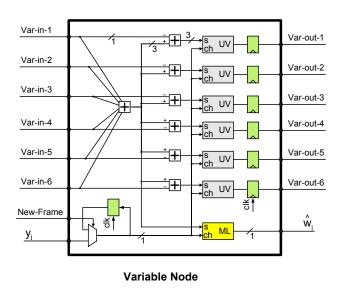

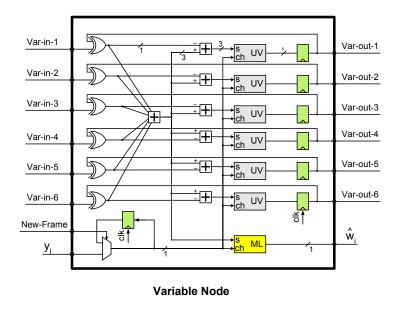

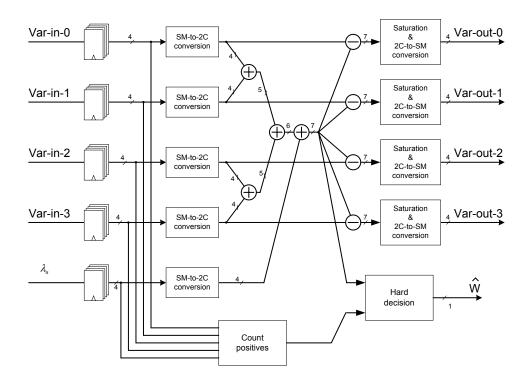

| 4.8  | VNU for the fully-parallel LDPC decoders in Designs 2A and 2B                                                                        | 42 |

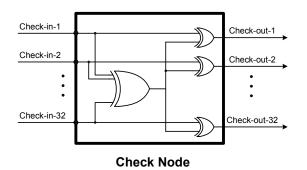

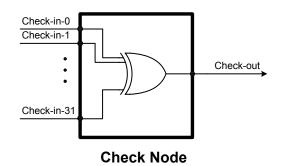

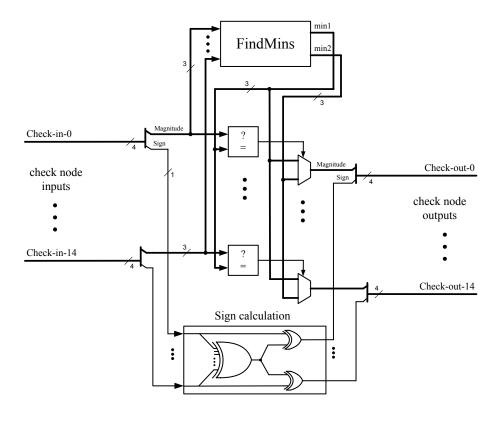

| 4.9  | CNU for the fully-parallel LDPC decoder in Designs 2A                                                                                | 43 |

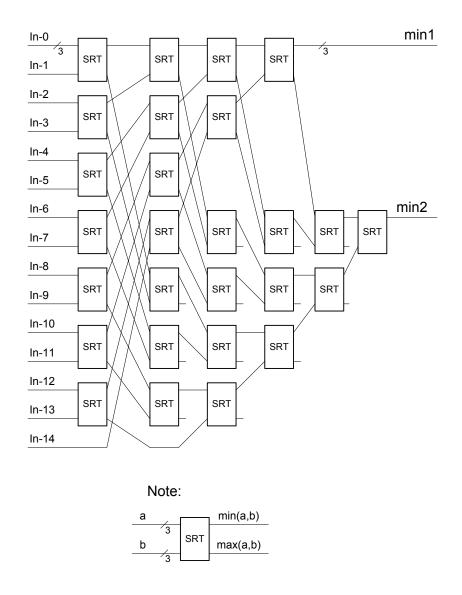

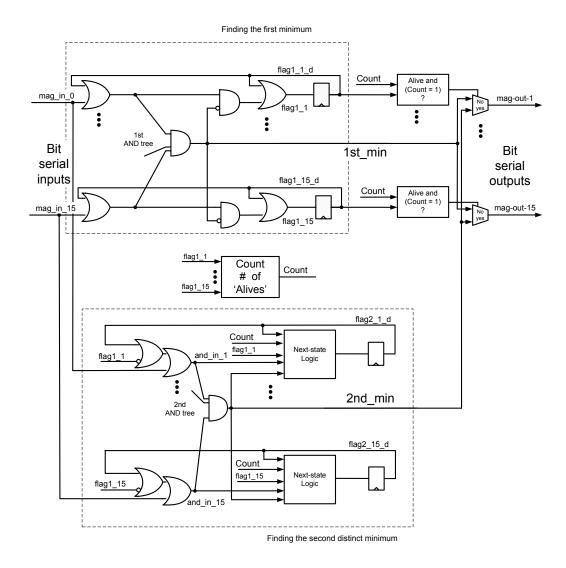

| 4.10 | The FindMins block to calculate the first and second minimums (i.e., min1 and min2) in Fig. 4.9                                      | 44 |

|      |                                                                                                                                      | 11 |

| 5.1  | A partially-parallel LDPC decoder.                                                                                                   | 48 |

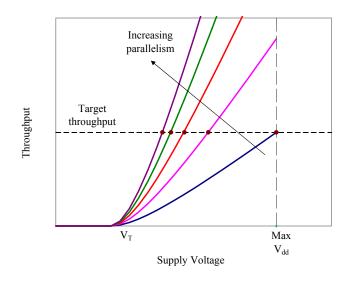

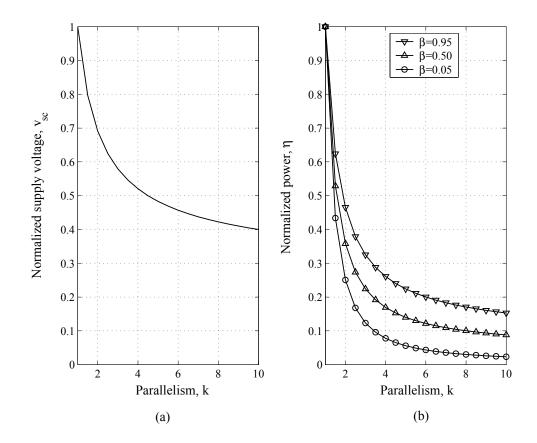

| 5.2  | Increased parallelism allows reduced supply voltage                                                                                  | 49 |

| 5.3  | Power reduction as a result of a parallel architecture: a) Reduction in supply voltage. b) Reduction in dynamic power dissipation.   | 51 |

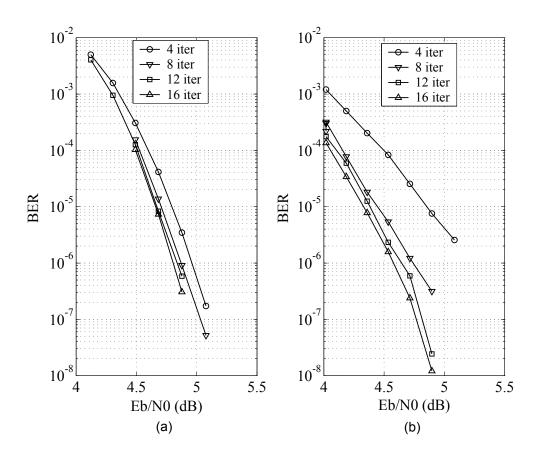

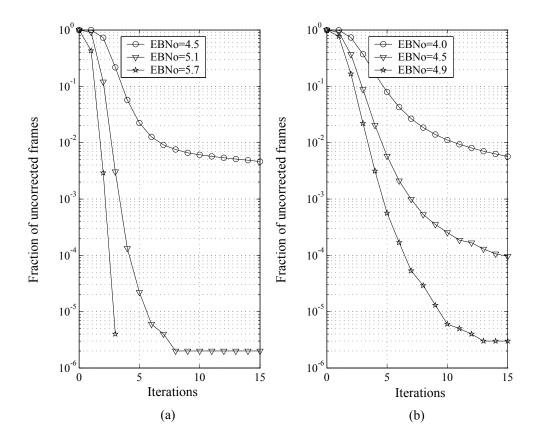

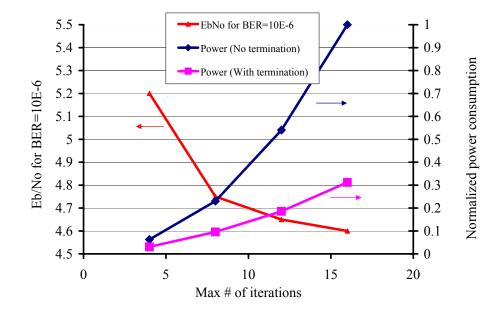

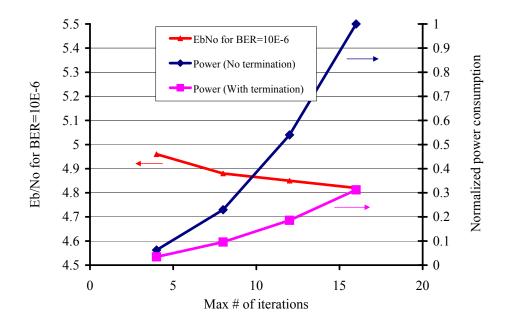

| 5.4  | BER vs. maximum number of iterations under 4-bit quantized min-<br>sum decoding: (a) Reed-Solomon based (6,32)-regular 2048-bit code |    |

| 5.5  | and (b) PEG (4,15)-regular 660-bit code                                                                                              | 54 |

| 0.0  | Solomon based (6,32)-regular 2048-bit code. (b) a PEG (4,15)-regular 660-bit code.                                                   | 55 |

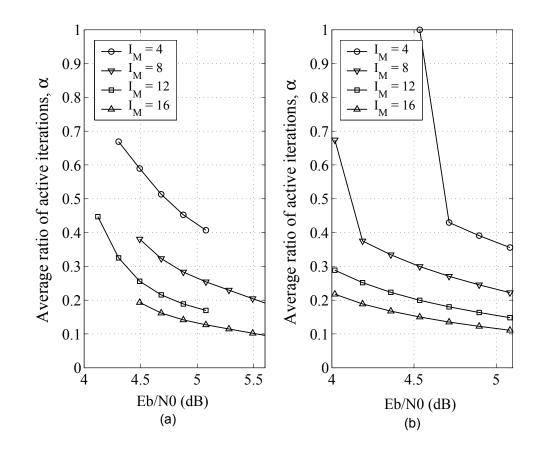

| 5.6  | Fraction of active iterations (a) Reed-Solomon based (6,32)-regular                                                                  | 00 |

|      | 2048-bit code and (b) PEG (4,15)-regular 660-bit code. $\ldots$ $\ldots$                                                             | 56 |

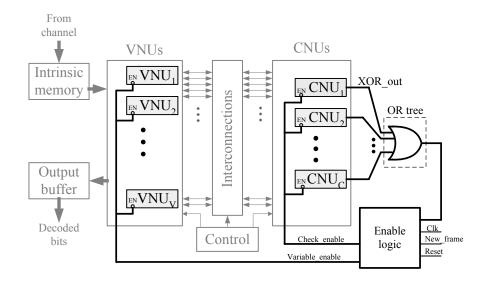

| 5.7  | The fully-parallel iterative LDPC decoder with early termination func-<br>tionality.                                                 | 58 |

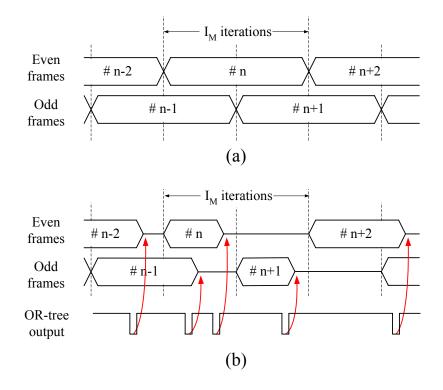

| 5.8  | Block-interlaced decoding timing diagram (a) without early termina-                                                                  |    |

|      | tion, (b) with early termination                                                                                                     | 59 |

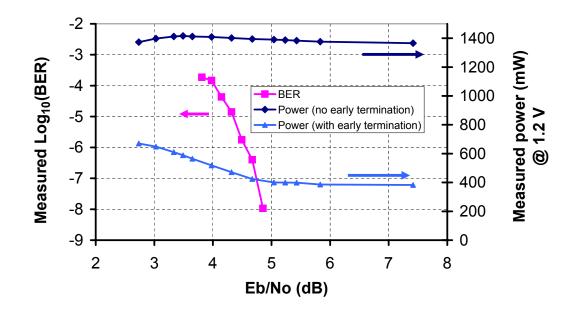

| 5.9  | The effect of $I_M$ on BER and power performance under a fixed decoding throughput for the (660, 484) PEG LDPC code                  | 60 |

| 5.10 | The effect of $I_M$ on BER and power performance under a fixed decoding throughput for the RS-based (2048, 1723) LDPC code           | 61 |

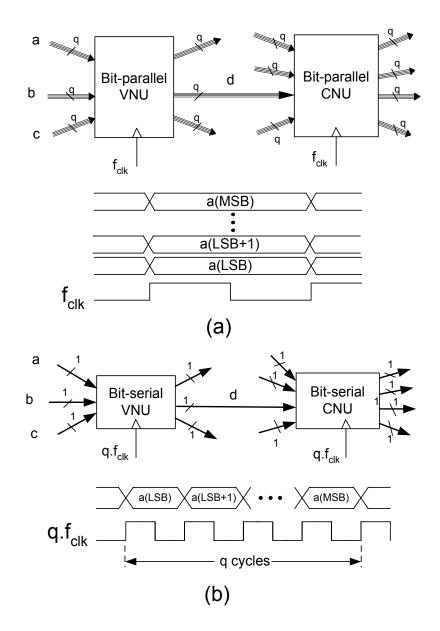

| 6.1  | Bit-serial vs. bit-parallel message passing.                                                                                         | 64 |

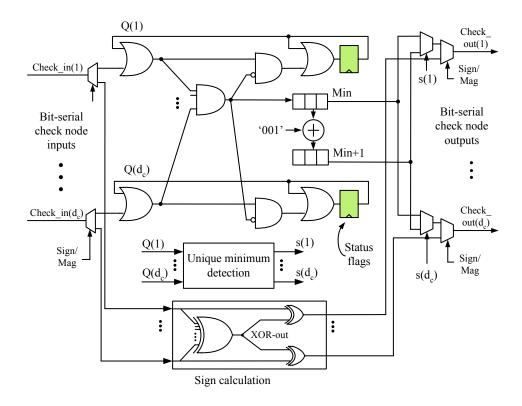

| 6.2  | Top-level diagram for a bit-serial CNU                                                                                               | 66 |

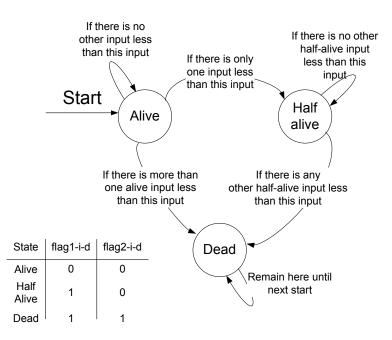

| 6.3  | The finite-state machine for bit-serial calculation of CNU output mag-<br>nitudes in a conventional min-sum decoder                  | 67 |

| 6.4  | The magnitude calculation module for the CNU in Fig. 6.2                                                                             | 69 |

|      |                                                                                                                                      |    |

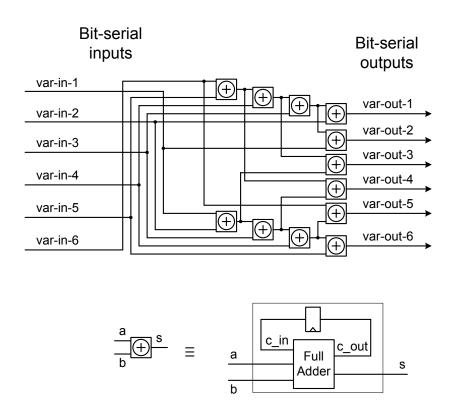

| 6.5  | A degree-6 VNU for computing (2.7) with a forward-backward archi-       |    |

|------|-------------------------------------------------------------------------|----|

|      | tecture [2]. Each adder box consists of a full-adder and a flip-flop to |    |

|      | store the carry from the previous cycle                                 | 70 |

| 6.6  | A VNU architecture for computing (2.7) with parallel adders and         |    |

|      | parallel-serial converters at the inputs and outputs                    | 71 |

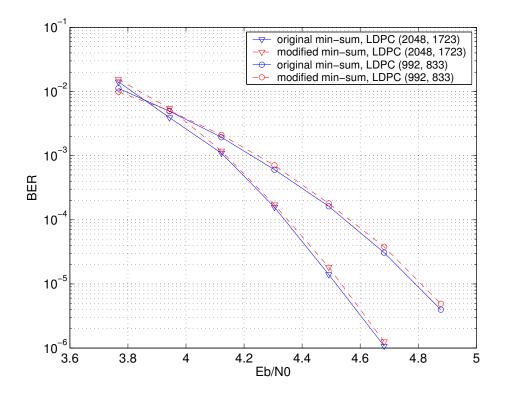

| 6.7  | Comparison between original min-sum and modified min-sum under          |    |

|      | full-precision operations for (2048, 1723) and (992, 833) LDPC codes.   | 74 |

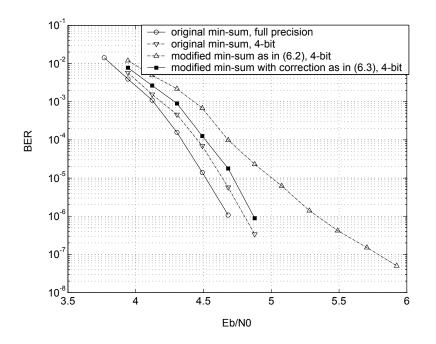

| 6.8  | Comparison between the original min-sum and modified min-sum as         |    |

|      | in (6.2) and (6.3) under fixed-point operations for (2048, 1723) LDPC   |    |

|      | code                                                                    | 75 |

| 6.9  | A bit-serial module for detecting the minimum magnitude of the check    |    |

|      | node inputs                                                             | 76 |

| 6.10 | A fully-parallel LDPC decoder.                                          | 77 |

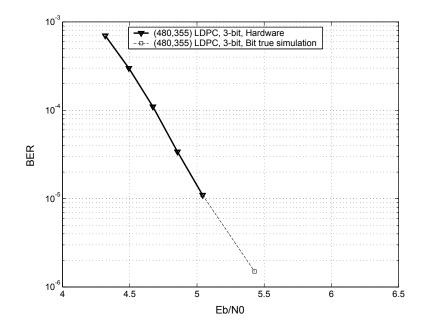

| 6.11 | FPGA hardware BER results and bit-true software simulation              | 78 |

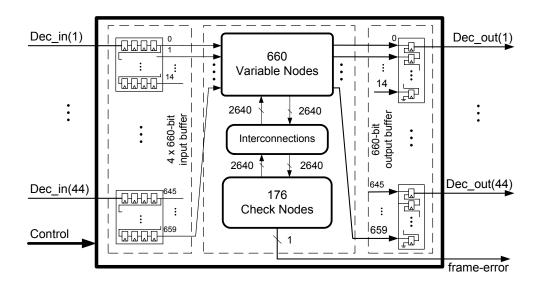

| 6.12 | The top-level block diagram for the (660, 484) LDPC decoder             | 80 |

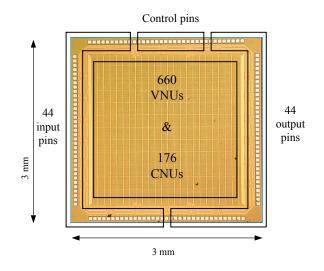

| 6.13 | Die photo of the (660, 484) LDPC decoder                                | 81 |

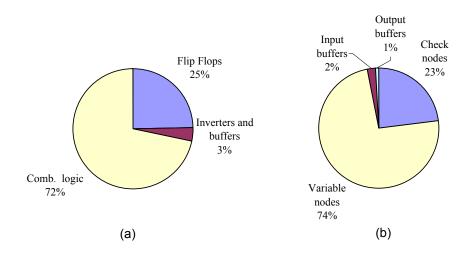

| 6.14 | Gate area breakdown for (a) cell types, (b) module types                | 82 |

| 6.15 | Measured power and BER for the fabricated 660-bit decoder               | 83 |

| 6.16 | Maximum operating frequency and the corresponding power dissipa-        |    |

|      | tion vs. supply voltage                                                 | 84 |

| 6.17 | Comparison with other works. The effect of early shut-down and sup-     |    |

|      | ply voltage scaling on power consumption is illustrated                 | 87 |

| 6.18 | Comparison with other works with decoder area also reflected on the     |    |

|      | vertical axis                                                           | 88 |

# List of Tables

| 3.1 | The average wirelength reduction for global nets in fully-parallel LDPC decoders.                                                                  | 25  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | Summary of LDPC decoder characteristics                                                                                                            | 45  |

| 6.1 | Comparison between the variable node architectures of Fig. 6.5 (forward-<br>backward) and Fig. 6.6 (parallel adder/subtracters) with $d_v = 6$ and |     |

|     | 3-bit quantization synthesized with CMOS 90-nm library cells                                                                                       | 72  |

| 6.2 | (480, 355) RS-based LDPC decoder implementation results                                                                                            | 79  |

| 6.3 | Characteristics summary and measured results.                                                                                                      | 85  |

| 6.4 | Comparison with other works                                                                                                                        | 86  |

| A.1 | The (4, 15)-regular (480, 355) LDPC code                                                                                                           | 97  |

| B.1 | The $(4, 15)$ -regular $(660, 484)$ LDPC code                                                                                                      | 103 |

## **1** Introduction

#### 1.1 Error Control Codes

The objective in this work is to investigate VLSI architectures for high-throughput power-efficient low-density parity-check (LDPC) decoders for applications such as fiber-optic communications and 10 Gbps Ethernet. LDPC codes are a sub-class of linear error control codes (ECC) [3]. Error control coding—also referred to as channel coding—is a powerful technique in digital communications for achieving reliable communication over an unreliable channel. ECC has evolved significantly since the advent of information theory by Shannon in 1948 [4] and has become an essential transceiver block in a wide range of applications. Error control codes have received a lot of attention recently due to two main reasons. First, significant progress has been made by the information theory community in designing capacity-approaching codes. Second, progress in VLSI technology has enabled the implementation of computationallyintensive decoding algorithms.

Figure 1.1 shows block diagrams of a generic transmitter and receiver in a communication system incorporating channel coding. The encoder module in the transmitter maps the input sequence of information bits into codewords that include some redundancy. The task of the decoder block in the receiver is to use the redundancy added by the encoder to detect and correct the errors induced in the channel.

Fig. 1.2 illustrates the effect of channel coding on the bit error rate (BER) performance of a communication system. In this figure, the dotted curve corresponds to an uncoded system whereas the solid curve corresponds to a system with a (256, 215) Reed Solomon code [5]. Both of the curves assume a BPSK modulated signal and an Additive White Gaussian Noise (AWGN) channel. The figure shows that for the same input SNR, the channel coding can significantly reduce the output BER compared to an uncoded scheme. As an example, for the case in Fig. 1.2, the BER is reduced from  $10^{-3}$  in the uncoded BPSK scheme to less than  $10^{-9}$  with the coded scheme for

Figure 1.1: An example communication system with ECC coding: (a) the transmitter, (b) the receiver.

an input SNR of about 7 dB. Similarly, the ECC code can reduce the required input SNR to achieve the same output BER. For example, the uncoded coding scheme in Fig. 1.2 requires an SNR of about 12 dB for BER of  $10^{-8}$  whereas the RS code can have the same BER with less than 7 dB of input SNR.

Several families of error control codes have been developed over the past few decades. Reed-Solomon (RS) codes [6] are now being extensively used in Compact Disks, DVD players, hard drives and long-haul optical communications to protect the information bits against the storage and communication errors. Deep space satellite communications and 3G-wireless are also widely using another powerful family of codes called Turbo codes [7].

In the past decade, LDPC codes have been found with superior error correction performance than Turbo codes. Although LDPC codes were originally introduced by Gallager in 1960's [3], they were not further explored until 1990's [8] due to their complex decoding hardware at the time. In [9] an LDPC code of length one million was designed which performed within 0.13 dB of the theoretical Shannon limit at a BER of  $10^{-6}$ . In [10] it was shown that a regular LDPC code with a modest length of 2048 bits

Figure 1.2: The effect of ECC on BER performance.

can also perform within only 1.5 dB of the Shannon limit. In addition to excellent BER performance, the decoding algorithm used to decode LDPC codes is highly parallel, providing the potential for very high decoding throughputs. Furthermore, thanks to Gallager's early publication of LDPC codes, their use is not restricted by patents, unlike Turbo codes [11]. Because of the above three reasons, LDPC codes have recently been adopted for different digital communication standards, including the European Digital Satellite Broadcast standard [12] in 2004 and 10-Gbit Ethernet wireline standard (IEEE802.3an) [13] in 2005. The recent Mobile WiMAX standard (IEEE802.16e) [14] also suggests LDPC codes as an optional error correction scheme.

For LDPC codes, the decoding process is typically more challenging than the encoding process. Whereas the encoding can be done in a non-iterative fashion, the decoding is usually an iterative process comprising computationally-intensive operations on soft-information. One iterative decoding algorithm commonly used for LDPC codes is called message-passing decoding. The algorithm operates on a set of "messages" each of which represents the decoder's belief about the value of a received bit. In each message-passing iteration, the algorithm refines the messages by considering known constraints imposed by the encoder on the data. For LDPC codes, the message-passing algorithm is highly parallel as there are typically a large number of messages which can be updated independently.

Hardware implementations of LDPC decoders may be categorized into two main groups: partially-parallel and fully-parallel. Although the fully-parallel architecture potentially provides the highest throughput, most of the decoders reported so far have focused on partially-parallel architecture where a number of shared processing units are used for updating the messages in each iteration. This is mainly due to two reasons. First, a fully-parallel decoder occupies a large area due to the large number of required processing units [15]. Second, due to the random structure of LDPC code graphs, the processing nodes in a fully-parallel decoder must communicate over a large and irregular network. This results in a large number of long and random wires across the decoder chip required to convey the messages between nodes. The complex interconnect in turn results in routing congestion and degrades the timing performance. In partially-parallel decoders, the large and irregular network of nodeto-node communication translates into large and power-hungry memory and address generation circuitry.

The goal in this work is to develop LDPC decoders with high energy efficiency and multi-Gbps decoding throughput while occupying practical chip area. As described above, a major challenge in implementing high-throughput decoders is the complexity of the node-to-node communications. We will propose a technique that reduces the decoder's node-to-node communication complexity by re-formulating the conventional message passing update rules. We will show that the proposed half-broadcasting technique results in 26% global wirelength reduction in the presented 2048-bit fully-parallel decoder.

To increase the decoding throughput, we will discuss a block-interlacing technique where two independent frames can be decoded simultaneously. We compare the throughput improvement and the hardware overhead associated with this technique. For the two decoders reported in Chapter 4, the post-layout simulations show that the block interlacing improved the throughput 60% and 71% at the cost of only 5.5% and 9.5% more gates, respectively.

We will present an analysis of the energy efficiency of LDPC decoders as a function

of the degree of parallelism in the decoder architecture. The analysis shows that for a fixed throughput, the fully-parallel architecture is more power efficient than partiallyparallel decoders. In addition, we show how an early termination scheme can further reduce the power consumption by terminating the decoding process as soon as a valid codeword has converged. To facilitate the early termination, we introduce an efficient method of detecting the decoder convergence with minimal hardware overhead.

To reduce the interconnect complexity and decoder area, we also propose bitserial message passing in which the multi-bit messages are calculated and conveyed between processing in a bit-serial fashion. We will also propose an approximation to the min-sum decoding algorithm that reduces the area of the CNUs by more than 40% compared with conventional min-sum decoding with only 0.1dB performance penalty at BER= $10^{-6}$ .

Finally, we report on two different fully-parallel decoder implementations: one on an FPGA and one on an ASIC. The fabricated 0.13- $\mu$ m CMOS bit-serial (660, 484) LDPC decoder has a 300-MHz maximum clock frequency with a nominal 1.2-V supply corresponding to a 3.3-Gbps total throughput. It performs within 3 dB of the Shannon limit at a BER of 10<sup>-5</sup>. With the power saving achievable by early termination, the decoder consumes 10.4 pJ/bit/iteration at  $E_b/N_0=4$  dB at nominal supply voltage. Coupling early termination with supply voltage scaling results in 648 Mbps total decoding throughput with 2.7 pJ/bit/iteration energy efficiency which even compares favorably with analog decoders [16] aimed for energy efficiency.

### 1.2 Outline

The outline of this thesis is as follows. Chapter 2 provides background on the prior work on LDPC codes, decoding algorithms and decoder implementations. Chapter 3 describes a technique called broadcasting to reduce interconnect complexity. We will show the benefits of this technique both for partially-parallel and fully-parallel decoders. Chapter 4 discusses a block-interlacing scheme that further increases the decoding throughput. The power analysis and power reduction achievable by early decoding termination is presented in Chapter 5. A bit-serial fully-parallel decoding architecture is proposed in Chapter 6. Finally, Chapter 7 concludes the thesis and provides potential venues for future work. \_\_\_\_\_

# 2 Low-Density Parity-Check (LDPC) Codes

#### 2.1 Code Structure

A binary LDPC code, C, can be described as the null space of a sparse  $M \times N$ {0,1}-valued *parity-check* matrix, H [3]. In other words, C consists of codewords  $u = (u_1, u_2, \ldots, u_N)$  such that

$$uH^T = 0, (2.1)$$

where  $uH^T$  is computed in the Galois field GF(2). An LDPC code can also be described by a bipartite graph, or *Tanner graph* [17], as shown in Fig. 2.1. In this figure, variable nodes  $\{v_1, v_2, \ldots, v_N\}$  represent the columns of H and check nodes  $\{c_1, c_2, \ldots, c_M\}$  represent the rows. An edge connects check node  $c_m$  to variable node  $v_n$  if and only if  $H_{mn}$ , the entry in H at row m and column n, is nonzero. We denote the set of variables that participate in check  $c_m$  as  $N(m) = \{n : H_{mn} = 1\}$  and the set of checks in which the variable  $v_n$  participates as  $M(n) = \{m : H_{mn} = 1\}$ . A particular variable-node configuration (i.e., an assignment of  $\{0, 1\}$ -values to each of the variable nodes) is a codeword of C if and only if all the checks are satisfied, i.e., if and only if

$$\sum_{n \in N(m)} v_n = 0 \pmod{2},$$

for all  $m \in \{1, 2, ..., M\}$ . An LDPC code is called  $(d_v, d_c)$ -regular if the number of ones in all columns of H is  $d_v$  and the number of ones in all rows of H is  $d_c$ . If the number of ones in all columns or the number of ones in all rows is not equal, the code is referred to as an irregular code. For a code with a full-rank  $M \times N$  parity-check matrix, H, the code rate is R = (N - M)/N = 1 - M/N. Fig. 2.1 shows the Tanner graph for a trivial (3,6)-regular LDPC code with N = 10 and M = 5. It should be noted that in more realistic LDPC codes the code length N is much longer (typically greater than 100) and the number of ones in the parity check matrix is much lower than the number of zeros.

Figure 2.1: Tanner graph for a (3,6)-regular LDPC code and the corresponding parity check matrix.

LDPC codes are encoded using a generator matrix,  $G_{K\times N}$ , where K is the number of information bits per codeword. For a full-rank M by N parity check matrix we have K = N - M. The encoder generates the codeword  $u = (u_1, u_2, \ldots, u_N)$  from the input information vector  $v = (v_1, v_2, \ldots, v_K)$  based on

$$u = vG. (2.2)$$

Since all the valid codewords should satisfy the equality in (2.1), we have

$$vGH^T = 0, (2.3)$$

and since (2.3) is true for every valid v, we have

$$GH^T = 0. (2.4)$$

It can be shown that any full-rank H matrix can be rearranged by Gaussian elimination and row/column permutations into the form  $H = [P|I_{N-K}]$ , where P is an N - K by K matrix and  $I_{N-K}$  is an N - K by N - K identity matrix. From (2.4) it can be shown that the generator matrix G can be constructed as

$$G = [I_K | P^T]. (2.5)$$

A generator matrix with the form as in (2.5) is called a *systematic* generator matrix. It has the property that the encoded codeword consists of the information bits concatenated with N - K parity check bits. A systematic generator matrix simplifies the encoding process as only the parity bits need to be calculated to generate encoded words from blocks of information bits.

#### 2.2 LDPC Decoding Algorithms

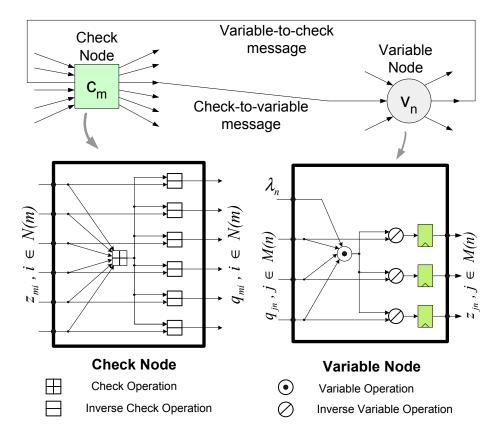

LDPC codes are decoded with a general family of decoding algorithms called iterative message-passing decoding algorithms. The sum-product algorithm (SPA) and min-sum (MS) algorithm are the two most commonly-used message-passing decoding algorithms and can be described using the Tanner graph representing the LDPC code. In these algorithms the decoding process starts by observing the channel inputs (*intrinsic* messages) corresponding to the variable nodes in the current received frame. Then each decoding iteration consists of updating and transferring *extrinsic* messages between neighboring variable and check nodes in the graph as shown in Fig. 2.2. A message encodes a *belief* about the value of a corresponding received bit and is usually expressed in the form of a log-likelihood ratio (LLR). Through message-passing these beliefs are refined and, in the case of a successful decoding operation, eventually converge on the originally transmitted codeword. The details of how messages are updated in SPA and MS decoding are presented in the next two sub-sections.

#### 2.2.1 Sum-product algorithm

Suppose that a binary codeword  $W = (w_1, w_2, \dots, w_N) \in C$  is transmitted over a communication channel and that a vector  $Y = (y_1, y_2, \dots, y_N)$  of bit signals is

Intrinsic messages from channel

Figure 2.2: Exchange of information in a message-passing decoding algorithm.

received. Let  $z_{mn}^{(i)}$  and  $q_{mn}^{(i)}$  represent the messages sent from  $v_n$  to  $c_m$  and from  $c_m$  to  $v_n$  in the *i*th iteration, respectively. Let  $N(m) = \{n : H_{mn} = 1\}$  and  $M(n) = \{m : H_{mn} = 1\}$ . Let  $I_M$  denote the maximum number of iterations. SPA decoding [18] consists of the following steps.

- 1. Initialize the iteration counter, i, to 1.

- 2. Initialize  $z_{mn}^{(0)}$  to the *a posteriori* log-likelihood ratios (LLR),  $\lambda_n = \log(P(v_n = 0|y_n)/P(v_n = 1|y_n))$  for  $1 \le n \le N$ ,  $m \in M(n)$ .

- 3. Update the check nodes, i.e., for  $1 \le m \le M$ ,  $n \in N(m)$ , compute:

$$q_{mn}^{(i)} = 2 \tanh^{-1} \left( \prod_{n' \in N(m) \setminus n} \tanh(z_{mn'}^{(i-1)}/2) \right).$$

(2.6)

4. Update the variable nodes, i.e., for  $1 \le n \le N$ ,  $m \in M(n)$ , compute:

$$z_{mn}^{(i)} = \lambda_n + \sum_{m' \in M(n) \setminus m} q_{m'n}^{(i)}.$$

(2.7)

5. Make a hard decision, i.e., compute  $\hat{W} = (\hat{w}_1, \hat{w}_2, \dots, \hat{w}_N)$ , where element  $\hat{w}_n$

is calculated as

$$\hat{w}_n = \begin{cases} 0 & \text{if } \lambda_n + \sum_{m' \in M(n)} q_{m'n}^{(i)} \ge 0; \\ 1 & \text{otherwise.} \end{cases}$$

for  $1 \leq n \leq N$ . If  $\hat{W}H^T = 0$  or  $i \geq I_M$  output  $\hat{W}$  as the decoder output and halt; otherwise, set i = i + 1 and go to step 3.

The sign (+ or -) of an LLR message indicates the belief about the value (0 or 1, respectively) of the received bit on the corresponding variable node. The magnitude of the message indicates the reliability of that belief. The variable update function in (2.7) combines all the beliefs about the value of the bit by adding the incoming messages. The check update function in (2.6) calculates the LLR for each outgoing message based on the fact that the parity check on all the edges connected to each check node has to be satisfied. This can be noted from the fact that for an LLR message  $\lambda$ , defined as  $\lambda = \log(P(0)/P(1))$ , one can show that  $\tanh(\lambda/2) = P(0) - P(1)$ .

#### 2.2.2 Min-sum algorithm

MS decoding [19] can be considered an approximation to SPA decoding [18]. The difference is that in MS, the check node update function of (2.6) is replaced with

$$\epsilon_{mn}^{(i)} = \min_{n' \in N(m) \setminus n} |z_{mn'}^{(i)}| \prod_{n' \in N(m) \setminus n} \operatorname{sgn}(\mathbf{z}_{mn'}^{(i)}).$$

(2.8)

Although the performance of MS is generally a few tenths of a dB lower than that of SPA decoding, it requires much simpler computational resources for the check node functions. Moreover, it is more robust against quantization errors when implemented with fixed-point operations [20].

To reduce the performance gap between MS and SPA algorithms, in [21] a modified check node update is proposed for the case of degree-3 check nodes by applying a correction factor to the check node update function in (2.8). In [22] a degree-matched modification is proposed for any check degree by applying a correction factor which is a function of the check node degree. It is shown that the modified min-sum algorithm provides almost the same BER performance as the SPA.

## 2.3 Capacity-Approaching LDPC Codes

In spite of recent progress in the information theory community, there are still no general methods to predict the performance of LDPC codes or to design LDPC codes with excellent performance that do not require extensive simulations. Some techniques, such as density evolution [23] and EXIT charts [24], exist to analyze and predict the convergence behavior of LDPC codes, but they usually are applied to families (or ensembles) of codes with infinite code length and certain check and variable degree distribution. Density evolution can be used to predict the decoding threshold value (i.e., the maximum noise level that can be added to the transmit signals while the decoder BER can be kept arbitrarily small). The density evolution and EXIT charts have also been used to optimize the degree distribution for constructing high performance irregular LDPC codes [25],[26].

Although the above techniques have enabled researchers to design long codes  $(N > 10^6)$  that perform less than a tenth of a dB from the Shannon limit, their accuracy tends to decrease for more practical codes with much shorter length. This is because the analysis in density evolution and EXIT chart techniques are only valid when the incoming messages arriving at each node are independent, which only happens when the code graph has no cycles. While this might be a reasonable approximation for long codes, the code graph of short LDPC codes inevitably contain some short cycles which make the above approximation inaccurate.

The length of the shortest cycle in the code graph is called the *girth* of the graph. Among other affecting parameters such as minimum weight and the number of short cycles in the code graph, it is known that in general LDPC codes with higher girth have better BER performance. Several algorithms have been proposed to construct high-girth LDPC codes [27],[28],[29]. As an example, in the progressive edge growth algorithm in [28] the code graph is constructed by incrementally adding the edges to the graph such that a high girth is maintained.

Also, families of LDPC codes have been constructed using finite geometries [30] and algebraic methods [10]. The method proposed in [10] is based on Reed-Solomon codes with two information bits. It is shown that the generated LDPC codes have no cycles of length 4 and have high minimum distance. Due to their superior performance and relatively short code length, the (6, 32)-regular (2048, 1723) RS-based LDPC code generated in [10] is now adopted as the standard code for the IEEE802.3an 10GBase-T standard [31].

#### 2.4 Decoder Implementation

Depending on the particular application, the objective when designing LDPC decoders is to meet a set of design specifications such as decoding throughput, power consumption, silicon area, decoding latency and testability. In the cases where the throughput and latency are explicitly mentioned in standards, the design goal is to achieve these specs while optimizing other parameters such as power and area.

As mentioned above, message-passing decoding requires a large number of messages to be updated and transferred on the code graph in each iteration. Previous researchers have proposed several approaches for representing and updating these messages.

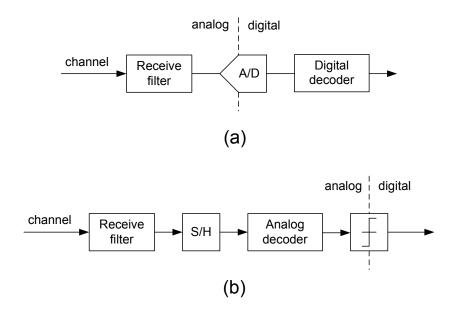

Figure 2.3: (a) Conventional receiver with digital ECC decoder, (b) An alternative receiver with analog decoder.

In [32], [33] and [16], analog signals are used to represent the extrinsic messages. Fig. 2.3 shows the difference between a conventional receiver architecture with digital decoder and an alternative architecture with an analog decoder. In analog decoders, the exponential voltage-current relationship of a bipolar device or a sub-threshold CMOS device is used to realize the required message-passing update functions. Although analog decoders have the advantage of relatively low power consumption, they are faced with the following challenges. First, due to process mis-matches and various sources of noise, analog decoders do not scale well with code length. This in turn limits the designer to adopt short LDPC codes (typically less than 500 bits) which usually have inferior BER performance. The limited scalability in analog decoders also limits the decoder throughput typically to less than 50 Mbps, which is far below the throughput requirement for current high-speed applications such as 10GBase-T or Digital Video Broadcast. Another major challenge in analog LDPC decoding is the need to store a relatively large number of analog signals at the beginning and also during the decoding process. Other issues include the need for framing the received symbols, the need for a customized design flow and finally the lack of testability.

In [34] an LDPC decoder with stochastic computation is proposed in which the messages are represented using Bernoulli sequences. Although this representation results in a very simple check and variable node architecture, it needs a significant amount of hardware overhead in order to interface the stochastic messages at the decoder inputs and outputs. In addition, since the stochastic computation uses a redundant number representation, it requires a large number of clock cycles to decode each frame (the decoder in [34] on average requires several hundred clock cycles at low SNRs and about 100 cycles at high SNRs) which limits the decoding throughput.

More conventional LDPC decoders often use a synchronous digital circuit with multi-bit digital signals to represent the messages. In these decoders, the decoding throughput,  $\eta$ , in *bits/s* is calculated as

$$\eta = \frac{Nf}{IL},\tag{2.9}$$

where N is the the code block length, I is the number of decoding iterations performed per block, L is the number of clock cycles required per iteration and f is the operating clock frequency. Parameters N and I are usually determined in the code design phase, so to increase the decoder throughput one must increase f/L. The maximum clock frequency of a synchronous digital circuit is determined by the propagation delay in the critical path (i.e., the longest path between sequential storage elements , e.g., flip-flops or latches). The value L (and also to some extent f) is a direct function of the decoder architecture.

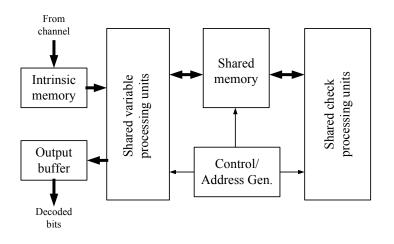

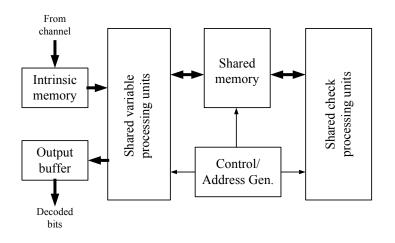

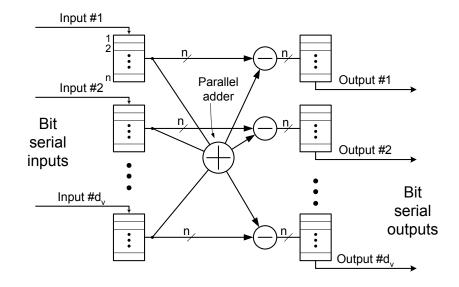

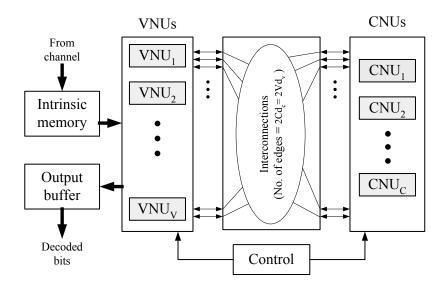

LDPC decoders can be broadly categorized into partially-parallel (also known as memory-based) decoders and fully-parallel decoders as described next. A generic partially-parallel LDPC decoder architecture is shown in Fig. 2.4. It consists of shared variable node update units (VNUs), shared check node update units (CNUs), and a shared memory fabric used to communicate messages between the VNUs and CNUs. Inputs to each CNU are the outputs of VNUs fetched from memory. After performing some computation (e.g., MIN operation for the magnitude and parity calculation for the signs in min-sum decoding), the CNU's outputs are written back into the extrinsic memory. Similarly, inputs to each VNU arrive from the channel and several CNUs via memory. After performing the message update (e.g., SUM operation in min-sum decoding), the VNU's outputs are written back into the extrinsic memory for use by the CNUs in the next decoding iteration. Decoding proceeds with all CNUs and VNUs alternately performing their computations for a fixed number of iterations, after which the decoded bits are obtained from one final computation performed by the VNUs.

A common challenge in partially-parallel architectures is to manage the large number of memory accesses and prevent memory collisions since multiple messages must be accessed simultaneously by the check and variable nodes. Examples of partially-parallel decoders include [35],[36] and [37]. The "hardware-aware code design" methodology in [35] provides 640 Mbps throughput (with 10 iterations per frame) for an LDPC code of block length 2048 with a tunable code rate; the design occupies 14.3 mm<sup>2</sup> in a 0.18- $\mu$ m CMOS technology. The partially-parallel DVB-S2 compliant LDPC decoders reported in [36] are programmable for 16200-bit or 64800bit modes and for a wide range of code rates. They achieve a maximum throughput of 90 Mbps and 135 Mbps in 130 nm and 90 nm technologies and occupy 49.6 mm<sup>2</sup> and 15.8 mm<sup>2</sup>, respectively. A 3.33 Gbps hardware-sharing (1200, 720) LDPC decoder is reported in [37].

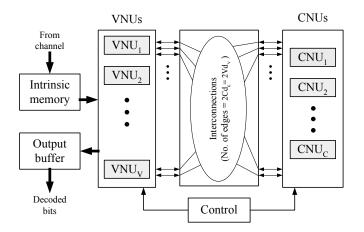

In fully-parallel decoders, each node in the code's Tanner graph is assigned a dedicated hardware processing unit, and messages are communicated between nodes by wires. Fig. 2.5 shows the high-level architecture of a fully-parallel decoder. It can be seen that the extrinsic memory block of Fig. 2.4 is replaced with the interconnections. This is because in a fully-parallel architecture, each extrinsic message is only written by one VNU or CNU, so the extrinsic memory can now be distributed amongst the VNUs and CNUs and no address generation is needed. The drawbacks of a fully-parallel architecture are the large circuit area required to accommodate all the processing units, as well as a complex and congested global interconnect net-

Figure 2.4: A partially-parallel LDPC decoder.

work. Routing congestion leads to longer interconnect delays and can degrade decoder timing-performance and dynamic power dissipation. Examples of fully-parallel decoders include [15] [38] [39].

Figure 2.5: The fully-parallel iterative LDPC decoder architecture.

Both fully-parallel and partially-parallel decoders need to store the extrinsic messages so that they can be accessed in the next decoding iteration. The size of memory should be at least equal to the number of edges in the code Tanner graph. Usually in pipelined designs the memory size is a constant multiple of the number of edges. In partially-parallel decoders the messages are stored in large memory blocks and are accessed through read/write operations. However, in fully-parallel decoders the storage is more distributed among processing units typically in the form of flip-flops. Although in comparison with an SRAM memory cell individual flip flops occupy larger area and consume more power, they have their advantages: they do not require address generation and in addition they can be accessed simultaneously by their corresponding processing units.

### 2.5 Architecture-Aware LDPC Codes

It is known that although randomly-generated LDPC codes with no regular structure in the parity check matrix tend to have high performance, they are not usually suitable for VLSI implementation. The reason is that randomly-structured codes require complex memory module addressing schemes that tend to decrease the decoding throughput and increase the area and power consumption.

To overcome these issues, researchers have proposed a decoder-first code design [40] methodology in which the LDPC code is designed to fit a pre-determined decoding architecture. The goal has been to minimize the degradation due to the structure in the code graph. In [41] a joint code-decoder design methodology is proposed. Using this methodology, Zhang and Parhi designed a (3, k)-regular LDPC code with  $L \cdot k^2$  variable nodes and  $3L \cdot k$  check nodes. It is suitable for its proposed partially-parallel decoder architecture with  $k^2$  variable processing units and k check processing units.

In [42] a Turbo-Decoding Message-passing (TDMP) decoding architecture is proposed along with an architecture-aware code construction that is shown to improve the convergence speed of the decoding process and reduces memory requirements.

Quasi-cyclic (QC) LDPC codes have the advantage of efficient encoding architecture using feedback shift registers. In [43] two classes of QC-LDPC codes are generated that perform close to computer-generated random codes. In [44] two methods are proposed to construct a systematic cyclic generator matrix from a QC parity-check matrix.

A convolutional version of LDPC codes has been proposed in [45]. At any given time, each code bit in an LDPC convolutional code (LDPC-CC) is generated using only previous information bits and previously generated code bits. It is shown that for certain applications, such as streaming video and variable length packet switching networks, LDPC-CCs are preferred over the conventional block LDPC codes [46]. LDPC-CCs also have the advantage of simple encoder structure. An ASIC implementation of a 175-Mbps, rate-1/2 (128, 3, 6) LDPC-CC encoder and decoder is reported in [47].

### 2.6 Overview

The motivation for this work is to design LDPC decoders with high throughput for applications such as fiber-optic communication systems and 10-Gbit Ethernet. This leads naturally to the investigation of fully-parallel architectures as these exploit all of the available parallelism in the message-passing decoding algorithm. Our power consumption analysis shows that fully-parallel architectures may also have advantages in energy efficiency.

A common challenge for fully-parallel LDPC decoders is the routing congestion between variable and check nodes which is the result of the randomness in the code parity check matrix. In this work, we present a technique called broadcasting and illustrate how it can reduce the routing congestion.

An overlapped message-passing architecture is then presented to increase the decoding throughput with a relatively small hardware overhead. We show that for the two presented fully-parallel decoders, the throughputs are improved by more than 60% at the cost of less than 10% logic overhead.

The power consumption is always a very important criteria in LDPC decoders. We will present an analysis of how the increased parallelism in the LDPC decoder architecture results in reduced total power consumption for a given target throughput. In addition we will illustrate an efficient early termination technique to further reduce the decoder dynamic power consumption.

We demonstrate implementations of a bit-serial message-passing decoder that reduce the routing congestion and also result in lower decoder core area. We also propose an approximation to the min-sum decoding algorithm which simplifies the check node logic with minimal BER penalty.

Although most of the proposed techniques in this work are mainly developed for fully-parallel decoders, we will explain how some of them can also be applied to partially-parallel decoders.

## **3 Reducing Interconnect Complexity**

As mentioned in Chapter 2, a common challenge when implementing LDPC decoders is communicating the extrinsic messages through the complex interconnections between the variable and check nodes. In partially-parallel decoders, the interconnection network results in a complicated memory access scheme where multiple processing units need to access a large number of shared memory blocks in parallel. In fully-parallel decoders, the complex interconnection results in a complicated routing network all across the chip in order to transfer the messages between the parallel check and variable processing units.

In this chapter we describe a technique called broadcasting that reduces the nodeto-node communication complexity in LDPC decoding. We will show how this technique can be applied to both fully-parallel and partially-parallel decoder architectures. We will also discuss the trade-offs that two variants of broadcasting (half-broadcasting and full-broadcasting) provide in terms of logic overhead and reduced interconnect complexity.

## 3.1 Half-broadcasting

We start by re-writing (2.6) and (2.7) of the sum-product algorithm as follows. Let

$$q_{mn}^{(i)} = 2 \tanh^{-1} \left( P_m^{(i)} / \tanh(z_{mn}^{(i-1)}/2) \right), \qquad (3.1)$$

where

$$P_m^{(i)} = \prod_{n' \in N(m)} \tanh(z_{mn'}^{(i-1)}/2)$$

(3.2)

and let

$$z_{mn}^{(i)} = S_n^{(i)} - q_{mn}^{(i)}, (3.3)$$

where

$$S_n^{(i)} = \lambda_n + \sum_{m' \in M(n)} q_{m'n}^{(i)}.$$

(3.4)

Figure 3.1: A conventional fully-parallel message-passing LDPC decoder with generic functions for check and variable nodes.

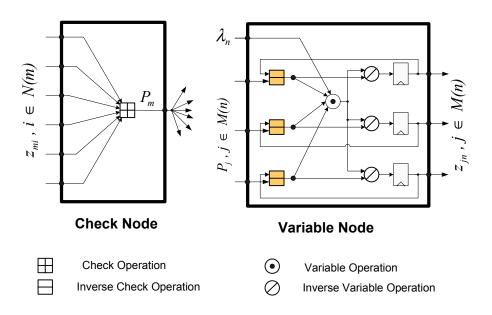

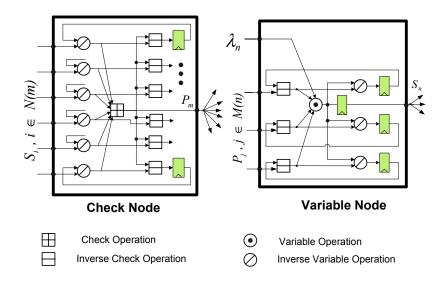

Fig. 3.1 shows the block diagram of a check and variable processing unit using (3.1)-(3.4). Symbols  $\boxminus$  and  $\boxplus$  denote the operations that are performed in (3.1) and (3.2), respectively. Similarly, symbols  $\oslash$  and  $\odot$  denote operations performed in (3.3) and (3.4), respectively.

Half-broadcasting is a repartitioning of the computations in Fig. 3.1. In this new partitioning, shown in Fig. 3.2, the  $\boxminus$  functions are moved to the variable nodes without affecting the message-passing algorithm. This is because extrinsic messages,  $q_{mn}^{(i)}$ , are reconstructed in the variable nodes from the received  $P_m^{(i)}$  and the  $z_{mn'}^{(i-1)}$ 's from iteration i-1. So, unlike the schemes in [48, 15, 2] in which each degree- $d_c$  check node generates  $d_c$  separate messages, one for each neighboring variable node, in this scheme each check node *broadcasts* a single message (i.e.,  $P_m^{(i)}$ ) to all of its neighbors. This approach reduces the amount of information that needs to be conveyed from check nodes to variable nodes. In a fully-parallel decoder, this translates into a reduction in global interconnect. In a partially-parallel decoder, it translates into fewer memory accesses.

Although the broadcasting technique above was described using the sum-product algorithm, the same technique can be applied to other variations of message-passing decoding such as min-sum decoding and bit-flipping [3]. For example, in the case of min-sum decoding, the variable nodes would be designed to broadcast the total value,  $S_n$ , to their neighbors.

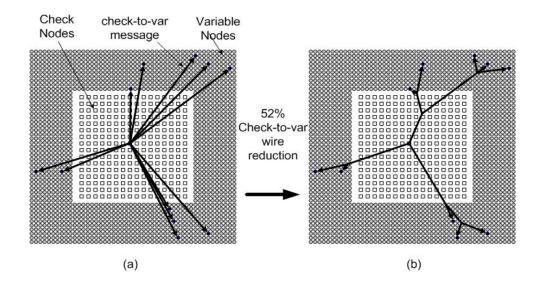

#### 3.1.1 Half-broadcasting for fully-parallel decoders

Fig. 3.3 shows conceptually how the broadcasting technique can mitigate the interconnection problem in fully-parallel decoders. In this figure, a floorplan similar to [15] is used, where the check nodes are placed in the center of the chip layout and variable nodes are placed on the sides. In Fig. 3.3(a), a node architecture with no broadcasting is assumed, where one sample check node in the center of the chip sends different messages to its neighboring variable nodes. This is done by dedicating separate wires (or buses) for each destination. However, using broadcasting, we share a significant amount of interconnect wiring when conveying messages from each source check node to the destination variable nodes, as in Fig. 3.3(b).

Fig. 3.4 shows a zoomed-in portion of the check-to-variable interconnects for a 2048-bit LDPC code before and after applying a half-broadcast scheme. This figure is generated by Matlab simulation and assumes that wires can be in any arbitrary

Figure 3.2: A half-broadcast architecture. The check node  $c_m$  broadcasts a single message,  $P_m$ , to all neighboring variable nodes.

direction. However, we can observe similar congestion effect in the layouts where only vertical and horizontal wiring is used.

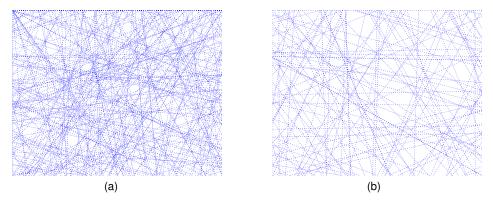

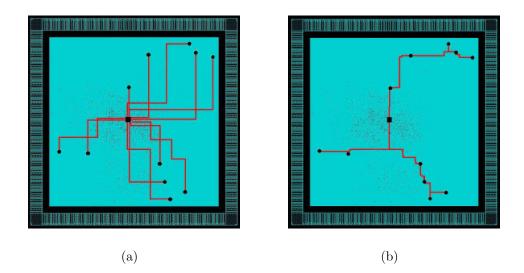

Fig. 3.5 shows the effect of the broadcasting technique on a fully-parallel decoder layout. These are real layouts obtained by automated place-and-route tools from Cadence using a floorplan similar to [15] where the check nodes are instantiated in the center and the variable nodes are instantiated on the sides of the decoder layout. One check node and its neighboring 11 variable nodes and the nets for conveying checkto-variable intrinsic messages between them are highlighted in the figure for clarity. Fig. 3.5(a) shows the case where no broadcasting is applied. Fig. 3.5(b) shows that by using the broadcasting scheme of Fig. 3.2, a significant amount of interconnect wiring can be shared, hence mitigating the complexity of interconnections.

To compare the effects of half-broadcasting on reducing the global wirelength, we implemented a fully-parallel 1-bit quantized LDPC decoder for the (6, 32)-regular (2048, 1723) code adopted for the 10GBase-T Standard twice: first without half-

Figure 3.3: Broadcasting reduces the total top-level wirelength by sharing the wires. (a) Output messages of a check node without broadcasting (b) Sharing interconnect wires of a check node with broadcasting

Figure 3.4: A small section of interconnects for a length-2048 LDPC code (a) before broadcast (b) after broadcast. There is 40% reduction in total wirelength.

broadcasting and once with broadcasting. In both cases the decoding algorithm was based on the Gallager's Algorithm A as described in [23].

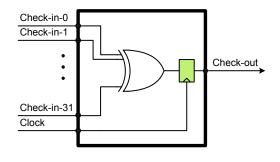

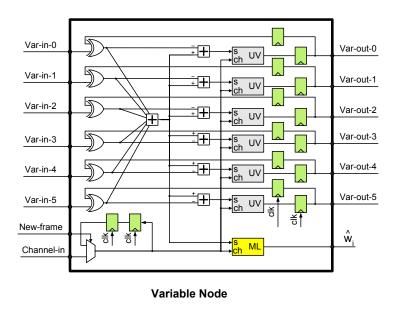

Fig. 3.6 shows the check and variable node architecture for the non-broadcasting decoder. In Algorithm A, all the check-to-variable and variable-to-check messages are 1-bit values, or *votes*, regarding the value of the corresponding received bit. In the

Figure 3.5: The routed nets for one check node output highlighted in a fully-parallel LDPC decoder layout: (a) without broadcasting and (b) with broadcast-ing.

check nodes, each output message is the exclusive-OR of all the other 31 check node inputs. In the variable nodes, the adders and subtracters first calculate the sum of the votes on each message. Then the unanimous voting (UV) blocks calculate the variable node outputs from the channel input, c, and the number of votes for one, s. The UV block output, u is calculated as:

$$u = \begin{cases} 1 & \text{if } s = 5 \\ c & \text{if } 5 > s > 0 \\ 0 & \text{if } s = 0 \end{cases}$$

In other words, the variable node output on each edge is always the same as the channel input except when all the other incoming messages vote against it. The majority logic block (ML) calculates the hard decision decoder output w from the channel input, c, and the total votes, t, based on:

$$w = \begin{cases} 1 & \text{if } t > 3 \\ c & \text{if } t = 3 \\ 0 & \text{if } t < 3 \end{cases}$$

The **new-frame** signal specifies the end of one set of iterations and start of loading a new frame.

| Code                | P&R tool | Predicted |

|---------------------|----------|-----------|

| (992,829) RS-LDPC   | -        | 27%       |

| (2048,1723) RS-LDPC | 26%      | 26%       |

| (4096,3403) RS-LDPC | -        | 27%       |

Table 3.1: The average wirelength reduction for global nets in fully-parallel LDPC decoders.

Fig. 3.7 shows the variable node and check node for the decoder with half-broadcast scheme. In this decoder the result of the 32-bit exclusive-OR is broadcast from each check node to all of its neighboring variable nodes. The correct message is then reconstructed in the variable nodes using the variable-to-check messages from previous iteration without affecting the functionality of the decoder.

As explained in this section, half broadcasting results in reduced global wirelength in fully-parallel decoders. For the two 2048-bit decoder designs presented in this chapter, the broadcasting scheme reduced the average node-to-node wirelength by 26% from 1.88 mm to 1.40 mm. The timing and BER performance of the implemented decoder will be presented in more detail in Chapter 4.

Table 3.1 lists the percentage wirelength reduction obtained from half-broadcasting compared with the conventional case where no broadcasting is applied. The technique is applied to LDPC codes with various lengths. The values in the first column are obtained from automated P&R tools. The values in the second column are obtained from a prediction algorithm which approximates a Steiner tree [49] solution to predict the wirelength savings by using the actual floorplan of the fully-parallel decoder and the silicon area dedicated to each variable and check-update unit in the floorplan. Table 3.1 shows that for code lengths of a few thousand bits assuming half-broadcasting yields similar savings in global wirelength.

(a)

(b)

Figure 3.6: (a) The CNU and (b) the VNU architectures for a conventional hard decision message-passing decoder with no broadcasting.

(a)

(b)

Figure 3.7: (a) The CNU and (b) the VNU architectures for a hard decision messagepassing decoder with half broadcasting.

#### 3.1.2 Half-broadcasting for partially-parallel decoders

For partially-parallel LDPC decoders, broadcasting reduces the number of shared memory write accesses. This is because in a conventional partially-parallel decoder, each check-processing unit (CPU) reads the extrinsic messages,  $z_{ij}$ , generated in the previous iteration from the memory and writes the resulting  $q_{ij}$  messages to another shared memory to be read by variable-processing units (VPU's), and so on. Thus the CPU for a check node with degree  $d_c$ , needs to perform  $d_c$  reads and  $d_c$  writes. By using a broadcast scheme for the check nodes, the CPU still needs to read  $d_c$  input values, but since the CPU generates only one output value, just one write operation is required. In total, the number of read/write memory accesses per CPU per iteration is reduced from  $2d_c$  to  $d_c + 1$ . Unlike fully-parallel decoders, there is some hardware overhead for half-broadcasting in partially-parallel decoders since the  $z_{mn}$ 's also need to be stored locally in the VPU for use in the next iteration. This additional local storage, however, does not add to the global node-to-node communication complexity.

# 3.2 Full-broadcasting

We called the architecture of Fig. 3.2 half-broadcasting because we applied the broadcasting technique only to the check-to-variable messages while the variable-to-check messages were kept unchanged. The same idea can be extended to a *full-broadcasting* scheme in which both check-to-variable and variable-to-check messages are broadcast. Fig. 3.8 shows the variable and check node architecture capable of full-broadcasting. In this figure, the inverse-check and inverse-variable operations,  $\boxminus$  and  $\oslash$ , are duplicated in order to be able to reconstruct the individual messages from the interim variable and check totals. A memory-based version of full-broadcasting is proposed in [50]. As one can expect, full-broadcasting results in further simplification in interconnect complexity; however this comes with a relatively large logic overhead. The exact amount of this overhead depends on the exact type of variable and check update functions, but since most of the calculations are duplicated, the overhead can be as much as 2x [50]. In addition, it should be noted that the full-broadcasting technique is not applicable for decoding algorithms, such as min-sum decoding, where either the inverse-check function,  $\boxminus$ , or inverse variable function,  $\oslash$ , is not available.

Figure 3.8: A full-broadcast architecture. The check node  $c_m$  broadcasts  $P_m$  to the neighboring variable nodes. The variable node  $v_n$  broadcasts  $S_n$ .

# 3.3 Comparison and Discussion

Depending on the type of update functions, the designer may need to assign a larger word length for the broadcast values (e.g.,  $P_m^{(i)}$  in (3.2) and  $S_n^{(i)}$  in (3.4) in the case of Sum-Product message-passing) compared with the word length needed for the actual extrinsic values (e.g.,  $q_{mn}^{(i)}$ 's and  $z_{mn}^{(i)}$ 's in (3.1) and (3.3)). In these cases, the effect of increased word length for broadcast messages must be taken into account. As an example, if  $\lambda_n$  and  $q_{m'n}$ 's in (3.4) are quantized with q bits, then  $q + \lceil \log(d_v + 1) \rceil$ bits would be required to represent  $S_n$ . However, since the word length of the  $z_{mn}$ 's in (3.3) is generally limited to only q bits by clipping, as in [20],  $S_n$  can be represented with only q + 1 bits without loss of accuracy. So, the variable-to-check messages will have  $0.5(1/q) \times 100\%$  additional wiring <sup>1</sup> due to the increased word length in  $S_n$ . For q=6, the overhead becomes 8%. A similar analysis can also be made for the checkto-variable broadcasting of Fig. 3.2 since the multiplications and divisions in (3.1) and (3.2) are usually transformed into summations and subtractions in the logarithm

<sup>&</sup>lt;sup>1</sup>The 0.5 coefficient arises because in this case half-broadcasting only affects the variable-to-check messages and keeps the check-to-variable messages unchanged.

domain. One particular case is the hard-decision message passing decoding [23] in which the  $z_{mn}$ 's and  $q_{mn}$ 's in Fig. 3.1 are 1-bit messages, and  $\boxplus$  and  $\boxminus$  symbols both indicate exclusive-OR operations. As a result, the broadcast message,  $P_m$ , in Fig. 3.2 is also a 1-bit value, hence no word length increase is required.

To compare the effectiveness of different broadcasting schemes in a partiallyparallel LDPC decoder, we define the node-to-node communication complexity as the number of unique LLR messages being read/written from/to the shared memory per iteration. <sup>2</sup> For an LDPC code with E edges in the graph, 2E global read operations are involved in each iteration: E reads in the check-update phase and Ereads in the variable-update phase, independent of the type of broadcasting. The number of write operations, however, varies with the choice of broadcasting. In a conventional decoder, each variable node generates  $d_v$  unique messages, so  $Nd_v = E$ write operations are needed in variable-update phase. Similarly, E write operations are needed for the check-update phase. In a half-broadcasting scheme in which the check nodes each broadcast a single LLR message, the number of variable-update phase memory writes continues to be E; however, the number of check-update phase write operations is reduced to M. Finally, in a full-broadcast scheme the number of required write operations for variable and check-update phase is reduced to N and M, respectively.

To summarize, one decoding iteration in a no-broadcast scheme requires 2E + 2E = 4E read/write operations. With half-broadcasting this is reduced to  $2E + E + M = (3 + 1/d_c)E$ . With full-broadcasting this is further reduced to  $2E + N + M = (2 + 1/d_v + 1/d_c)E$ . For moderately large values of  $d_v$  and  $d_c$ , half-broadcasting and full-broadcasting result in close to 25% and 50% memory access reductions, respectively, compared to a no broadcasting scheme. As an example, for a (6-32)-regular (2048,1723) LDPC code in the 10GBase-T standard (E = 12288), the number of global memory accesses per iteration is reduced by 24% and 45% using half-broadcasting and full-broadcasting, respectively.

The above comparisons suggest that in fully-parallel decoders, half-broadcasting provides a better trade-off between relaxing node-to-node communication complexity and logic overhead. Meanwhile, the full-broadcasting architecture can be the preferred choice in low-parallelism LDPC decoders where logic area constitutes a small portion

<sup>&</sup>lt;sup>2</sup>In addition to communication complexity, one can also investigate the effectiveness of broadcasting schemes from energy consumption point of view and possibly assigning different energy costs for the read and write operations.

of the total decoder area and hence the logic overhead due to full-broadcasting can be tolerated.

# 4 Block-Interlaced Decoding

#### 4.1 Background

Each iteration of LDPC message-passing decoding consists of updating check and variable node outputs based on functions similar to (3.1) and (3.3). Due to the data dependency, the computation of  $z_{mn}^{(i)}$  in (3.3) cannot be started until all the  $q_{m'n}^{(i)}$ ,  $m' \in M(n)$  have been calculated from (3.1). Similarly, the check-update phase cannot be started before completion of the variable update phase of the previous iteration.

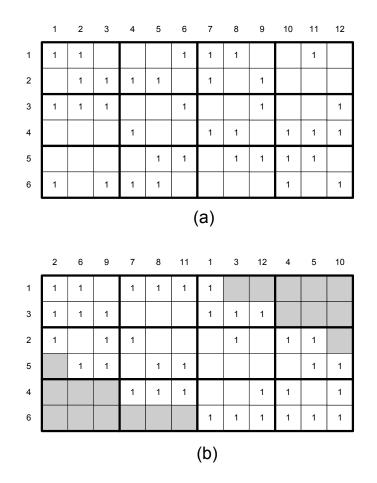

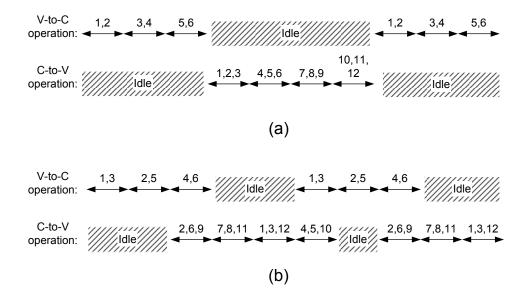

In [1], an overlapped message-passing scheduling is proposed for quasi-cyclic LDPC codes decoded in a memory-based architecture. The idea is to perform the check (variable) node update phase in an order such that the variable (check) node update phase can be started for some variable (check) nodes before all the check (variable) node updates are complete. A modified scheduling algorithm for overlapped message passing is proposed in [50] which can be applied to any LDPC code. The algorithm in [50] is based on permuting rows and columns of H so that the sub-matrices in the lower-left and upper-right corners of the permuted H are all zeros. Fig. 4.1 shows an example of a  $6 \times 12$  parity check matrix before and after the row and column permutations as proposed in [50]. In Fig. 4.2 the corresponding timing diagrams are shown. The timing diagrams are based on a partially-parallel decoder architecture with two shared CPUs and three shared VPUs. In contrast to the diagram in Fig. 4.2a, the diagram in Fig. 4.2(b) shows that using the permuted H matrix of Fig. 4.1(b), some variable nodes (i.e., columns 2, 6 and 9) can be updated even before the check node update phase is complete. Similarly, some check nodes (i.e., rows 1 and 3) can be updated before the variable node update phase from previous iteration is complete. This overlapped scheme reduces the amount of time required to perform one decoding iteration, hence it results in higher decoding throughput. The maximum possible amount of overlapping in a partially-parallel message-passing LDPC decoder is directly related to the number of all-zero sub-matrices (i.e., the  $m \times n$  sub-matrices, where m and n are the number of shared CPUs and VPUs, respectively) in the lower left and upper right corners of the permuted H matrix.

Figure 4.1: An example of row/column permutation of H matrix in overlapped message-passing [1]: (a) the original H matrix, (b) the permuted H matrix.

Figure 4.2: Message-passing timing diagram for (a) the original matrix of Fig. 4.1.a (b) for the permuted matrix of Fig. 4.1.b.

One drawback of the overlapped message-passing is that as the number of parallel variable and check processing units increases, the potential increase in throughput is decreased. This can be seen from Fig. 4.1. As the parallelism increases the relative size of the sub-matrices in H is also increased and as a result it becomes increasingly harder to find a permuted H matrix with all-zero sub-matrices in the lower-left and upper-right corners. (In the case of a fully-parallel architecture, the sub-matrix becomes the same size as the parity check matrix and as a result no overlapping is possible). In addition, the potential throughput gain is reduced for smaller H matrices with high variable and check node degrees.

# 4.2 Interlacing

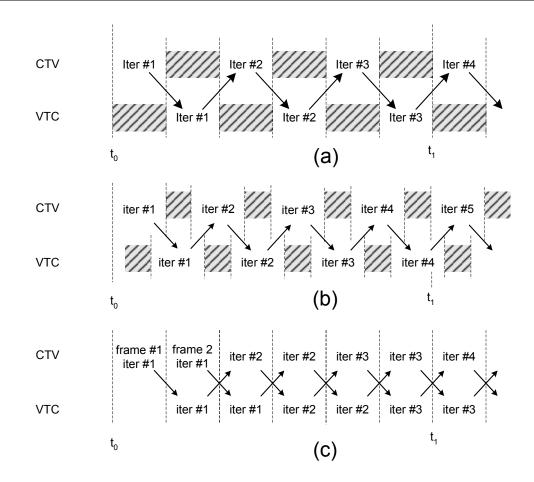

The following paragraphs describe an alternative approach to increase the decoding throughput. We will show that unlike the overlapped message-passing technique, the proposed scheme is most applicable for the fully-parallel decoder architecture. We will also evaluate the throughput improvement and associated costs of this approach for two fully-parallel LDPC decoders.

Figure 4.3: A timing diagram for the message-passing algorithm: (a) conventional (b) overlapped message passing [1] (c) block interlacing.