# DIRECT GMSK GENERATION USING SIGMA-DELTA MODULATION

by

Denis Daly

April 2003

Supervisor: Anthony Chan Carusone

# DIRECT GMSK GENERATION USING SIGMA-DELTA MODULATION

by

Denis Daly

#### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF BACHELOR OF APPLIED SCIENCE

#### DIVISION OF ENGINEERING SCIENCE FACULTY OF APPLIED SCIENCE AND ENGINEERING UNIVERSITY OF TORONTO

Supervisor: Anthony Chan Carusone

April 2003

© Copyright by Denis Daly, 2003

## DIRECT GMSK GENERATION USING SIGMA-DELTA MODULATION

Denis Daly

Degree of Bachelor of Applied Science University of Toronto 2003

#### Abstract

A constant-envelope, continuous phase modulation architecture is presented in which a sigma-delta modulator is combined with a direct modulator. The main advantages of this architecture are that linearity of the oscillator's tuning device is ensured and implementation is simplified due to the use of discrete frequency switching in the oscillator. The main disadvantage is that the quantization noise introduced by the  $\Sigma$ - $\Delta$  modulator must be filtered out or spread out to ensure wireless noise specifications are met. The architecture is simulated in an open-loop configuration implementing GMSK modulation for use in a GSM transceiver. A prototype, low-frequency implementation of the modulation architecture is constructed and experimental results are found to match simulations. By increasing the  $\Sigma$ - $\Delta$  modulation frequency, the quantization noise is filtered out by the VCO and disappears beneath the measurement noise floor.

## **Acknowledgements**

I would like to thank Professor Anthony Chan Carusone for his guidance and mentorship over the past year. He has taught me much and has helped prepare me for graduate school. I would also like to thank my parents for their continual support. This thesis wouldn't have been possible without their loving presence in my life.

## Contents

| Abstract                                                                                                                                                                                                                     | i                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Acknowledgements                                                                                                                                                                                                             | ii                              |

| Contents                                                                                                                                                                                                                     | iii                             |

| List of Figures                                                                                                                                                                                                              | iv                              |

| List of Tables                                                                                                                                                                                                               | v                               |

| List of Abbreviations                                                                                                                                                                                                        | vi                              |

| <ul> <li>Chapter 1: Introduction</li> <li>1.1 Motivation</li> <li>1.2 Applications and the State of the Art</li> <li>1.3 Background</li> <li>1.4 Outline</li> </ul>                                                          | <b>1</b><br>1<br>2<br>4<br>7    |

| <ul> <li>Chapter 2: Proposed Modulation Architecture</li> <li>2.1 Overview of Architecture</li> <li>2.2 Advantages</li> <li>2.3 Disadvantages</li> <li>2.4 Frequency Analysis</li> <li>2.5 System Analysis of PLL</li> </ul> | <b>8</b><br>9<br>10<br>11<br>13 |

| <ul> <li>Chapter 3: Circuit Implementation</li> <li>3.1 Overview</li> <li>3.2 Voltage-Controlled Oscillator</li> <li>3.3 Circuit Simulations</li> </ul>                                                                      | <b>18</b><br>18<br>18<br>22     |

| <ul> <li>Chapter 4: Experimental Results</li> <li>4.1 Overview</li> <li>4.2 Frequency Spectrum Plots</li> </ul>                                                                                                              | <b>18</b><br>26<br>28           |

| Chapter 5: Conclusion5.1Summary5.2Future Work                                                                                                                                                                                | <b>30</b><br>30<br>30           |

| References                                                                                                                                                                                                                   | 32                              |

| Appendix A: PLL Closed-Loop Calculations                                                                                                                                                                                     | 34                              |

# List of Figures

| Figure 1. Three popular methods to modulate a signal 2                                           |

|--------------------------------------------------------------------------------------------------|

| Figure 2. A Second-Order Sigma-Delta Modulator                                                   |

| Figure 3. Frequency Spectrum of a Second-Order Sigma-Delta Modulator                             |

| Figure 4: A MSK Encoded Signal                                                                   |

| Figure 5: A Sigma-Delta Based Open-Loop Frequency Modulator                                      |

| Figure 6: Adder Simplification due to the $\Sigma\Delta$ modulator                               |

| Figure 7: Power spectrum of random data and Gaussian filtered random data 10                     |

| Figure 8: Frequency Power Spectrum of a GMSK Signal12                                            |

| Figure 9: Frequency Power Spectrum of a Sigma-Delta Modulated                                    |

| Figure 10: Linearized system diagram of a PLL                                                    |

| Figure 11: Bode plot of $Y_f(s)/D(s)$ for the PLL in a closed-loop configuration                 |

| Figure 12: Circuit diagram of differential LC oscillator                                         |

| Figure 13: (a) Circuit diagram and (b) layout of the modelled on-chip inductor20                 |

| Figure 14: Broad tuning curve of the VCO21                                                       |

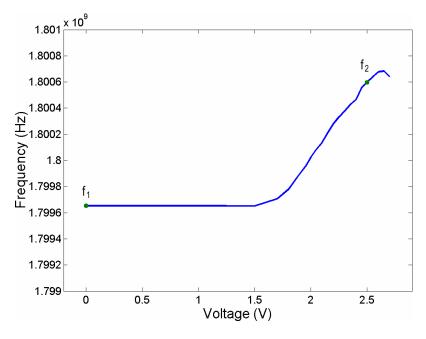

| Figure 15: Fine tuning curve of the VCO                                                          |

| Figure 16: Instantaneous frequency response of the VCO                                           |

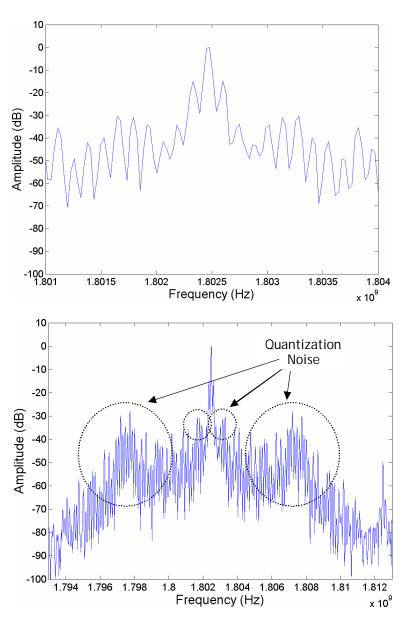

| Figure 17: Frequency spectrum plots of GMSK output ( $\Sigma$ – $\Delta$ Frequency of 10 MHz)24  |

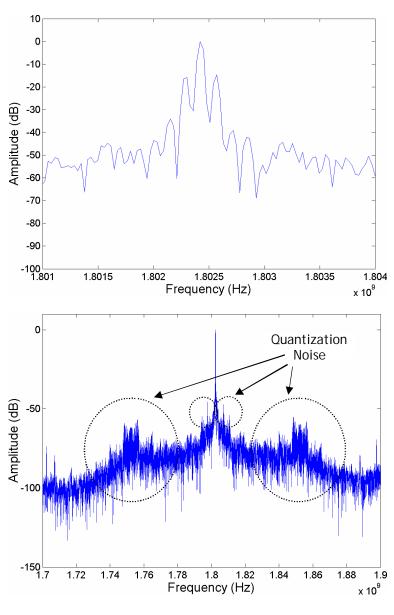

| Figure 18: Frequency spectrum plots of GMSK output ( $\Sigma$ – $\Delta$ Frequency of 100 MHz)25 |

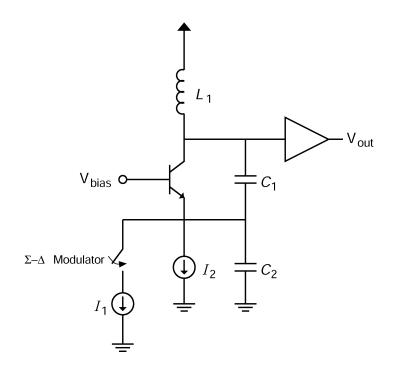

| Figure 19: Single-ended Colpitts LC oscillator                                                   |

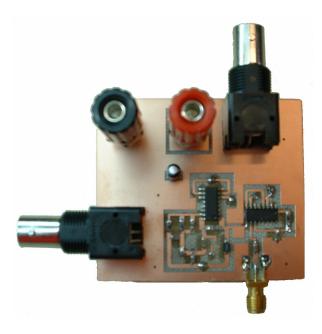

| Figure 20: Printed Circuit Board27                                                               |

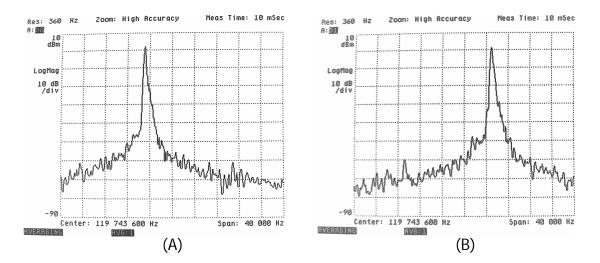

| Figure 21: (A) Lower frequency and (B) upper frequency that the oscillator switched between 28   |

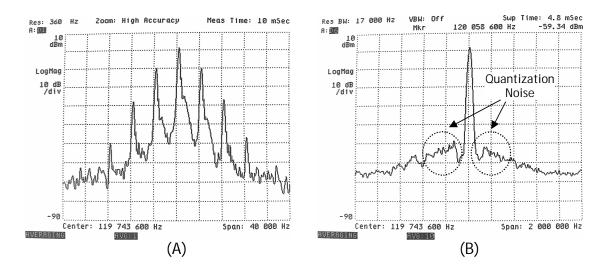

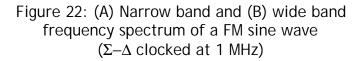

| Figure 22: (A) Narrow band and (B) wide band frequency spectrum of a FM sine wave                |

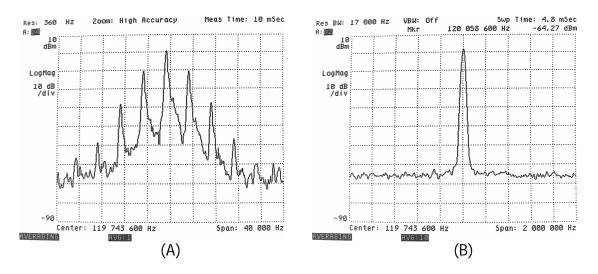

| Figure 23: (A) Narrow band and (B) wide band frequency spectrum of a FM sine wave                |

## List of Tables

| Table 1: Current GSM technologies                  | 7    |

|----------------------------------------------------|------|

| Table 2: PLL specifications from [9]               | . 16 |

| Table 3: Values for Figure 12                      | . 19 |

| Table 4: Values for the on-chip inductor           | . 20 |

| Table 5: Values for the single-ended LC oscillator | . 27 |

# List of Abbreviations

| A/D  | Analog to Digital                       |

|------|-----------------------------------------|

| D/A  | Digital to Analog                       |

| DAC  | Digital to Analog Converter             |

| GMSK | Gaussian Minimum Shift Keying           |

| GSM  | Global System for Mobile Communications |

| MSK  | Minimum Shift Keying                    |

| РСВ  | Printed Circuit Board                   |

| PLL  | Phase-Locked Loop                       |

| VCO  | Voltage Controlled Oscillator           |

| S- D | Sigma-Delta                             |

Chapter 1

## Introduction

#### 1.1: Motivation

As the world continues to adopt wireless electronic devices, there exists a demand for engineers to develop faster, cheaper, and more reliable circuits to power these devices. Despite the dot.com meltdown at the start of the millennium, growth in the wireless market shows no signs of slowing. GSM, a second generation wireless technology used in cellular phones, currently has 800 million subscribers worldwide and there are expected to be 1.3 billion GSM subscribers by 2006 [1].

At the heart of every wireless device is a phase-locked loop (PLL), an analog circuit used for frequency synthesis and clock recovery. The design of the phase-locked loop is critical - it significantly affects the power consumption, cost, and transmission quality of the device. Since most wireless devices are mobile and are powered by a battery, decreased power consumption and hence increased battery life is an important consideration to consumers. The cost of the device is also important to consumers. The transmission quality of the device is usually more of a concern to companies than consumers. For example, a company must ensure that its GSM cellular phones transmit wireless signals that adhere to international standards. Otherwise, the phone will not work reliably or will disrupt the operation of other cellular phones.

This thesis will discuss a new frequency synthesizer architecture that can be used in wireless devices to modulate a digital signal. Section 1.2 will provide an outline of existing modulation architectures and Section 1.3 will explain a few key concepts that are used in the proposed modulation architecture.

1

#### 1.2: Applications and the State of the Art

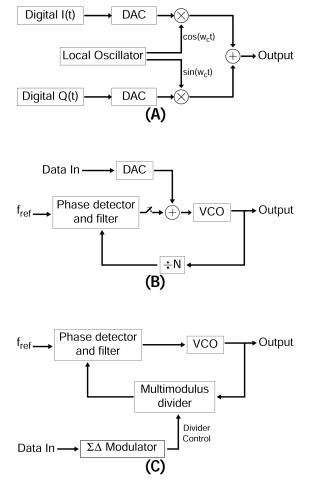

There are three popular methods to perform phase/frequency modulation of a digital signal: quadrature modulation, open-loop modulation, and modulated synthesis. Fig. 1 shows block diagrams for each of these methods.

Figure 1. Three popular methods to modulate a signal

- A) Quadrature modulation

- B) Open-loop modulation

- C) Modulated synthesis

#### Quadrature Modulation

Of these three methods, quadrature modulation is the most commonly used approach for digital phase/frequency modulation. This method allows for a high-quality signal to be generated because the oscillator is disassociated from the baseband signals [2]. The architecture is also very flexible. However, these advantages come at the cost of increased circuit complexity. There is the need for two DACs and two analog multipliers to accommodate the in phase and quadrature signals.

#### **Open-loop Modulation**

An architecture that eliminates the need for quadrature baseband DACs and a separate local oscillator is the open-loop modulator. Although the open-loop modulator still requires a single DAC, the architecture is simple to implement and is an attractive option for a low-cost, low-power modulator. Unfortunately, there are several problems inherent in the open-loop modulator architecture. While transmitting data, the open-loop modulator must periodically halt transmission to stabilize the center frequency of the VCO. In addition, the VCO must have a linear tuning curve to ensure that the output is not distorted. Even if the VCO has a linear tuning curve, the slope of the curve determines the bandwidth of the output signal and thus must be calibrated to control the output bandwidth.

#### Modulated Synthesis

In the modulated synthesizer, the data is modulated by switching the value of a frequency divider in the feedback path of the PLL. The data is first passed through a sigma-delta modulator to quantize the data and move the quantization noise to a high frequency. Like the open-loop modulator, the modulated synthesizer does not require as much analog circuitry as the quadrature modulator. As well, the modulated synthesizer does not suffer from the open-loop modulator's requirements of a linear VCO tuning curve and periodic frequency stabilization [3]. However, the modulated synthesizer requires a multimodulus divider and precompensation or two-point-modulation of the input signal to compensate for bandpass filtering caused by the PLL [4].

#### 1.3: Background

#### 1.3.1: Sigma-Delta Modulation

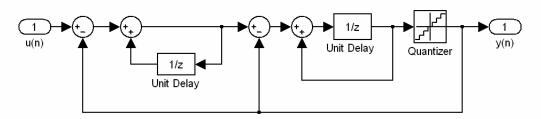

Sigma-delta modulation is most often used in oversampling D/A and A/D converters. It allows for shaping of the quantization noise to improve the signal to noise ratio in the bandwidth of interest. As with traditional oversampling converters without noise shaping, sigma-delta modulators use oversampling to spread the quantization noise over a larger frequency range. When the oversampled signal is passed through a low-pass filter, there exists a greater signal to noise ratio than if the signal had been sampled at its Nyquist rate with the same quantizer. The noise-shaping transfer function used in a sigma-delta modulator can have arbitrary order. Higher-order noise shaping results in less quantization noise power in the bandwidth of interest, but more quantization noise power overall. Figure 2 shows a discrete-time block diagram for a second-order sigma-delta modulator [5].

Figure 2. A Second-Order Sigma-Delta Modulator

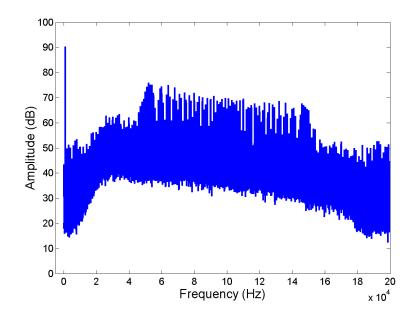

The frequency spectrum of a sigma-delta modulated signal can be seen in Figure 3. At low frequencies, the quantization noise is not significant and the sinusoid's frequency component is clearly visible. At higher frequencies, the quantization noise increases, reaching a maximum at half the sampling frequency.

Figure 3. Frequency Spectrum of a Second-Order Sigma-Delta Modulator (Input sinusoid of 1 KHz, Oversampling ratio of 200)

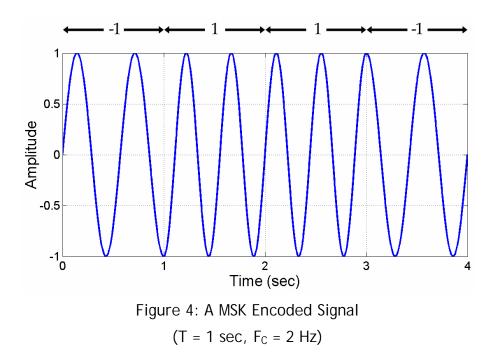

#### 1.3.2: Minimum Shift Keying (MSK)

Minimum Shift Keying is a spectrally efficient, continuous phase, continuous envelope modulation scheme [6]. In MSK, the frequency of oscillation switches between two frequencies with continuous phase. The two frequencies are spaced such that the phase of the signal increases or decreases by  $P_2$  in a baud rate period depending on whether a 1 or -1 is being transmitted. The two frequencies that represent -1 and 1 are equal to:

$$f_L = f_C - \frac{1}{4T}, \qquad \qquad f_H = f_C + \frac{1}{4T}$$

T represents the baud rate and  $f_c$  represents the carrier frequency. An MSK waveform can thus be represented by the following equation:

$$\mathbf{y}(t) = A\cos\left(2\mathbf{p}f_c t + \mathbf{q}_0 + \frac{\mathbf{p}}{2T}\int_{-\infty}^t \mathbf{f}(t)dt\right)$$

In the above equation,  $\phi(\tau)$  is either -1 or 1, representing the bit that is being transmitted. Fig. 4 shows four baud rate periods of an arbitrary MSK waveform.

Gaussian Minimum Shift Keying (GMSK) is a modulation scheme based on MSK that is used in GSM cellular phones. In GMSK, the binary data is passed through a Gaussian filter before being modulated. This filter introduces a small amount of intersymbol interference into the modulated signal but also increases the overall spectral efficiency.

#### 1.3.3: GSM (Global System for Mobile Communications)

GSM is the dominant mobile communications technology used in cellular phones. At the end of 2002, there were 787 million GSM subscribers worldwide [1]. GSM is available in a variety of technologies as shown in Table 1.

| GSM Technology      | Availability                 | Operating<br>Frequency | Channel Baud<br>Rate |

|---------------------|------------------------------|------------------------|----------------------|

| GSM 900             | Europe, Asia,<br>Australia   | 900 MHz                | 270 kb/sec           |

| GSM 1800 / DCS 1800 | Europe, Asia,<br>Australia   | 1800 MHz               | 270 kb/sec           |

| GSM 1900 / PCS 1900 | US, Canada,<br>Latin-America | 1900 MHz               | 270 kb/sec           |

| Table 1: | Current | GSM | technologies |

|----------|---------|-----|--------------|

|----------|---------|-----|--------------|

#### 1.4: Outline

Chapter 2 will outline the proposed modulation architecture and examine it from a systems perspective. The modulation architecture's advantages and disadvantages will be discussed and system-level frequency spectrum plots will be shown. A circuit implementation of the proposed architecture will be presented in Chapter 3. HSPICE circuit simulations results will be compared to the results in Chapter 2. Finally, Chapter 4 will describe a discrete implementation of the proposed modulation architecture and the experimental results of this implementation will be presented and compared with both system and circuit level simulations.

## **Proposed Modulation Architecture**

#### 2.1: Overview of Architecture

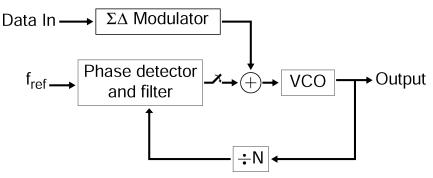

Figure 5: A Sigma-Delta Based Open-Loop Frequency Modulator

The proposed architecture, seen in Figure 5, is a sigma-delta based open-loop modulator. Like the modulated synthesizer, this approach uses a  $\Sigma-\Delta$  modulator to avoid using a DAC and thus decreases the analog circuit requirements. In a  $\Sigma-\Delta$  based open-loop modulator, the output frequency switches between a discrete set of frequencies as the output of the  $\Sigma-\Delta$  modulator switches between discrete levels. As with the traditional open-loop modulator, the loop must periodically close to stabilize the center frequency.

A drawback with using a  $\Sigma$ - $\Delta$  modulator is that its quantization noise must be filtered out before transmitting the output signal. Modulated synthesizers filter out the quantization noise by using the bandpass filtering built into the PLL. However the PLL bandwidth cannot be easily controlled as it is primarily determined by other system requirements such as frequency tracking and jitter specifications. Similar quantization noise issues arise with the  $\Sigma-\Delta$  based open-loop modulator, except that the VCO bandwidth needs to be considered instead of the PLL bandwidth. The VCO bandwidth represents the extent to which the signals outside the frequency bandwidth of interest are attenuated. This attenuation is primarily determined by how quickly the VCO can switch between frequencies. At low  $\Sigma-\Delta$  frequencies, the VCO frequency switching can be considered to be instantaneous, and thus all of the quantization noise is passed to the output of the PLL. However, when the  $\Sigma-\Delta$  modulator frequency becomes sufficiently high, the VCO frequency switching time becomes significant and the VCO can ideally act as a bandpass filter, filtering out the quantization noise.

#### 2.2: Advantages

#### 2.2.1: VCO Linearity

When a one-bit  $\Sigma$ - $\Delta$  modulator is used, the VCO only switches between two frequencies and the tuning curve of the VCO is assured to be linear, regardless of the linearity of the tuning device. In traditional open-loop modulators, high quality varactors are needed to achieve a linear tuning curve. Even though a one-bit  $\Sigma$ - $\Delta$  modulator can ensure a linear VCO tuning curve, it is still necessary to control the slope of the tuning curve, which defines the output bandwidth.

#### 2.2.2: Adder Simplification

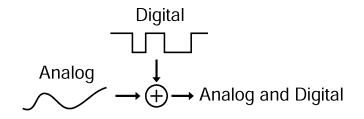

The  $\Sigma$ - $\Delta$  based frequency modulator can be thought of essentially the same as the open-loop modulator in Figure 1.B) except that the low-pass filter in the DAC has been removed. Even though this low-pass filter is relatively trivial to implement, by removing it there are significant repercussions throughout the rest of the PLL. One such repercussion is that the adder design can be simplified. Instead of adding two analog signals together, the adder needs to only add an analog with a digital signal. This simplification is shown in Figure 6. Due to the negative feedback of the PLL when the loop is closed, it is not necessary for the adder to be perfectly linear. However, the adder would need to be linear if a multi-bit  $\Sigma$ - $\Delta$  modulator was used.

Figure 6: Adder Simplification due to the  $\Sigma$ - $\Delta$  modulator

#### 2.3: Disadvantages

As stated in 2.1, a drawback with using a  $\Sigma$ - $\Delta$  modulator is that its quantization noise must be filtered out before transmitting the output signal. By examining the power spectrum of a GSM signal, one can determine what  $\Sigma$ - $\Delta$  modulator frequency is necessary to ensure a sufficiently large signal-to-noise ratio in the bandwidth of interest. Figure 7 shows the power spectrum of random data and Gaussian filtered random data.

Figure 7: Power spectrum of random data and Gaussian filtered random data (Frequency axis normalized to half the data rate)

The Gaussian filters used in Figure 7 and in GMSK have a -3 dB frequency of  $0.3F_{data}$ . Because the Gaussian filtered power spectrum is significantly attenuated at frequencies greater than  $0.5F_{data}$ , the oversampling ratio, M, can be considered to equal  $\frac{F_s}{0.5F_{data}}$ . By increasing the  $\Sigma$ - $\Delta$  modulator frequency, the quantization noise is moved farther away from the carrier frequency and the PLL is able to filter out more of this noise. However, power consumption in digital circuits is proportional to the square of frequency and circuit complexity increases as the  $\Sigma$ - $\Delta$  modulator frequency at which the wireless standards are met. For example, the GSM standard requires that spurious emissions are less than -83 dBc/Hz for frequencies 0.2 to 0.4 MHz away from the carrier frequency [7].

#### 2.4: Frequency Analysis

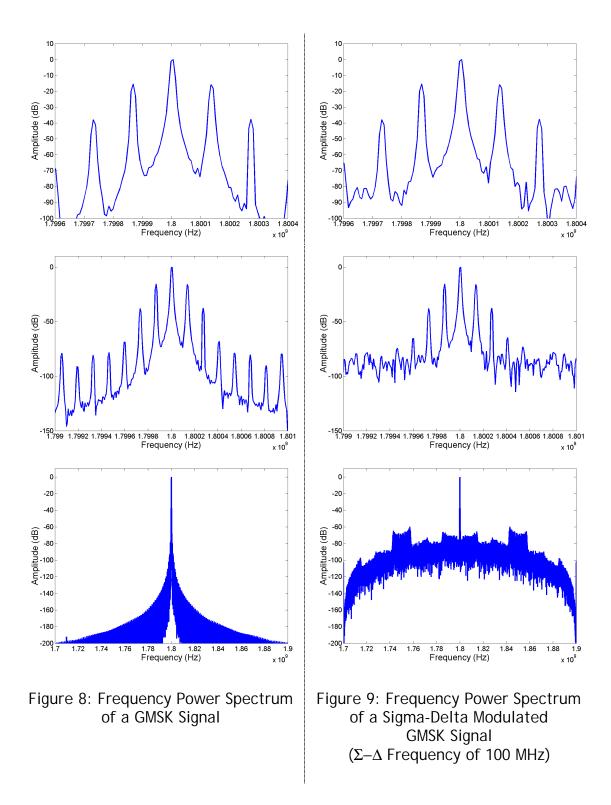

The frequency power spectrums of a GMSK signal and a second-order, single-bit  $\Sigma - \Delta$  modulated GMSK signal are shown in Figure 8 and Figure 9. The oversampling ratio for the  $\Sigma - \Delta$  modulated GMSK signal is approximately 740 (100 MHz clock frequency, 270/2 = 135 kHz signal bandwidth). Nearby the carrier frequency, the quantization noise floor is 90 dB below the main peak. The quantization noise reaches its maximum value 50 MHz from the carrier frequency (corresponding to half the clock frequency), 60 dB below the main peak.

#### 2.5: System Analysis of PLL

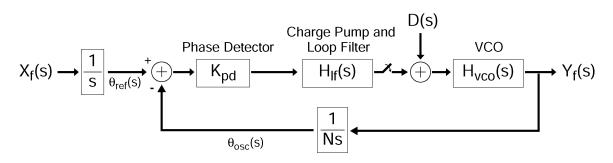

One important design consideration in the design of a PLL for a sigma-delta based frequency synthesizer is the bandwidth of the VCO. In direct modulation, where the data enters directly into the VCO, the bandwidth of the VCO can significantly affect the quantization noise of the input signal. Figure 10 shows the linearized system diagram of a PLL.

Figure 10: Linearized system diagram of a PLL

Traditionally, analysis of the PLL is conducted by examining the phases of the input and output signals. However, when analyzing open-loop effects in a PLL, it can be useful to examine frequencies instead. Thus,  $X_f(s)$  and  $Y_f(s)$  represent the frequencies of the reference signal and oscillator, respectively.

The phase/frequency detector is modelled as a gain block,  $K_{pd}$ , that amplifies or attenuates the difference in phase between the output  $Y_f(s)$  and the reference  $X_f(s)$ .  $\theta_{ref}$  and  $\theta_{osc}$  represent the phases. N is the feedback frequency divider value.

The charge pump and loop filter are represented by the transfer function  $H_{lf}(s)$ .  $H_{lf}(s)$  typically has two poles and one zero. The lower frequency pole,  $w_{p1}$ , determines the bandwidth of the PLL and the zero,  $w_z$ , improves the stability and tracking of the loop. The high frequency pole,  $w_{p2}$ , removes some non-ideal effects and can be neglected in this analysis.

$$H_{lf}(s) = \frac{1 + \frac{s}{w_z}}{\left(1 + \frac{s}{w_{p1}}\right)\left(1 + \frac{s}{w_{p2}}\right)} \approx \frac{1 + \frac{s}{w_z}}{1 + \frac{s}{w_{p1}}}$$

In some applications the low frequency pole,  $w_{p1}$ , is moved to dc:

$$H_{lf}(s) = \frac{1 + \frac{s}{w_z}}{s\left(1 + \frac{s}{w_{p2}}\right)} \approx \frac{1 + \frac{s}{w_z}}{s}$$

The VCO block in Figure 10 converts a voltage to a frequency. Typically the VCO is represented by a gain block, K<sub>VCO</sub>. This is because in a closed-loop PLL configuration, the only input into the VCO block comes from the loop filter, and this input typically does not have any high frequency components. Because the input is over a narrow frequency range, the frequency response of the VCO can be assumed to be uniform. However, when D(s) is a sigma-delta modulated input, the control voltage into the VCO now has high frequency components. Thus, high-frequency characteristics of the VCO must be considered. Various second and third-order models exist for the VCO that affect its frequency switching response [8]. In one of its simplest forms, the VCO can be modelled as a low-pass filter, with a -3dB frequency that is significantly greater than the -3dB frequency of the charge pump and loop filter.

$$H_{vco}(s) = \frac{K_{vco}}{1 + \frac{s}{w_{vco}}}$$

Direct modulation can be implemented in both an open and closed-loop configuration. In an open-loop configuration, the loop alternates between transmitting data and locking the carrier frequency. In a closed-loop configuration, locking of the carrier frequency occurs at the same time as transmitting data.

#### **Open-Loop Configuration**

Section 1.2 provided an introduction to open-loop modulation and its advantages and disadvantages. The system analysis of open-loop direct modulation is relatively straightforward. When data is being transmitted, the transfer function from D(s) to  $Y_f(s)$  is  $H_{VCO}(s)$ . The only design consideration is to ensure that the sigma-delta modulation quantization noise is sufficiently attenuated by  $H_{VCO}(s)$  and spread over a wide enough bandwidth so that the transmission quality meets specifications. If this can not be achieved, an additional bandpass filter may be required prior to transmission.<sup>1</sup> The rest of the PLL is designed in a traditional manner for good locking characteristics.

#### Closed-Loop Configuration

The analysis and design of the PLL in a closed-loop configuration is more complicated than in an open-loop configuration because the loop must be able to stay in lock at the same time as it is transmitting data. The benefit of this approach is that there is no longer the need to periodically halt transmission and close the loop to lock the carrier frequency.

In a closed-loop configuration, the transfer function from D(s) to  $Y_f(s)$  is:

$$\frac{Y_f(s)}{D(s)} = \frac{Hvco(s)}{1 + (Ns)^{-1}Hvco(s)K_{PD}H_{lf}(s)} = \frac{sNHvco(s)}{sN + Hvco(s)K_{PD}H_{lf}(s)}$$

At low frequencies  $(s \approx 0)$ , it can be seen that  $\frac{Y_f(s)}{D(s)} \approx 0$ .

At high frequencies  $(s \to j\infty)$ , it can be seen that  $\frac{Y_f(s)}{D(s)} \approx H_{VCO}(s)$ .

Assuming that  $H_{VCO}(s)$  has a low pass response, the transfer function from the data input to the frequency output is bandpass with a lower -3dB cutoff frequency of  $w_L$ . If we only consider the low frequency pole and zero of the loop filter, we can obtain an expression for  $w_L$  (See Appendix A):

<sup>&</sup>lt;sup>1</sup> In some systems, this may already be present.

$$w_{L} = \sqrt{-0.5b + 0.5\sqrt{b^{2} + 4N^{-2}K_{VCO}^{2}K_{PD}^{2}w_{p1}^{2}}}$$

where  $b = 2w_{p1}^{2} + 2K_{VCO}K_{PD}N^{-1}w_{p1} - \left(w_{p1} + \frac{K_{VCO}K_{PD}w_{p1}}{Nwz}\right)^{2}$

For applications where the low frequency pole is located at dc, we have the following expression for  $w_L$ :

$$w_{L} = \sqrt{-0.5b + 0.5\sqrt{b^{2} + 4N^{-2}K_{VCO}^{2}K_{PD}^{2}}}$$

where  $b = 2K_{VCO}K_{PD}N^{-1} - \left(\frac{K_{VCO}K_{PD}}{N_{WZ}}\right)^{2}$

For the data D(s) to be transmitted at the output, it is important that its frequency spectrum lie between  $w_L$  and  $w_{VCO}$ . Otherwise, the signal will be attenuated. The signal will be bandlimited below  $w_{VCO}$  by the Gaussian filter, and simple coding can be applied to the data stream to ensure it has no dc content.

#### Analyzing a typical PLL in a closed-loop configuration

An existing 1.4 GHz GMSK modulator has the following PLL specifications:

| W <sub>p1</sub>  | Located at dc                   |

|------------------|---------------------------------|

| W <sub>p2</sub>  | $2\pi \times 148 \text{ kHz}$   |

| WZ               | $2\pi \times 12.5 \text{ kHz}$  |

| K <sub>VCO</sub> | $2\pi \times 200 \text{ MHz/V}$ |

| K <sub>PD</sub>  | 1 V/rad (assumed)               |

| N                | 87.5                            |

Table 2: PLL specifications from [9]

$w_{vco}$  is assumed to be 100 MHz.

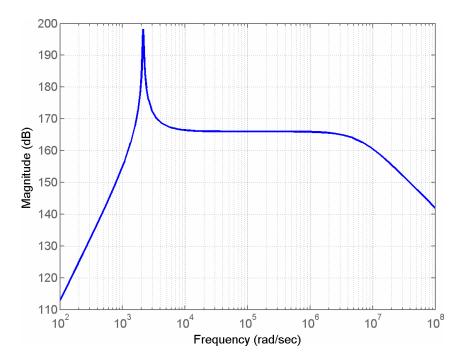

Using these values,  $w_L$  is calculated to be  $2\pi \times 219$  Hz. This value of  $w_L$  agrees with the simulated bode plot for the closed-loop PLL shown in Figure 11. The magnitude peaking near  $w_L$  can be prevented by lowering the zero frequency,  $w_Z$ . If the data stream is encoded to have no components at frequencies near  $w_L$ , this magnitude peaking is not a problem.

Figure 11: Bode plot of  $Y_f(s)/D(s)$  for the PLL in a closed-loop configuration

## **Circuit Implementation**

#### 3.1: Overview

To verify the feasibility of the proposed modulation architecture, a voltagecontrolled oscillator circuit for use in a GSM 1800 transceiver was designed in CMOS 0.35  $\mu$ m technology. A sigma-delta modulated signal was direct modulated by the oscillator in an open-loop configuration and frequency spectrum plots were found to match the simulated plots in Chapter 2.

#### 3.2: Voltage-Controlled Oscillator

#### 3.2.1: Overall circuit

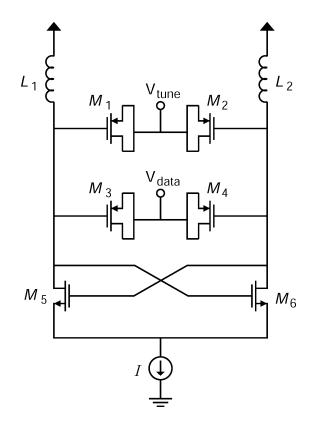

The voltage-controlled oscillator was an LC oscillator designed in CMOS 0.35  $\mu$ m technology. An LC oscillator was used instead of a ring oscillator because the GSM specifications require very little phase noise [10]. A differential oscillator was implemented to reduce the effect of DC offsets. The oscillator operated with a power supply voltage of 2.5 V and required 20 mW of power. Tuning of the oscillator was accomplished using PMOS based capacitors. Figure 12 shows the circuit diagram of the differential LC oscillator that was used.

Figure 12: Circuit diagram of differential LC oscillator

| $L_{1}, L_{2}$                  | 3 nF             |

|---------------------------------|------------------|

| $M_1, M_2$                      | L = 1.4 μm       |

|                                 | W = 10 µm (x 40) |

| M <sub>3</sub> , M <sub>4</sub> | L = 0.7 μm       |

|                                 | W = 1 μm         |

| M <sub>5</sub> , M <sub>6</sub> | L = 0.35 μm      |

|                                 | W = 10 μm        |

| Ι                               | 8 mA             |

Table 3: Values for Figure 12

#### 3.2.2: On-chip inductor

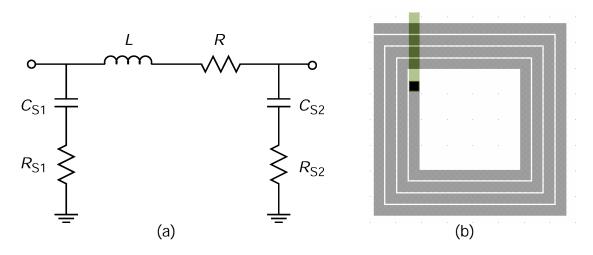

For accurate simulation results, on-chip inductors were modelled using Asitic, CAD software that can model spiral inductors in integrated circuits [11]. Although it was assumed that the inductors were isolated from one another, the inductors could have been cross-coupled together, thereby increasing the Q of each inductor and reducing the phase noise of the oscillator [12]. The differential LC oscillator could have also been implemented with a single inductor, as described in [13].

Figure 13: (a) Circuit diagram and (b) layout of the modelled on-chip inductor

| L                     | 2.95 nH   |

|-----------------------|-----------|

| R                     | 7.45 Ω    |

| C <sub>S1</sub>       | 60.4 fF   |

| C <sub>S2</sub>       | 60.5 fF   |

| R <sub>S1</sub>       | 1.89 Ω    |

| R <sub>S2</sub>       | 0.374 Ω   |

| Q                     | 4.38      |

| F <sub>resonant</sub> | 11.91 GHz |

Table 4: Values for the on-chip inductor

#### 3.2.3: Tuning characteristics

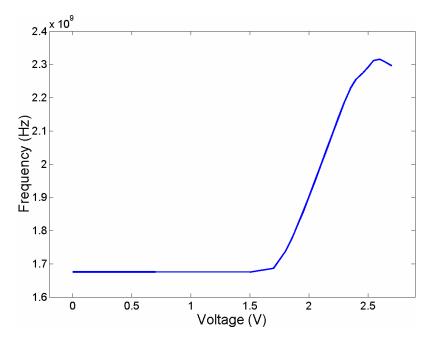

Frequency tuning of the oscillator was accomplished using PMOS transistors  $M_1$ ,  $M_2$ ,  $M_3$  and  $M_4$  in Figure 12. Transistors  $M_1$  and  $M_2$  were responsible for broad tuning of the VCO from 1.7 GHz to 2.2 GHz. Figure 14 shows the broad tuning curve of the VCO for input voltages ranging from 0 V to 2.5 V.

Figure 14: Broad tuning curve of the VCO

Transistors  $M_3$  and  $M_4$  were responsible for the narrow frequency switching due to the  $\Sigma-\Delta$  modulator. When using a one-bit  $\Sigma-\Delta$  modulator,  $V_{data}$  would switch between 0 V and 2.5 V depending on the output of the modulator. The VCO would then switch between two frequencies,  $f_1$  and  $f_2$ , as seen in Figure 15. To improve the effective resolution of the  $\Sigma-\Delta$  modulator, it is important to keep the difference between frequencies  $f_1$  and  $f_2$  not significantly greater than the bandwidth of the signal being transmitted. In GSM, the channel bandwidth is 200 kHz, and thus frequencies  $f_1$  and  $f_2$  were spaced approximately 1 MHz apart. This was accomplished by choosing sufficiently small transistor sizes of  $M_3$  and  $M_4$  in relation to  $M_1$  and  $M_2$ .

In existing implementations of direct modulators, the VCO tuning curve is assumed to be linear over small changes in the input voltage. For an input voltage between 1.7 V and 2.5 V, the tuning curve seen in Figure 15 is relatively linear. However, perfect linearity cannot be achieved without digital precompensation of the input signal and complete characterization of the

tuning curve. A one-bit  $\Sigma$ - $\Delta$  modulator results in a linear tuning curve regardless of the linearity of the tuning device that is used.

Figure 15: Fine tuning curve of the VCO

#### 3.3: Circuit Simulations

#### 3.3.1: Instantaneous frequency switching of VCO

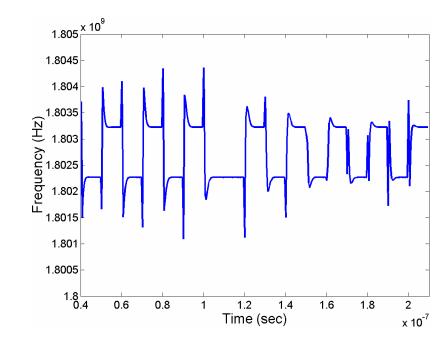

An important design consideration in the proposed modulation architecture is how the VCO responds to instantaneous changes in frequencies. If the VCO slowly changes between frequencies, then it has a low-pass response and the high frequency components of the input into the VCO are filtered out. If the VCO overshoots when switching between frequencies, then some highfrequency components of the input are amplified. Figure 16 shows the instantaneous frequency response of the differential LCO when driven by a  $\Sigma$ - $\Delta$ modulator at 100 MHz. In the figure, it can be seen that the frequency switching characteristic of the VCO varies with time. This is because the frequency switches, the oscillator overshoots by 40%. At other times, the oscillator has almost no overshoot. Since the frequency response is clearly not low-pass, one cannot assume that the VCO will filter out the  $\Sigma-\Delta$  modulator quantization noise. Therefore, it is desirable to use a high oversampling ratio in the  $\Sigma-\Delta$  modulator to spread out the quantization noise. Other bandpass filtering may be required throughout the transmitter to further attenuate the quantization noise, possibly by implementing a narrowband power amplifier or a narrowband antenna.

Figure 16: Instantaneous frequency response of the VCO

#### 3.2.2: Frequency spectrum plots

A  $\Sigma-\Delta$  modulated input of Gaussian filtered alternating 1's and -1's was inputted into the VCO to generate a GMSK waveform. Frequency spectrum plots of this waveform for  $\Sigma-\Delta$  modulator frequencies of 10 MHz and 100 MHz are shown in Figure 17 and Figure 18. The frequency plots shown in Figure 18 closely match the ideal MATLAB simulated frequency plots shown in Figure 9. By increasing the  $\Sigma-\Delta$  modulator frequency, the quantization noise is attenuated as expected. With a  $\Sigma-\Delta$  frequency of 100 MHz, the quantization noise has a maximum value of -50 dB compared to a maximum value of -25 dB with a  $\Sigma-\Delta$  frequency of 10 MHz.

Figure 17: Frequency spectrum plots of GMSK output  $(\Sigma - \Delta$  Frequency of 10 MHz)

Figure 18: Frequency spectrum plots of GMSK output ( $\Sigma$ - $\Delta$  Frequency of 100 MHz)

## **Experimental Results**

#### 4.1: Overview

To test the feasibility of the proposed modulation architecture, a voltagecontrolled oscillator was prototyped on a two-sided printed circuit board using discrete components. For simplicity, narrowband frequency/phase modulation was implemented *a*t a carrier frequency of 120 MHz. The voltage-controlled oscillator was implemented using a single-ended Colpitts LC oscillator as shown in Figure 19.

Figure 19: Single-ended Colpitts LC oscillator

| L <sub>1</sub>    | 20 nH   |

|-------------------|---------|

| C <sub>1</sub>    | 39 pF   |

| C <sub>2</sub>    | 270 pF  |

| I <sub>1</sub>    | 57.2 μΑ |

| I <sub>2</sub>    | 3.07 mA |

| V <sub>bias</sub> | 1.8 V   |

Table 5: Values for the single-ended LC oscillator

The printed circuit board was constructed using a milling machine and the discrete transistors used were Intersil HFA 3127 ultra-high frequency transistor arrays. Figure 20 shows a picture of the printed circuit board.

Figure 20: Printed Circuit Board

A 4 kHz sinusoid was passed through a second-order, one-bit  $\Sigma - \Delta$  modulator at various oversampling ratios. To reduce the complexity of the PCB, the  $\Sigma - \Delta$  modulation was done in MATLAB and then imported into a function generator. The  $\Sigma - \Delta$  modulated data from the function generator switched the bias current through the oscillator, thereby switching the oscillation frequency between the two frequencies shown in Figure 21.

Figure 21: (A) Lower frequency and (B) upper frequency that the oscillator switched between

#### 4.2: Frequency Spectrum Plots

Figure 22 shows the narrow band and wide band output frequency spectrums when the  $\Sigma-\Delta$  modulator was clocked at 1 MHz. As expected, the  $\Sigma-\Delta$  quantization noise is at a minimum at the carrier frequency and at 1 MHz away from the carrier frequency.

To reduce the quantization noise in the output, the  $\Sigma-\Delta$  frequency was increased. Figure 23 shows the narrow band and wide band frequency spectrums when the  $\Sigma-\Delta$  modulator was clocked at 10 MHz. Over a narrow bandwidth, the frequency spectrums in Figure 22 and Figure 23 look identical. However, Figure 23.b) has significantly less quantization noise visible than Figure 22.b). This can be explained due to two reasons. A 10 MHz  $\Sigma-\Delta$  modulator still generates quantization noise, but at a frequency sufficiently far away from the carrier frequency such that the noise is filtered out by the VCO. As well, with a higher frequency  $\Sigma-\Delta$  modulator, the quantization noise is spread over a larger frequency range.

## Conclusion

#### 5.1: Summary

A constant-envelope, continuous phase modulation architecture was presented in which a sigma-delta modulator is combined with a direct modulator. The main advantages of this architecture are that linearity of the oscillator's tuning device is ensured and implementation is simplified due to the use of discrete frequency switching in the oscillator. The main disadvantage is that the quantization noise introduced by the  $\Sigma$ - $\Delta$  modulator must be filtered out or spread out to ensure wireless noise specifications are met.

In Chapter 2, the architecture was analyzed from a systems perspective in both open-loop and closed-loop configurations. The instantaneous frequency response of the VCO was found to be an important design consideration. In Chapter 3, the architecture was simulated in an open-loop configuration implementing GMSK modulation for use in a GSM transceiver. A prototype, low-frequency implementation of the modulation architecture was constructed and experimental results were presented in Chapter 4. By increasing the  $\Sigma-\Delta$  modulation frequency, the quantization noise was filtered out by the VCO and disappeared beneath the measurement noise floor.

#### 5.2: Future Work

One area of future work is designing an integrated PLL and fully-differential VCO on-chip that is capable of implementing the proposed modulation architecture in both an open-loop and closed-loop configuration. Other areas of research include investigating multi-bit or bandpass  $\Sigma-\Delta$  modulators in this

30

architecture and designing a VCO that has a narrowband instantaneous frequency response to aid in filtering out the quantization noise.

#### References

- [1] "GSM Association: Membership and Market Statistics," January 14, 2003. Available at <u>http://www.gsmworld.com</u>

- [2] T. Melly, A. Porret, C. C. Enz, and E. A. Vittoz, "An Ultralow-Power UHF Transceiver Integrated in a Standard Digital CMOS Process: Transmitter," *IEEE J. Solid-State Circuits*, vol. 36, pp. 467-472, March 2001.

- [3] D. R. McMahill and C. G. Sodini, "Automatic Calibration of Modulated Frequency Synthesizers," *IEEE Trans. Circuits Syst. II*, vol. 49, pp. 301-311, May 2002.

- [4] B. Neurauter, G. Märzinger, A. Schwarz, R. Vuketich, M. Scholz, R. Weigel and J. Fenk, "GSM 900/DCS 1800 Fractional-N Modulator with Two-Point-Modulation," *2002 IEEE MTT-S Digest*, pp. 425-428

- [5] D. Johns and K. Martin, *Analog Integrated Circuit Desig*n, New York, John Wiley & Sons, 1997, pp 544.

- [6] S. Pasupathy, "Minimum Shift Keying; A Spectrally Efficient Modulation", *IEEE Communications Magazine*, vol. 17, pp. 14-22, July 1979.

- [7] C. Chien, *Digital Radio Systems on a Chip*, Boston, Kluwer Academic Publishers, 2001, pp. 443.

- [8] A. Shibutani, T. Saba, S. Moro and S. Mori, "Transient Response of Colpitts-VCO and Its Effect on Performance of PLL System," *IEEE Trans. Circuits Syst. 1*, vol. 45, pp. 717-725, July 1998.

- [9] H. Zarei, O. Shoaei, S. Fakhraie, "A 37-mW Fully Integrated GMSK Modulator for DRRS Standard in 0.6-mm Digital CMOS Process," *IEEE Trans. Circuits Syst. II*, vol. 49, pp. 513-520, July 2002.

- [10] C.M. Hung and K. K. O., "A Packaged 1.1-GHz CMOS VCO with Phase Noise of -126 dBc/Hz at a 600-kHz Offset," *IEEE J. Solid-State Circuits*, vol. 35, pp. 100-103, January 2000.

- [11] A. M. Niknejad and R. G. Meyer, "Analysis, Design, and Optimization of Spiral Inductors and Transformers for Si RF IC's," *IEEE J. Solid-State Circuits*, vol. 33, pp. 1470-81, October 1998.

- [12] M. Danesh and J. R. Long, "Differentially Driven Symmetric Microstrip Inductors," *IEEE Trans. Microwave Theory and Techniques*, vol. 50, pp. 332-341, January 2002.

- [13] S. Cho and A. P. Chandrakasan, "A 6.5 GHz CMOS FSK Modulator for Wireless Sensor Applications," Symposium on VLSI Circuits, pp. 182-185, 2002.

## **Appendix A: PLL Closed-Loop Calculations**

Assuming that  $H_{VCO}(s)$  has a low pass response, the transfer function from the data input to the frequency output is bandpass with a lower -3dB cutoff frequency of  $w_L$ . Solving for  $w_L$ :

$$|H_{VCO}(s)K_{PD}H_{if}(s) + Ns| = |\sqrt{2}Ns|$$

$$|H_{VCO}(jwL)K_{PD}H_{if}(jwL) + jNwL| = \sqrt{2}N_{WL}$$

If we only consider the low frequency pole and zero of the loop filter:

$$\frac{\left|\frac{KvcoK_{PD}\left(1+\frac{jwL}{wz}\right)}{\left(1+\frac{jwL}{wp1}\right)}+jNwL\right|}{\left(1+\frac{jwL}{wp1}\right)}+jNwL\right|} = \sqrt{2}NwL$$

$$\frac{\left|\frac{KvcoK_{PD}}{wL}+j\frac{KvcoK_{PD}}{wZ}-\frac{NwL}{wp1}+Nj}{\left(1+\frac{jwL}{wp1}\right)}\right|}{\left(1+\frac{jwL}{wp1}\right)}=\sqrt{2}NwL$$

$$\frac{\left|\frac{KvcoK_{PD}}{wL}-\frac{NwL}{wp1}+j\left(N+\frac{KvcoK_{PD}}{wZ}\right)}{\left(1+\frac{jwL}{wp1}\right)}\right|}{\left(1+\frac{jwL}{wp1}\right)}=\sqrt{2}N$$

$$\frac{\sqrt{\left(\frac{KvcoK_{PD}}{wL}-\frac{NwL}{wp1}\right)^{2}+\left(N+\frac{KvcoK_{PD}}{wZ}\right)^{2}}}{\sqrt{\left(\frac{wL}{wp1}\right)^{2}+1}}=\sqrt{2}N$$

This is a quadratic equation in terms of  $w_L^2$ . Expanding in terms of  $w_L^2$ :

$$\left(\frac{K_{VCO}K_{PD}}{w_L} - \frac{Nw_L}{w_{P1}}\right)^2 + \left(N + \frac{K_{VCO}K_{PD}}{w_Z}\right)^2 = 2N^2 \left(\frac{w_L}{w_{P1}}\right)^2 + 2N^2$$

$$K_{VCO}^2 K_{PD}^2 + \frac{N^2}{w_{P1}^2} w_L^4 - \frac{2K_{VCO}K_{PD}N}{w_{P1}} w_L^2 + \left(N + \frac{K_{VCO}K_{PD}}{w_Z}\right)^2 w_L^2 = \frac{2N^2}{w_{P1}^2} w_L^4 + 2N^2 w_L^2$$

$$\frac{N^{2}}{w_{p1}^{2}}w_{L}^{4} + \left(2N^{2} + \frac{2K_{VCO}K_{PD}N}{w_{p1}} - \left(N + \frac{K_{VCO}K_{PD}}{w_{Z}}\right)^{2}\right)w_{L}^{2} - K_{VCO}^{2}K_{PD}^{2} = 0$$

$$w_{L}^{4} + \left(2w_{p1}^{2} + 2K_{VCO}K_{PD}N^{-1}w_{p1} - \left(w_{p1} + \frac{K_{VCO}K_{PD}w_{p1}}{Nw_{Z}}\right)^{2}\right)w_{L}^{2} - N^{-2}K_{VCO}^{2}K_{PD}^{2}w_{p1}^{2} = 0$$

Solving the quadratic equation:

$$w_{L}^{2} = -0.5 \left( 2w_{p1}^{2} + 2K_{VCO}K_{PD}N^{-1}w_{p1} - \left(w_{p1} + \frac{K_{VCO}K_{PD}w_{p1}}{Nwz}\right)^{2} \right)$$

$$\pm 0.5 \sqrt{\left( 2w_{p1}^{2} + 2K_{VCO}K_{PD}N^{-1}w_{p1} - \left(w_{p1} + \frac{K_{VCO}K_{PD}w_{p1}}{Nwz}\right)^{2} \right)^{2} + 4N^{-2}K_{VCO}^{2}K_{PD}^{2}w_{p1}^{2}}$$

Since  $w_L$  must be positive and real:

$$w_{L} = \sqrt{-0.5b + 0.5\sqrt{b^{2} + 4N^{-2}K_{VCO}^{2}K_{PD}^{2}w_{p1}^{2}}}$$

where  $b = 2w_{p1}^{2} + 2K_{VCO}K_{PD}N^{-1}w_{p1} - \left(w_{p1} + \frac{K_{VCO}K_{PD}w_{p1}}{Nwz}\right)^{2}$

If we instead assume that the low frequency loop filter pole is placed at dc, we can conduct a similar analysis:

$$H_{lf}(s) = \frac{1 + \frac{s}{w_z}}{s}$$

$$\frac{\left|\frac{K_{VCO}K_{PD}\left(1+\frac{jw_L}{w_Z}\right)}{jw_L}+jNw_L\right|}{=\sqrt{2}Nw_L}$$

$$\frac{\left|\frac{K_{VCO}K_{PD}}{w_L}+j\frac{K_{VCO}K_{PD}}{w_Z}-Nw_L}{jw_L}\right|}{w_L}=\sqrt{2}Nw_L$$

$$\frac{\left|\frac{K_{VCO}K_{PD}}{w_L}-Nw_L+j\frac{K_{VCO}K_{PD}}{w_Z}}{jw_L}\right|}{jw_L}=\sqrt{2}N$$

$$\frac{\left(\frac{K_{VCO}K_{PD}}{w_L}-Nw_L\right)^2+\left(\frac{K_{VCO}K_{PD}}{w_Z}\right)^2}{w_L}}{w_L}=\sqrt{2}N$$

This is a quadratic equation in terms of  $w_L^2$ . Expanding in terms of  $w_L^2$ :

$$\left(\frac{K_{VCO}K_{PD}}{w_{L}} - Nw_{L}\right)^{2} + \left(\frac{K_{VCO}K_{PD}}{w_{Z}}\right)^{2} = 2N^{2}w_{L}^{2}$$

$$K_{VCO}^{2}K_{PD2}^{2} + N^{2}w_{L}^{4} - 2K_{VCO}K_{PD}Nw_{L}^{2} + \left(\frac{K_{VCO}K_{PD}}{w_{Z}}\right)^{2}w_{L}^{2} = 2N^{2}w_{L}^{4}$$

$$N^{2}w_{L}^{4} + \left(2K_{VCO}K_{PD}N - \left(\frac{K_{VCO}K_{PD}}{w_{Z}}\right)^{2}\right)w_{L}^{2} - K_{VCO}^{2}K_{PD}^{2} = 0$$

$$w_{L}^{4} + \left(2K_{VCO}K_{PD}N^{-1} - \left(\frac{K_{VCO}K_{PD}}{Nw_{Z}}\right)^{2}\right)w_{L}^{2} - N^{-2}K_{VCO}^{2}K_{PD}^{2} = 0$$

Solving the quadratic equation:

$$wL^{2} = -0.5 \left( 2K_{VCO}K_{PD}N^{-1} - \left(\frac{K_{VCO}K_{PD}}{N_{WZ}}\right)^{2} \right)$$

$$\pm 0.5 \sqrt{\left( 2K_{VCO}K_{PD}N^{-1} - \left(\frac{K_{VCO}K_{PD}}{N_{WZ}}\right)^{2} \right)^{2} + 4N^{-2}K_{VCO}^{2}K_{PD}^{2}}$$

Since  $w_{\!L}$  must be positive and real:

$$w_{L} = \sqrt{-0.5b + 0.5\sqrt{b^{2} + 4N^{-2}K_{VCO}^{2}K_{PD}^{2}}}$$

where  $b = 2K_{VCO}K_{PD}N^{-1} - \left(\frac{K_{VCO}K_{PD}}{N_{WZ}}\right)^{2}$