Session RMO3B-2 A 38-Gb/s 2-tap Transversal Equalizer in 0.13-µm CMOS using a Microstrip Delay Element George Ng and Anthony Chan Carusone

Dept. of Electrical & Computer Engineering University of Toronto 10 King's College Rd., Toronto, Ontario, M5S 3G4, Canada

## Outline

- Motivation

- 2-tap FIR equalizer topologies

- Circuit design

- Measurement results

- Conclusion

## Motivation

- Frequency dependent channel losses results in inter-symbol interference (ISI) at receiver

- A simple 2-tap finite impulse response (FIR) equalizer can be used to compensate the channel losses

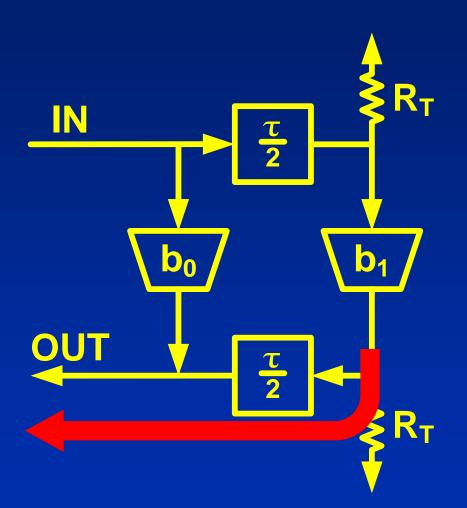

# **Traveling Wave Filter**

- Compensates for reflections due to termination impedance mismatch

- Difficult to get gain due to output side delay element

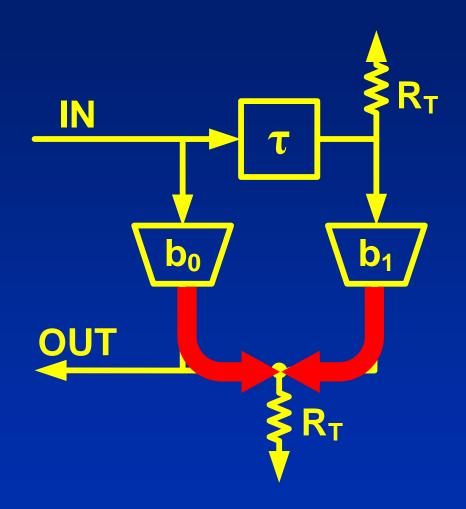

## **Transversal Filter**

- Cannot easily compensate for termination mismatch reflections

- Offers gain advantage due to colocation of tap outputs

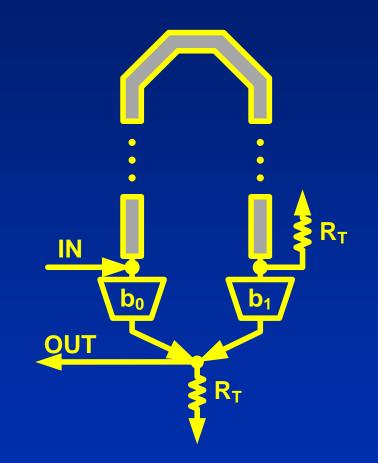

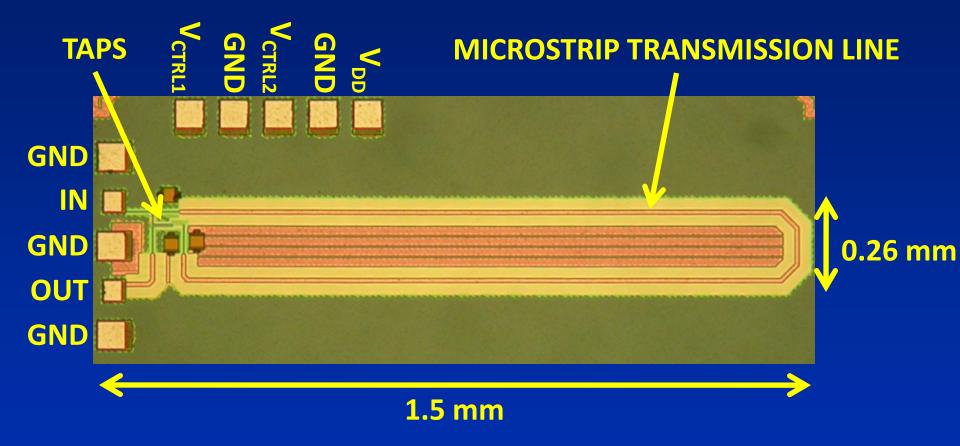

# **Microstrip Passive Delay Line**

- "U" shape simplifies routing to taps

- Easier to accommodate metal fill rules

- Higher bandwidth than lumped L-C delay line

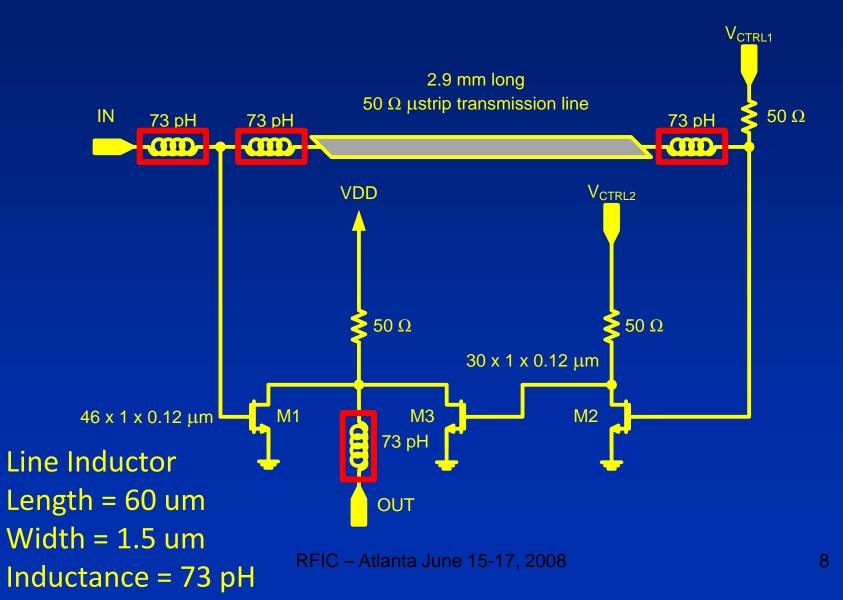

## **2-Tap Transversal Equalizer**

### **Unloaded Microstrip Line**

RFIC – Atlanta June 15-17, 2008

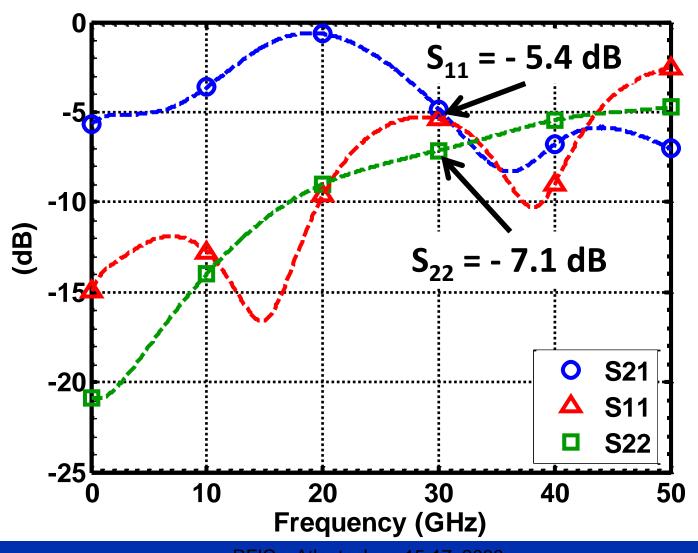

### **2-Tap without Line Inductors**

RFIC – Atlanta June 15-17, 2008

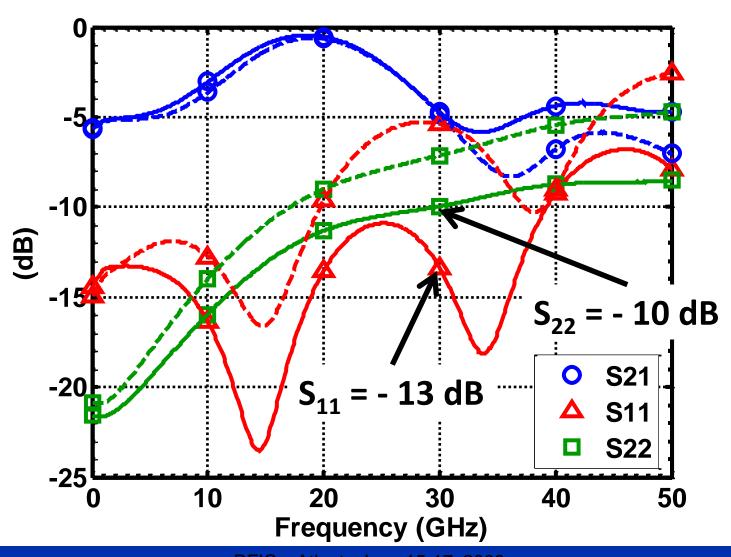

### **2-Tap with Line Inductors**

RFIC – Atlanta June 15-17, 2008

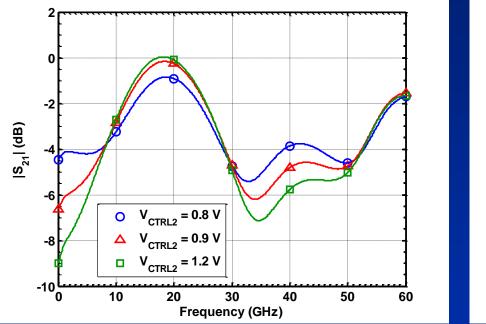

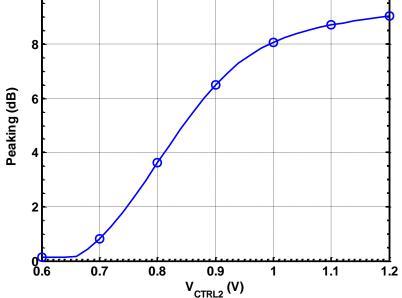

# **Simulated Peaking**

$S_{21}$  versus frequency

Peaking at maximum frequency versus peaking control voltage  $(V_{CTRL2})$

10

#### UMC 0.13-µm CMOS process

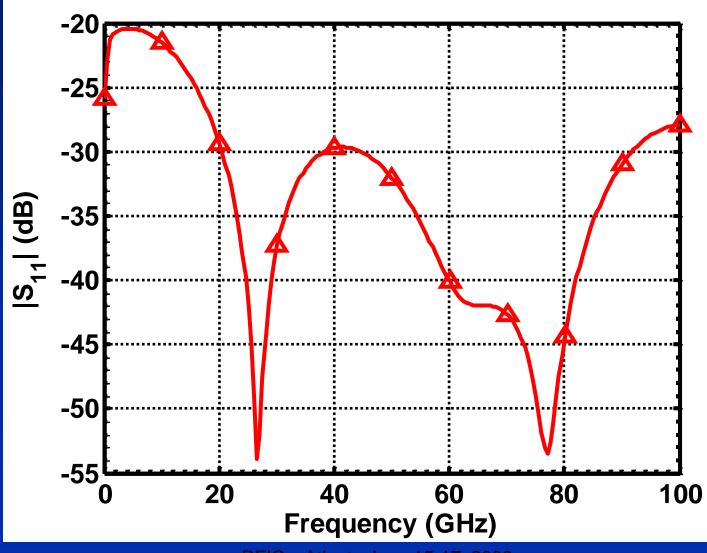

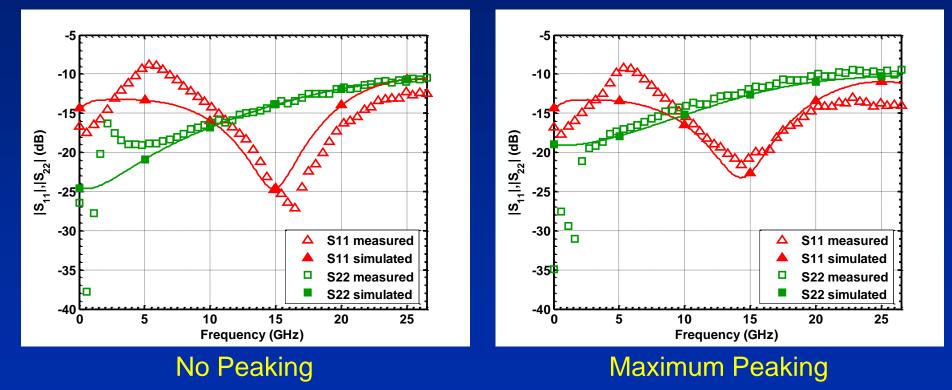

# **S-Parameter Matching**

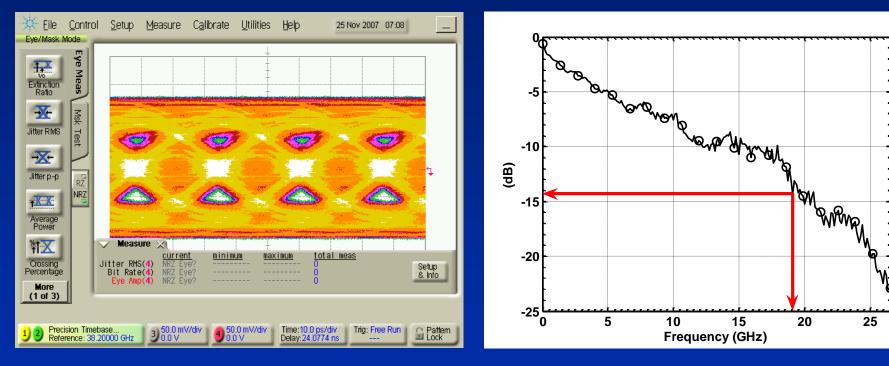

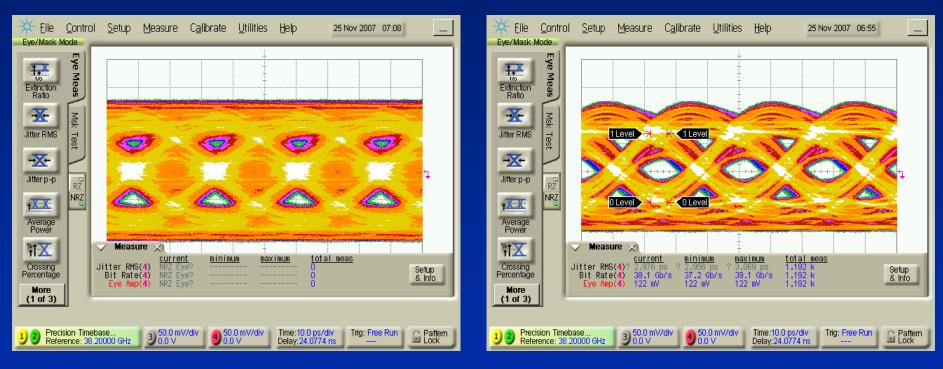

## Eye Diagrams – 38 Gb/s

Unequalized Eye

Channel Loss @ 19 GHz: 14.3 dB (one-half bit-rate) Channel Type: 6-ft SMA & 3-ft 50-GHz cable

# Eye Diagrams – 38 Gb/s

**Unequalized Channel Eye**

Equalized Eye

$$V_{DD} = 1.2 V$$

$V_{CTRL1} = 0.82 V$

$V_{CTRL2} = 0.88 V$

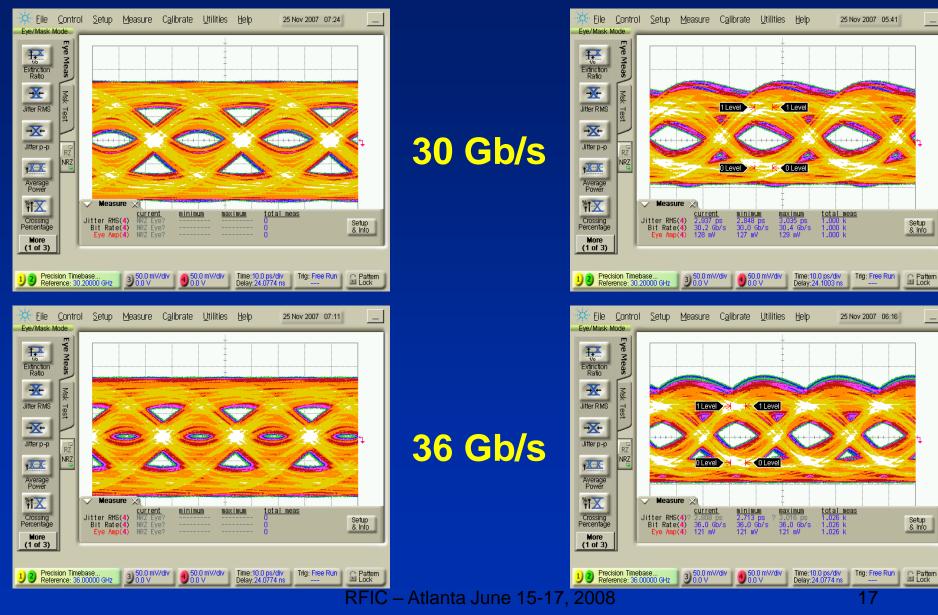

### Eye Diagrams 30 & 36 Gb/s

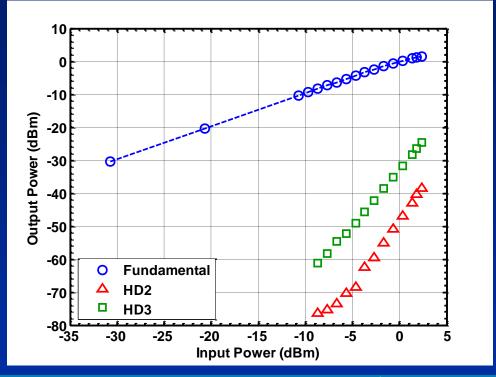

# Linearity

| Mode                            | No peaking |

|---------------------------------|------------|

| Input Tone (GHz)                | 2          |

| Input Ref. 1 dB Comp. Pt. (dBm) | 1.8        |

| THD @ Comp. Pt. (dB)            | -27.5      |

# **Measurement Summary**

| Specification                                                   | Measured Result                                                            |

|-----------------------------------------------------------------|----------------------------------------------------------------------------|

| Process                                                         | UMC 0.13-µm CMOS                                                           |

| Nominal Operating Supply (V)                                    | 1.2                                                                        |

| Nominal I <sub>DD</sub> (mA)<br>Nominal I <sub>CTRL2</sub> (mA) | 12 (no peaking),<br>17 (max peaking)<br>0 (no peaking),<br>8 (max peaking) |

| Maximum Power Consumption (mW)                                  | 30 mW<br>14 mW (tap 1)<br>16 mW (tap 2)                                    |

| S <sub>11</sub> (peaking off) (dB)                              | > -9.2 dB up to 26.5 GHz                                                   |

| S <sub>22</sub> (peaking off) (dB)                              | > -10 dB up to 26.5 GHz                                                    |

| Maximum equalized channel attenuation (dB)                      | 14.3                                                                       |

| Maximum equalized bit-rate (Gb/s)                               | 38                                                                         |

| Input ref. 1-dB compression point (no peaking) (dBm)            | 1.8                                                                        |

# Conclusion

- Presented a 2-tap transversal FIR equalizer

- Utilizes "U" shaped microstrip transmission line to achieve baud-tap spacing

- Series "line inductors" maintain constant input and output impedance up to 30 GHz

- Demonstrated equalization of 38-Gb/s data stream with 14.3 dB of channel attenuation

## **Acknowledgments**

- Gennum Corporation for IC fabrication

- Broadcom Corporation for financial support