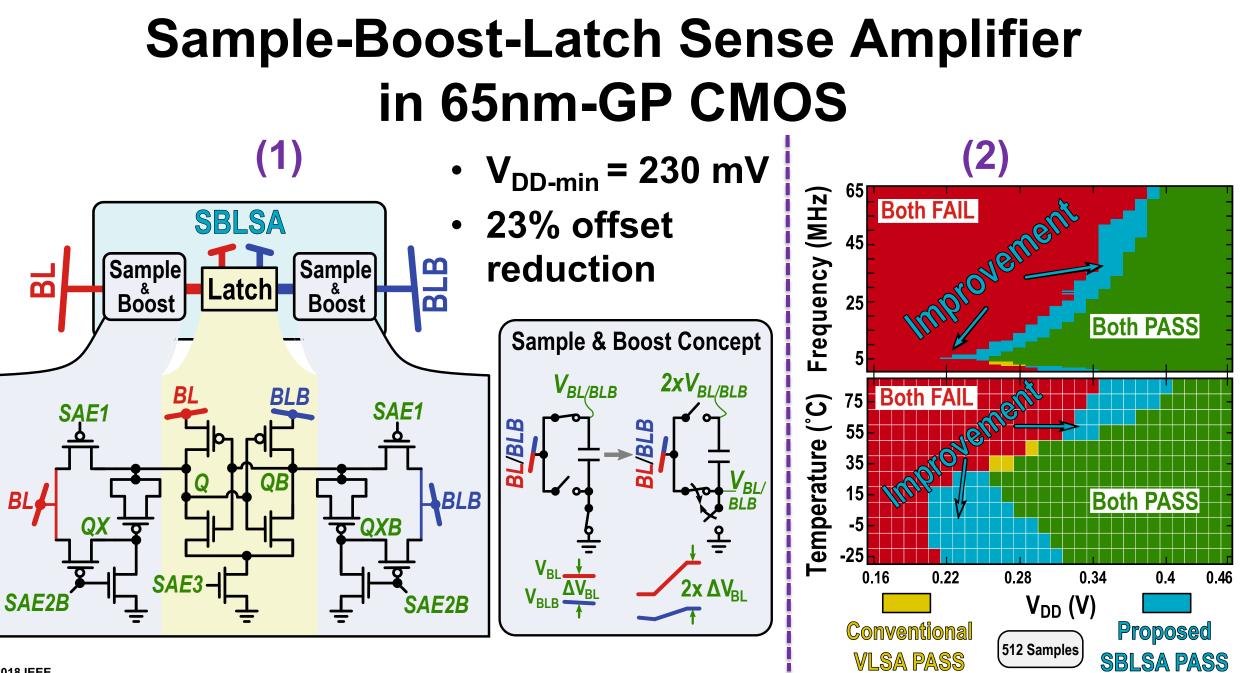

## Sample-Boost-Latch Based Offset Tolerant Sense Amplifier for Subthreshold SRAMs

Dhruv Patel<sup>1,2</sup> and Manoj Sachdev<sup>2</sup> <sup>1</sup>Dept. of ECE, University of Toronto, Canada <sup>2</sup>Dept. of ECE, University of Waterloo, Canada

- Low-voltage, high-speed & reliable SRAMs are in high demand for SoCs

- Sense Amplifier offset play a vital role in dictating SRAM performance

- For example, for every 1 mV of Sense Amplifier offset requires ~10 mV of highly capacitive bitline discharge for  $6\sigma$  SRAM yield [Abu-Rahma CICC 2011]

**Motivation:**

© 2018 IEEE International Solid-State Circuits Conference

Student Research Preview