# Hybrid Latch-Type Offset Tolerant Sense Amplifier for Low-Voltage SRAMs

Dhruv Patel, Student Member, IEEE, Adam Neale, Member, IEEE, Derek Wright, Member, IEEE, and Manoj Sachdev, Fellow Member, IEEE

Abstract-Sense Amplifier (SA) input-referred offset often dictates the minimum required differential input ( $\Delta V_{BL-min}$ ) and is an important factor in realizing low-voltage SRAMs. This work presents a HYbrid Latch-Type Sense Amplifier (HYSA-QZ), where the bitline signals are supplied to multiple internal nodes to significantly reduce  $\Delta V_{BL-min}$ . A 65nm CMOS test chip with arrays of HYSA-QZ, two intermediate formulations of HYSA-QZ, conventional Current Latch SA (CLSA) and conventional Voltage Latch SA (VLSA) were fabricated. Measurements over 5120 SAs of each type show that the HYSA-QZ implemented with regular-V<sub>T</sub> transistors require 50.0%, and 22.8% lower  $\Delta V_{BL-min}$ with 6.5% (or 4.5%) and 30.7% (or 18.8%) of total gate (or layout) area overhead compared to CLSA and VLSA at 0.4 V, respectively. Iso-gate-area offset improvement was substantiated with Pelgrom's mismatch model where HYSA-QZ with regular-V<sub>T</sub> transistors showed 46.6% and 7.7% improvements in measured standard deviation of offset distribution compared to CLSA and VLSA, respectively. Measured  $\Delta V_{BL-min}$  for HYSA-QZ remains stable and low over a temperature range from 0 °C to 75 °C at 0.4 V. Moreover, an additional 13.0% reduction in  $\Delta V_{BL-min}$  was measured in HYSA-QZ when using Low-V<sub>T</sub> transistors. Finally, HYSA-QZ operates reliably at V<sub>DD-min</sub> of 260 mV in 25 °C.

Index Terms—Comparator, Offset Tolerant Latch, Offset Cancellation, Sense Amplifier, Variation Tolerant Circuits, SRAM

### I. INTRODUCTION

Static Random Access Memories (SRAMs) often occupy a significantly large area of System on Chips (SOCs) and consequently affect their energy consumption, yield, and reliability. A sense amplifier (SA) is an important circuit that reads and amplifies the data stored in an SRAM cell. The characteristics of an SA determine several important SRAM metrics, including minimum operating voltage, maximum read frequency, and power/energy consumption [1]. Among all these related characteristics, the SA sensing delay, minimum required differential input voltage,  $\Delta V_{BL-min}$  (resolution), and energy of the read/write operations are the most important [2].

#### II. BACKGROUND

Two popular SA topologies are the Voltage Latch SA (VLSA) and the Current Latch SA (CLSA). The choice of specific topology is dependent on the technology used [3]. To make a reliable decision, an SA requires a minimum worst-case differential signal ( $\Delta V_{BL-min}$ ), which should be greater than the SA's input-referred offset voltage (Vos) [4]. The SA's Vos is determined by the V<sub>T</sub> mismatches of the sensing and input

transistors [5]. Abu Rahma et al. reported that larger standard deviation of input referred offset distribution ( $\sigma_{OS}$ ) has a significant negative impact on SRAM speed and read access yield, Y<sub>read</sub> [6]. Analysis carried out by the authors shows that for a 28 nm, 16 Mb SRAM with Yread of 97%, every 1 mV increase in  $\sigma_{OS}$  of the SA requires a 10 mV increase in the  $\Delta V_{BL-min}$  [6]. Minimizing  $\Delta V_{BL-min}$  improves energy consumption as it takes less time to develop a smaller differential voltage on the highly capacitive bitlines, which experience less discharge per read access. The SA's Vos arises from the mismatches in the gain factor, the drain current, the threshold voltage V<sub>T</sub>, and the layout of the devices used [7, 8]. Among these, VT mismatch has been identified as the dominant contributing factor to Vos. Shah [9] concluded that the VT mismatch between the NMOS sensing pair mostly determines the CLSA's Vos. Similarly, the work on VLSA [10] reported that the majority of  $V_{OS}$  is contributed by the  $V_T$  mismatch in NMOS pair when bitlines are precharged to V<sub>DD</sub>. Unfortunately, aggressive device scaling has resulted in increased device variations and contributed to larger Vos in SAs [11, 12].

The main target for this work is to investigate into offset tolerant low-voltage SA topologies that can leverage low-voltage SRAMs to enable wide range of battery-operated mobile, sensory and implantable SOCs with stringent energy constraints. In this paper, we propose a differential SA architecture that reduces the required  $\Delta V_{BL-min}$  while offering reliable operation from the nominal supply down to the subthreshold supply range. The proposed SA combines both CLSA and VLSA features by applying the differential input signal to multiple sensing nodes, and thus referred to it as the HYbrid SA (HYSA). This also makes our proposed differential HYSA compatible with most of the symmetrical fully differential SRAM cells i.e. 6T, 8T, 10T etc.

The rest of this paper is outlined as follows. Section III introduces the proposed SA, HYSA-QZ as a succession from the conventional topologies with their description, and simplified circuit analysis and proving the improvement in offset tolerance. Section IV shows the simulations on transient waveforms, and offset tolerance supporting the hypothesis from the prior section. It also analyzes each SA's sensing delay and dynamic power consumption. Section V contains measured offset statistics and shmoo plots. Section VI compares proposed HYSA-QZ with other SAs considered in this work as well as previously published works. Finally, Section VII concludes the work with summarized results.

Manuscript submitted on May 7, 2018. This work was supported in part by NSERC under grant NSERC-RGPIN-205034-2012 052714.

Dhruv Patel was with the University of Waterloo and is now with the Electrical and Computer Engineering Department, University of Toronto, Toronto, ON M5S 3G4 (e-mail: dhruv.patel@isl.utoronto.ca).

Adam Neale was with the University of Waterloo and is now with Intel, Hillsboro, OR 97124, USA (e-mail: ajneale@uwaterloo.ca).

Derek Wright, and Manoj Sachdev are with the Electrical and Computer Engineering Department, University of Waterloo, Waterloo, ON N2L 3G1. (e-mails: derek.wright@uwaterloo.ca, msachdev@uwaterloo.ca).

This is a final version of the accepted manuscript. Published version can be found at http://doi.org/10.1109/TCSI.2019.2899314

# III. HYBRID SRAM SENSE AMPLIFIER

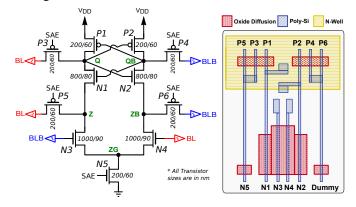

Abu Rahma et al. reported that the CLSA exhibits ~3x wider  $\sigma_{os}$  compared to a VLSA of the same total gate area [6]. However, the CLSA having access to multiple internal nodes over a regenerative signal path allowed us to apply the bitline signals to those internal nodes to preset the regenerative mechanism's converging direction with higher gain factor against mismatches. As a result, the HYSA-QZ was developed where its schematic and layout are shown in Fig. 1. Similar to the operation of VLSA and CLSA, the operation of the proposed HYSA-QZ can be divided into two phases: (I) Precharge with BL/BLB (II) Enable Latch, Regenerate and Resolve. In phase (I), SAE is kept LOW which turns ON all the P3-P6 access PMOS switches allowing differential BL/BLB to precharge Z/ZB and Q/QB nodes with small voltage difference. In phase (II), SAE is asserted HIGH which turns off all the P3-P6 PMOS access switches and turns on N5. This allows differential current driving transistors, N3/N4 driven by BL/BLB to further amplify the voltage difference in Z/ZB and Q/QB nodes. This ultimately helps start the regeneration process in the latching element formed by the P1/P2 and N1/N2 transistors. Finally, the latching element resolves one of Q/QB nodes to VDD and another to GND. The resulting output on Q/QB nodes is later buffered through an inverter as OUTB/OUT.

Fig. 1. Proposed offset tolerant HYbrid Latch-type Sense Amplifier (HYSA-QZ) schematic and layout.

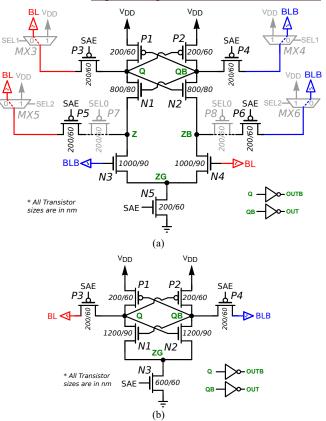

Fig. 2 (a) illustrates the proposed HYSA-QZ and its associated mode selection transistors. The mode selection multiplexors and transistors are for investigating and understanding the effectiveness of applying the differential signal to multiple SA locations to mitigate the V<sub>T</sub> mismatch between otherwise matched transistor pairs. These are shown in gray to distinguish them from the HYSA-QZ transistors. In the most preferred configuration, **HYSA-QZ**, the differential bitline signals are applied to all three following pairs of nodes: (i) Q and QB nodes; (ii) Z and ZB nodes; and (iii) the gates of transistors N3 and N4. Transistors P1, N1, P2, and N2 make a latching element in the HYSA-QZ and, together with P3 and P4, behave like a VLSA as shown in Fig. 2 (b). Transistors N3 and N4 with their gates connected to BLB and BL, respectively, mimic a CLSA.

Table I shows seven different topologies with their respective modes implemented on the test chip along with their relative total gate area (calculated sum of width x length of transistors) and physical layout area (both excludes the area of selection multiplexors/transistors). The first letter in the first column signifies Regular or Low  $V_T$  (R- $V_T$  or L- $V_T$ ) transistors

Fig. 2. SAs fabricated in 65nm test Chip – (a) Hybrid and Current Latch-Type SRAM SAs with configurable test modes (b) Conventional VLSA.

in the SA. Subsequent letters signify the types of SA, e.g., HYSA, CLSA or VLSA. The last set of letters signify the applied differential input signal (BL/BLB) locations. For example, L-HYSA-QZ signifies it to be an  $L-V_T$  HYSA with BL/BLB signals applied to Q/QB and Z/ZB nodes. As apparent from Fig. 2 (a), an HYSA with appropriate SEL signals can be reduced to a CLSA. In all CLSA and HYSA configurations, the BL/BLB are always applied to the gates of N3/N4 transistors. In literature, the SA proposed in the work of [13] is similar to the L-CLSA-Z which additionally applies BL/BLB signals to Z/ZB nodes. On the other hand, the proposed SAs in the works of [14], [15] and [16] are similar to the L-HYSA-Q which additionally applies BL/BLB signals to Q/QB nodes, but not to Z/ZB nodes. In our proposed R/L-HYSA-QZ, we apply BL/BLB signals to both Q/QB and Z/ZB nodes simultaneously to further improve the offset tolerance and in fact, the best

TABLE I. TEST MODES DESCRIPTION

| Mode      | Mode description                                              | SEL<br>[2:0] | Rel.<br>Total<br>Gate<br>Area | Rel.<br>Total<br>Layout<br>Area |  |

|-----------|---------------------------------------------------------------|--------------|-------------------------------|---------------------------------|--|

| R-VLSA    | R-V <sub>T</sub> VLSA (Conventional)                          | -            | 1                             | 1                               |  |

| R-CLSA    | R-V <sub>T</sub> CLSA (Conventional)                          | 111          | 1.23                          | 1.14                            |  |

| L-CLSA    | L-V <sub>T</sub> CLSA (Conventional)                          | 111          | 1.23                          | 1.14                            |  |

| L-CLSA-Z  | L-V <sub>T</sub> CLSA with BL/BLB to<br>Z/ZB (Intermediate-I) | 010          | 1.31                          | 1.19                            |  |

| L-HYSA-Q  | $L-V_T$ HYSA with BL/BLB to<br>Q/QB (Intermediate-II)         | 101          | 1.23                          | 1.14                            |  |

| R-HYSA-QZ | R-V <sub>T</sub> HYSA BL/BLB to Q/QB<br>and Z/ZB (Proposed)   | 000          | 1.31                          | 1.19                            |  |

| L-HYSA-QZ | $L-V_T$ HYSA BL/BLB to Q/QB and Z/ZB (Proposed)               | 000          | 1.31                          | 1.19                            |  |

possible offset tolerance among all analyzed topologies in this work. The significance and the effect of applying BL/BLB signals to both Q/QB and Z/ZB nodes will be shown throughout this paper by the means of offset tolerance analysis, simulations and detailed on-chip measurements.

The rest of this section provides a substantiation with simplified circuit analysis showing HYSA-QZ having higher offset tolerance compared to other topologies. The circuit analysis shown in Fig. 3 evaluates differential overdrive voltages ( $\Delta V_{OV}$ ) and differential drain-to-source voltages ( $\Delta V_{DS}$ ) on the NMOS transistor pairs, N1/N2 and N3/N4 at the instant when the SAE signal makes a 0 $\rightarrow$ 1 transition.  $\Delta V_{OV}$  and  $\Delta V_{DS}$  of NMOS transistor pairs are analyzed as they are the key parameters for creating differential transconductance ( $\Delta g_m$ ) and differential impedance ( $\Delta \Omega$ ), respectively giving rise to differential current ( $\Delta I$ ) in the left and right branches of a given latch-type SA. The polarity of  $\Delta I$  set by the applied  $\Delta V_{BL}$  and other preset conditions is of importance in making a correct decision at the moment when the SAE is asserted. Hence,  $\Delta V_{OV}$  and  $\Delta V_{DS}$  are analyzed at this instant.

Assumptions and definitions used in this analysis in Fig. 3 are shown in the first row. To impose worst-case disadvantageous mismatch conditions,  $V_T$  mismatches ( $\Delta V_T$ ) are assumed such that  $V_{T2} > V_{T1}$  and  $V_{T4} > V_{T3}$  inducing  $\Delta I$  in undesirable opposite polarities. Given these mismatch assumptions and applied  $\Delta V_{BL}$  according to the topology configurations (see third and fourth rows),  $\Delta V_{OV:2-1}/\Delta V_{OV:4-3}$  and  $\Delta V_{DS:2-1}/\Delta V_{DS:4-3}$  are calculated as shown in fifth and sixth rows, respectively. Based on the applied BL/BLB in all topologies, the expected value through the left branches (Q) is '1' (V<sub>DD</sub>) and through the right branches (QB) is '0' (GND). Hence, favorably, left branches should exhibit higher impedance to GND trying to hold to V<sub>DD</sub> and should drain less current compared to right branches. On the other hand, right branches should exhibit lower impedance to GND trying to drain QB to GND and should drain more current compared to left branches. Therefore, the preset or pre-charge conditions where the transistors in the right branches have higher V<sub>OV</sub> (indicating higher current draining capability) and lower VDs (indicating lower impedance to GND) compared to the transistors in the left branches is desirable. This dictates that higher magnitudes of  $\Delta V_{OV:2-1}/\Delta V_{OV:4-3}$  with +ve

polarity and higher magnitudes of  $\Delta V_{DS:2-1}/\Delta V_{DS:4-3}$  with -ve polarity is desired resulting in higher  $\Delta I$  with desirable polarity working against mismatches; this ultimately dictates topology's ability to tolerate disadvantageous mismatch conditions.

Calculated  $\Delta V_{OV}$  and  $\Delta V_{DS}$  in Fig. 3 are put into three categories: (1) working with mismatch (Bad), (2) working against mismatch to neutralize the mismatch effect (Neutral) and (3) Compensating mismatch to 0 and/or giving additional offset tolerance (Good). VLSA: The required  $\Delta V_{BL-min}$  must be at least equal to  $\Delta V_{T:2-1}$  to neutralize the mismatch effect with some aid from  $\Delta V_{DS:2-1}$  pre-setting  $\Delta \Omega_{2-1}$  in favor of the desired decision. CLSA: It has  $\Delta V_{OV:2-1}$  compensated to 0 where the mismatch due to  $\Delta V_{T;2-1}$  works in favor of presetting  $\Delta \Omega_{4-3}$  but works against presetting  $\Delta\Omega_{2-1}$ . Coincidental advantages due to  $\Delta V_{T:2-1}$  are bound to randomness and therefore not assured. CLSA will typically require  $\Delta V_{BL-min}$  of at least  $\Delta V_{T:4-3}$  for making a correct decision, requiring it to neutralize  $\Delta V_{OV:4-3}$ . **CLSA-Z:** It has applied  $\Delta V_{BL}$  working in favor of presetting  $\Delta\Omega_{4-3}$  giving assured aid in desirable initial amplification phase, but works against presetting  $\Delta \Omega_{2-1}$  which is relatively less of a concern after the sufficient signal amplification on Z/ZB is achieved [17]. It will require  $\Delta V_{BL-min}$  of around  $\Delta V_{T:4-3}$  to neutralize  $\Delta V_{OV:4-3}$  or little larger to overcome worst-case  $\Delta V_{T:2-1}$  mismatch. **HYSA-O:** It has coincidental aid from  $\Delta V_{T:2-1}$  to pre-set  $\Delta \Omega_{4-3}$  in the desired polarity but is diminished by the intentionally applied  $\Delta V_{BL}$ . However, it has its  $\Delta V_{OV:2-1}$ compensated to 0 and has 2x impact of  $\Delta V_{BL}$  to fight against  $\Delta V_{T:2-1}$  mismatch to neutralize  $\Delta V_{DS-2:1}$ ; which consequently reduces  $\Delta V_{BL-min}$  requirement to neutralize  $\Delta V_{OV:4-3}$ . **HYSA-QZ:** This proposed topology has assured  $\Delta V_{BL}$ presetting  $\Delta\Omega_{4-3}$  in the desired polarity during initial amplification phase and has  $\Delta V_{DS:2-1}$  compensated to 0. Moreover, its  $\Delta V_{OV:2-1}$  is benefitted by 2x effect of  $\Delta V_{BL}$  to fight against  $\Delta V_{T:2-1}$  mismatch; this further helps in reducing the  $\Delta V_{BL-min}$  requirement to fight  $\Delta V_{T:4-3}$  to neutralize  $\Delta V_{OV:4-3}$ . All these benefitting attributes indicate HYSA-QZ has higher offset tolerance than topologies discussed before. Overall, applying BL/BLB to more internal nodes bring consistency in preset conditions and relaxes  $\Delta V_{BL-min}$  for neutralizing mismatches or disadvantageous preset conditions. The simulations supporting this hypothesis is shown in the next section followed by supporting measurement results in Section V.

| Circuit Analysis<br>Assumptions &<br>Definitions:                                                                                                                                                                                                                                                                                                                                                                                          |                                | $D - \sqrt{V_{DD}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\Delta V_{T:2-1} = V_{T2} - \Delta V_{T:4-3} = V_{T4} - \Delta V_{T:4-3} = V_{T4} - \Delta V_{T}$ |                                                                                                                                         | $V_{OV} = V_{GS} - V_T$<br>$\Delta V_{OV:2-1} = V_{OV2} - V_{OV}$<br>$\Delta V_{OV:4-3} = V_{OV4} - V_{OV}$ |                                                        | - V <sub>DS1</sub>                     | rst Case random local<br>nismatch condition $\rightarrow$ $V_{T2} > V$<br>on applied BL/BLB signals $V_{T4} > V$                                                                                    |                                            |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|

| VLSA                                                                                                                                                                                                                                                                                                                                                                                                                                       | VLSA CLSA                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LSA                                                                                                |                                                                                                                                         | CLSA-Z HYSA-Q                                                                                               |                                                        |                                        | HYSA-QZ                                                                                                                                                                                             |                                            |  |

| Q/QB: Pre-charged                                                                                                                                                                                                                                                                                                                                                                                                                          | to BL/BLB                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | charged to V <sub>DD</sub><br>: Floated                                                            |                                                                                                                                         | <b>QB:</b> Pre-charged to V <sub>DD</sub><br>: Pre-charged to BL/BLB                                        | Q/QB: Pre-cha<br>Z/ZB: F                               | arged to BL/BLB<br>loated              | /BLB Q/QB: Pre-charged to BL/E<br>Z/ZB: Pre-charged to BL/E                                                                                                                                         |                                            |  |

| V <sub>DD</sub> QB V <sub>DD</sub> -∆V <sub>BL</sub><br>*Convtnl. NI N2<br>ZG                                                                                                                                                                                                                                                                                                                                                              |                                | V <sub>DD</sub><br>Convtnl. N1<br>V <sub>DD</sub> <sup>-</sup> Q QB<br>V <sub>DD</sub><br>V <sub>DD</sub> |                                                                                                    | $\begin{array}{c c} V_{DD} & QB & V_{DD} \\ \hline \\ $ |                                                                                                             | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |                                        | V <sub>DD</sub> Q   QB   V <sub>DD</sub> ΔV <sub>BL</sub> *Proposed   N1   N2   N2   N2     V <sub>DD</sub> Z   ZB   V <sub>DD</sub> ΔV <sub>BL</sub> V <sub>DD</sub> ΔV <sub>BL</sub> N3   ZG   N4 |                                            |  |

| $\textcircled{2} \Delta V_{OV:2-1} = \Delta V_{B}$                                                                                                                                                                                                                                                                                                                                                                                         | _ <b>- ΔV</b> <sub>T:2-1</sub> | $\sim$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                    |                                                                                                                                         |                                                                                                             |                                                        |                                        | $\bigotimes \Delta V_{OV:2-1} = \Delta V_{BL} + \Delta V_{BL} - \Delta V_{T:2-1}$                                                                                                                   |                                            |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $= \Delta V_{BL} - \Delta V_{T:4-3}$                                                               | <u> </u>                                                                                                                                | $\Delta V_{OV:4-3} = \Delta V_{BL} - \Delta V_{T:4-3}$                                                      | -                                                      | ΔV <sub>BL</sub> - ΔV <sub>T:4-3</sub> |                                                                                                                                                                                                     | $\Delta V_{\rm BL} - \Delta V_{\rm T:4-3}$ |  |

| Ο   ΔV   Δ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ   Ξ | -ΔV <sub>BL</sub>              | $\bigotimes \Delta V_{DS:2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <sub>-1</sub> <b>= +∆V</b> <sub>T:2-1</sub>                                                        | $\odot$                                                                                                                                 | $\Delta V_{DS:2-1} = + \Delta V_{BL}$                                                                       | $\textcircled{O} \Delta V_{DS:2-1} = -\Delta V_{I}$    | $\Delta V_{BL} + \Delta V_{T:2-1}$     | ΔV <sub>DS</sub>                                                                                                                                                                                    | <sub>5:2-1</sub> = 0                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <sub>−3</sub> = −ΔV <sub>T:2−1</sub>                                                               | $\odot$                                                                                                                                 | $\Delta V_{\text{DS}:4-3} = -\Delta V_{\text{BL}}$                                                          | <u>ΔV<sub>DS:4-3</sub> = -</u>                         | ΔV <sub>T:2−1</sub> + ΔV <sub>BL</sub> | Ο   ΔV     ΔV   DS:4-5                                                                                                                                                                              | <sub>3</sub> = −ΔV <sub>BL</sub>           |  |

| Bad: Working With mismatch Working against mismatch to neutralize the mismatch effect Good: Compensating mismatch to 0 and/or beyond giving additional offset tolerance                                                                                                                                                                                                                                                                    |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |                                                                                                                                         |                                                                                                             |                                                        |                                        |                                                                                                                                                                                                     |                                            |  |

Fig. 3. Simplified circuit analysis showing how applying bitlines to various internal nodes over each of the topologies studied in this work is effectively overcoming the V<sub>T</sub> mismatches. The analysis consists of comparing resulted differential over drive voltages ( $\Delta V_{OV}$ ) and differential drain-to-source voltages ( $\Delta V_{DS}$ ) for an applied  $\Delta V_{BL}$  on a given SA topology. The analysis was performed just at the moment when the SAE is asserted high (0  $\rightarrow$  1 transition).

From the previous analysis it was clear that all topologies do not have any mismatch compensation happening on N4/N3 pair ( $\Delta V_{0V:4:3}$  terms in Fig. 3). Hence, this led to spending more gate area budget on N4/N3 than on N2/N1 reducing the  $\Delta V_{T:4:3}$ mismatch. The sizing of the R-VLSA in Fig. 2 (b) was selected as a tradeoff between Vos, energy consumption, and the overall area. Furthermore, the PMOS access switches (P3-P6) in all topologies exhibit mismatch and coupling effect from the SAE signal on internal nodes. Since the common mode on bitlines is assumed to be close to V<sub>DD</sub>, PMOS transistors were selected for these access switches to avoid V<sub>T</sub> drop across them while precharging internal nodes. By giving sufficient time to pre-charge internal nodes, the impact of I<sub>d</sub> variations due to mismatch effect could be reduced. Moreover, these switches were sized near-

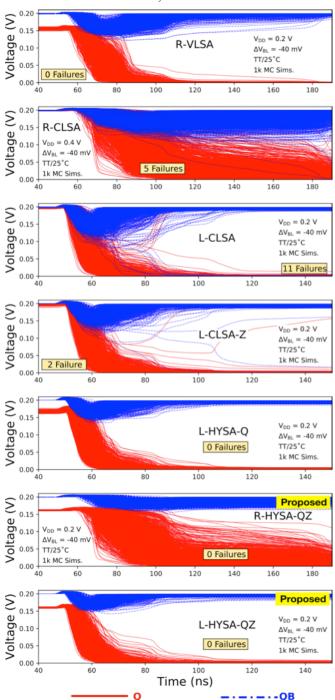

Fig. 4. Transient response (1k Monte Carlo simulations) of SAs analyzed in this work. Simulated with  $V_{DD} = 0.2$  V and  $\Delta V_{BL} = -40$ mV at 25° C.

minimum to avoid additional bitline loading and the coupling effect through the overlap capacitances of the access switches which are relatively small fraction of their gate capacitances ( $\sim 10\%$  of C<sub>gate</sub>).

#### IV. SIMULATION RESULTS

As this work is mainly targeted towards low-voltage operation, the comparison among each SA's output (Q/QB) transient response with  $V_{DD} = 0.2$  V and  $\Delta V_{BL} = -40$ mV at TT/25 °C corner is shown in Fig. 4. It shows 1k Monte Carlo (MC) simulations with the decision failures associated with each SA. SAs with Q/QB precharged with bitlines (R-VLSA, L-HYSA-Q, R/L-HYSA-QZ) were able to perform successfully at such low supply voltage without any failures. Also, similar results were achieved with  $\Delta V_{BL} = +40$ mV. Despite having four stacking transistors, L-HYSA-Q and proposed R/L-HYSA-QZ were capable of operating without any decision failures owing to their precharge conditions and high offset tolerance. Hence, they are suitable for low-voltage operations. The benefits of applying bitlines at multiple locations is further analyzed in detail later in this section.

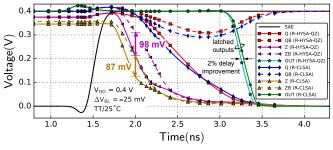

Fig. 5. Transient simulations comparison on pre-amplification of Z/ZB nodes on R-HYSA-QZ and R-CLSA just before the Q/QB peels away.

Fig. 5 shows the transient simulation comparison between **R-CLSA** R-HYSA-QZ and with  $V_{DD} = 0.4 V$ and  $\Delta V_{BL} = -25 \text{ mV}$  at TT/25°C corner. The purpose of this simulation is to compare the initial amplification of the differential signal in these two topologies before the regenerative phase starts (Q/QB peeling away). As analyzed in Fig. 3, pre-charging Q/QB and Z/ZB with bitline signals in R-HYSA-QZ help increase the effective  $\Delta V_{BL}$  applied to the SA. For example, Z/ZB in R-HYSA-QZ has 11 mV (98 mV-87 mV) more differential amplitude developed compared to R-CLSA showing the increased effectiveness of  $\Delta V_{BL}$  and ultimately increasing offset tolerance [17] [18]. Notice that Z/ZB in R-HYSA-QZ starts discharging from a relatively higher voltage compared to Z/ZB in R-CLSA. Despite that, R-HYSA-QZ could resolve in 2% less time owing to higher preamplification as a result of applied bitlines at Q/QB and Z/ZB nodes.

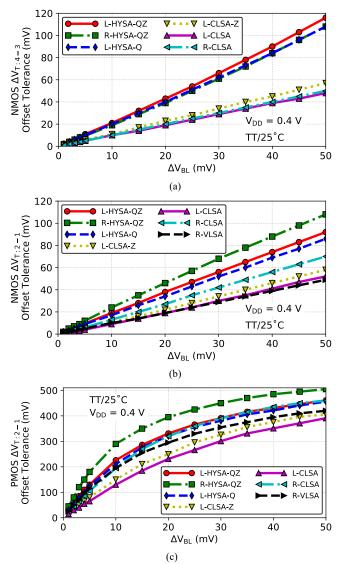

An SA with offset mitigation features should be able to tolerate offset and still make the correct decision. Simulated offset tolerance for each transistor pair in different topologies is shown in Fig. 6. It signifies how much V<sub>T</sub> offset in a given transistor pair can a given SA tolerate while still making a correct decision with applied value of  $\Delta V_{BL}$ . The analysis was performed across different values of  $\Delta V_{BL}$  with  $V_{DD} = 0.4$  V at TT/25°C corner. V<sub>T:1,2,3,4</sub> values were modified from their nominal values (i.e.  $V_{T:2} = V_{T-nom} + \Delta V_{T:2-1}/2$ ,  $V_{T:1} = V_{T-nom} - \Delta V_{T:2-1}/2$ ) in the transistor model files to emulate  $\Delta V_{T:4-3}$  and  $\Delta V_{T:2-1}$  in undesirable direction. Fig. 6 (a) and (b) shows the

offset tolerance for NMOS pairs N4/N3 and N2/N1 one at a time, respectively. For example, R-HYSA-QZ with applied  $\Delta V_{BL}$  of 20 mV is capable of tolerating 44 mV of  $\Delta V_{T:2-1}$  offset (considering other transistor pairs in perfect matching conditions, i.e  $\Delta V_{T:4-3} = 0$ ) and still make the correct decision. This can be explained by inspecting the simplified offset tolerance analysis from Fig. 3 in a following manner. Let us substitute the known values such as  $\Delta V_{BL} = 20$  mV and  $\Delta V_{T:4-3} = 0$  into the column associated with R-HYSA-QZ in Fig. 3. Now, this results in  $\Delta V_{OV:2-1} = +40 \text{ mV} - \Delta V_{T:2-1}$ , meaning  $\Delta V_{T:2-1}$  has to be greater than 40 mV to flip  $\Delta V_{OV:2-1}$  into -ve (undesirable) polarity to make an incorrect decision. Not only that but with the resulting  $\Delta V_{OV:4-3}$  of +20 mV,  $\Delta V_{DS:2-1}$  of 0 mV and  $\Delta V_{DS:4-3}$  of -20 mV, with all terms either being with desired polarity or compensated to 0, provides additional pull to maintain latching inertia into correct direction. Hence requiring  $\Delta V_{T:2-1}$  of 44 mV to overcome effective desirable impact of precharging conditions. Overall, all SAs' offset tolerance associated with NMOS pairs show linear scaling with applied  $\Delta V_{BL}$ .

Fig. 6. Simulated offset tolerance comparison across  $\Delta V_{BL}$  with  $V_{DD} = 0.4 V$  and  $\Delta V_{BL} = 20 \text{ mV}$  at 25°C. (a) Offset tolerance due to  $V_T$  mismatches of N4/N3 ( $\Delta V_{T:4-3}$ ) only. (b) Offset tolerance due to N1/N2  $V_T$  mismatches ( $\Delta V_{T:2-1}$ ) only. (c) Offset tolerance due to P1/P2  $V_T$  mismatches ( $\Delta V_{T:2-1}$ ) only.

Furthermore, Fig. 6 (c) shows a similar analysis on the P1/P2 pair. All topologies can tolerate relatively much higher PMOS mismatches compared to NMOS mismatches. Thus, sizing PMOS pair to near-minimum size poses almost no harm to V<sub>OS</sub> and allowed us to spend most of the gate area budget on the NMOS transistors where the VT mismatch matters the most. In all three transistor pairs (N4/N3, N2/N1 and P1/P2) and within their respective VT flavors, offset tolerance is increased as more internal nodes are precharged with bitlines where R/L-HYSA-OZ have the highest offset tolerance compared to other SAs. From these offset tolerance simulations, the general trend of the offset tolerance of HYSA-QZ > HYSA-Q >  $CLSA-Z > VLSA \approx CLSA$ , which supports the circuit analysis performed in the previous section. Also, applying bitlines at O/OB is relatively more effective compared to applying bitlines at Z/ZB as the offset tolerance improvement from L-CLSA-Z to L-HYSA-Q is relatively much higher than the offset tolerance improvement from L-CLSA to L-CLSA-Z.

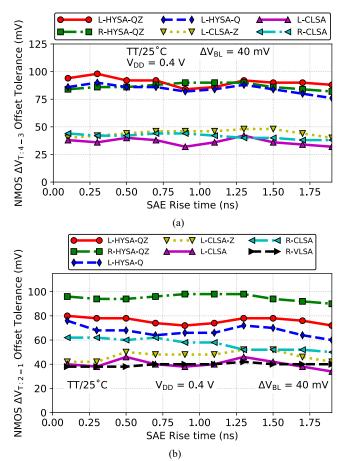

Fig. 7. Simulated Offset Tolerance comparison across SAE Rise time with  $V_{DD} = 0.4 \text{ V}$  and  $\Delta V_{BL} = 40 \text{ mV}$  at TT/25°C. Simulations were performed with transistor noise and  $V_{RMS-noise} = 5 \text{ mV}$  on all  $V_{DD}$ , bitlines and SAE signals. (a) Offset tolerance due to  $V_T$  mismatches of N4/N3 ( $\Delta V_{T:4-3}$ ) only. (b) Offset tolerance due to N1/N2  $V_T$  mismatches ( $\Delta V_{T:2-1}$ ) only.

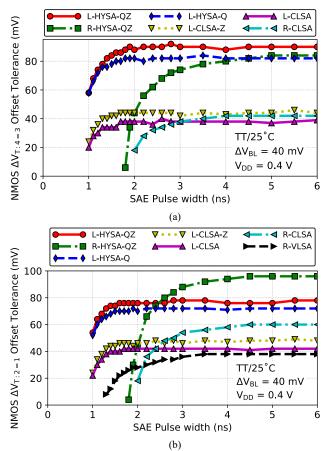

The SAE signal responsible for enabling footer transistor and disabling access switches leads to charge injection and coupling effects on to the critical internal nodes of the SA. Also, the SAE on/off timing determines the final considered output voltages developed on Q/QB nodes which are typically taken as an input by another latch following the SA. Hence, it is critical to analyze the sensitivity of the offset tolerance due to the dynamics of the SAE signal such as variations in SAE rise time (Fig. 7) and SAE pulse width (Fig. 8). These simulations were performed with  $V_{DD} = 0.4$  V and  $\Delta V_{BL} = 40$  mV at TT/25 °C corner. To add additional rigor, the transistor noise was enabled and  $V_{RMS-noise} = 5 \text{ mV}$  was added to all  $V_{DD}$ , bitlines and SAE signals during these simulations. Fig. 7 (a) and (b) shows the  $\Delta V_{T:4-3}$  and  $\Delta V_{T:2-1}$  offset tolerance across varied SAE rise time. Both plots have their offset tolerance relatively stable across SAE rise time and hence, sufficient to conclude that offset tolerance is insensitive to the SAE rise times within the range of 0.1 ns – 2 ns. Fig. 8 (a) and (b) shows the  $\Delta V_{T:4-3}$  and  $\Delta V_{T:2-1}$ offset tolerance across varied SAE pulse width. For all topologies, the offset tolerance starts off with lower value due to the pulse width not meeting the finite sensing delay associated with 40 mV of applied  $\Delta V_{BL}$ . After the pulse width exceeds the SA's sensing delay, the offset tolerance starts to stabilize and converge to the offset tolerance value found from Fig. 6 (a) and (b). SAs in L-V<sub>T</sub> flavor has much lower sensing delay and therefore requires relatively much less SAE pulse width before converging to their peak offset tolerance compared to SAs in R-V<sub>T</sub>. For example, L-HYSA-OZ requires pulse width of ~2 ns whereas R-HYSA-OZ requires ~4.5 ns to converge to their peak offset tolerance values. To highlight, in both analysis from Fig. 7 and Fig. 8, proposed R/L-HYSA-QZ is consistent in offering highest offset tolerance among other topologies.

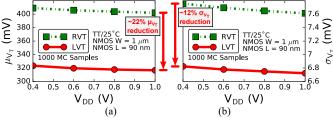

Possible offset improvement due to the use of transistors with different  $V_T$  flavors is also analyzed. Fig. 9 shows the  $V_T$  statistics of 1k MC simulations on an NMOS transistor ( $W_n =$

Fig. 8. Simulated Offset Tolerance comparison across SAE Pulse width with  $V_{DD} = 0.4 \text{ V}$  and  $\Delta V_{BL} = 40 \text{ mV}$  at TT/25°C. Simulations were performed with transistor noise and  $V_{RMS-noise} = 5 \text{ mV}$  on all  $V_{DD}$ , bitlines and SAE signals. (a) Offset tolerance due to  $V_T$  mismatches of N4/N3 ( $\Delta V_{T:4-3}$ ) only. (b) Offset tolerance due to N1/N2  $V_T$  mismatches ( $\Delta V_{T:2-1}$ ) only.

1 μm, L<sub>n</sub> = 90 nm) with L-V<sub>T</sub> and R-V<sub>T</sub> flavors under the saturation region at 25 °C in TT corner. Only an NMOS transistor with the size similar to the ones used in the implemented topologies was analyzed as the NMOS pairs have predominant impact on offset compared to PMOS pairs. Both  $\mu_{V_T}$  and  $\sigma_{V_T}$  are reduced from R-V<sub>T</sub> to L-V<sub>T</sub> by 22% and 12%, respectively. Lower  $\sigma_{V_T}$  is an indication of reduced mismatch effect and ultimately lower Vos for a given SA. Lower  $\mu_{V_T}$  is an indication for a lower sensing delay with the cost of increased total dynamic power consumption of a given SA (Pdy-SA).

Fig. 9. NMOS (1 $\mu$ m/90nm) V<sub>T</sub> statistics for 1k MC simulations at TT/25°C: (a) V<sub>T</sub> average ( $\mu_{V_T}$ ) (b) V<sub>T</sub> standard deviation ( $\sigma_{V_T}$ ).

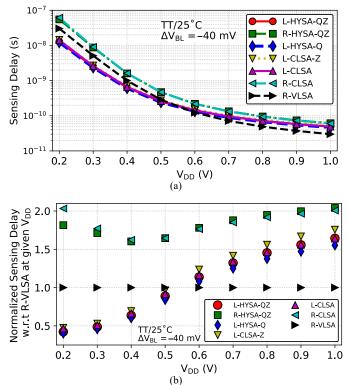

Fig. 10. (a) Simulated sensing delay across  $V_{DD}$ . (b) Normalized sensing delay w.r.t R-VLSA at a given  $V_{DD}$ . Performed at TT/25°C with  $\Delta V_{BL} = -40$  mV.

Fig. 10 (a) shows the simulated sensing delays across  $V_{DD}$  on a semi-log scale with perfect matching condition at 25 °C while keeping  $\Delta V_{BL} = -40$  mV. The sensing delays were extracted from SAE<sub>50%-rise</sub> to the OUT<sub>50%-fall</sub>, where the OUT is the SAs' buffered outputs with an inverter depicted in Fig. 2. Fig. 10 (b) shows the relative sensing delay with respect to R-VLSA's sensing delay at a given V<sub>DD</sub>. The sensing delay is reduced from R-V<sub>T</sub> to L-V<sub>T</sub>, with the difference increasing at lower V<sub>DD</sub>. The R-VLSA has lower sensing delay compared to R-CLSA and R-HYSA-QZ due to fewer transistor stacking and larger footer transistor (N3) width. The L-HYSAs and L-CLSAs

have lower sensing delay than R-VLSA up to 0.5 V owing to the combination of pre-charge conditions and lower V<sub>T</sub>. Nevertheless, sensing delay of an SA is just a small fraction of the entire read path delay. Importantly, lower SA V<sub>OS</sub> resulting in smaller  $\Delta V_{BL-min}$  development on highly capacitive bitlines would ultimately help reduce the overall read path delay.

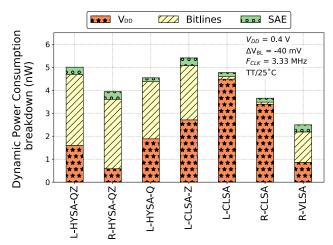

Fig. 11. Simulated  $P_{dy-SA}$  breakdown into  $V_{DD}$ , bitlines and SAE. (Simulated with  $V_{DD} = 0.4 \text{ V}$ ,  $\Delta V_{BL} = -40 \text{mV}$ , and  $F_{CLK} = 3.33 \text{ MHz}$  at TT/25°C corner).

The P<sub>dy-SA</sub> was simulated to realize the cost of precharging internal nodes. The Pdy-SA breakdown of each SA is shown in Fig. 11 where the simulations were performed with  $V_{DD} = 0.4 \text{ V}$ and  $F_{CLK} = 3.33$  MHz at TT/25 °C corner. The simulated  $P_{dy-SA}$ is divided into three key components: (1) Power drawn from the SAs' V<sub>DD</sub> source during regeneration phase and in the case of R/L-CLSA and L-CLSA-Z, precharging their Q/QB nodes. (2) Portion of the power drawn from the bitlines loading the gates of the current sensing transistors (not applicable for R-VLSA) and in the case of R/L-HYSA-QZ, L-HYSA-Q, L-CLSA-Z and R-VLSA, precharging their Q/QB and/or Z/ZB nodes. (3) Power drawn from the SAE driver loading the gates of the SA enable footer transistor and the PMOS access switches (P3-P6). From Fig. 11, it is apparent that R/L-CLSA draws relatively much less power from bitlines as they are only applied to the gates of the current sensing transistors (N4/N3). On the other hand, R/L-HYSA-QZ, L-HYSA-Q, L-CLSA-Z, and R-VLSA has significant portion of their Pdy-SA contributed by the bitlines as the internal nodes are being precharged by them. Also, the power contributed by the SAE signal is relatively low and as one would expect, it increases in proportion with the total gate area driven by the SAE signal (i.e. SAE power increases in topologies with higher number of access switches). The inverters used for buffering SA outputs had the same sizes for all topologies and hence, the power spent on loading those buffers (embedded in power contribution from V<sub>DD</sub> and bitlines) is equal in all topologies. Overall, R-VLSA consumes the lowest Pdy-SA as it has the lowest relative total gate area compared to other SAs. Also, note that despite having the same total gate area, L-CLSA-QZ has lower Pdy-SA than L-HYSA-Z as latter precharges both Q and QB nodes to VDD whereas former precharges only Q node to VDD but prechages QB node to  $V_{DD} - \Delta V_{BL}$ , which is lower than  $V_{DD}$ . The increased  $P_{dy-SA}$ cost for proposed R/L-HYSA-QZ compared to other SAs (excluding L-CLSA-Z) within same VT flavor mainly comes from supplying bitlines to multiple internal capacitances as well as driving more number of access switches.

(b) Fig. 12. (a) Simulated dynamic power (b) Normalized dynamic power w.r.t R-VLSA at a given V<sub>DD</sub>. Performed at  $\Delta V_{BL} = -40$ mV,  $F_{CLK} = 3.33$  MHz, TT/25°C.

The  $P_{dy-SA}$  comparison was further analyzed in Fig. 12 (a) showing the  $P_{dy-SA}$  simulated across  $V_{DD}$  with  $\Delta V_{BL} = -40 \text{ mV}$ and  $F_{CLK} = 3.33$  MHz at TT/25°C corner. Fig. 12 (b) shows the relative Pdy-SA where R-VLSA was set as a reference for each VDD. For R-HYSA-QZ and L-HYSA-QZ, the Pdy-SA cost relative to R-VLSA is increased from 63% to 94% and from 100% to 162% while reducing V<sub>DD</sub> from 1 V to 0.2 V, respectively. Despite the fact that the relative P<sub>dy-SA</sub> is higher for HYSA-QZs, with improved offset tolerance, they would lower highly capacitive bitline swing requirement reducing the overall SRAM power consumption and energy [19] [20]. Moreover, the Pdy-SA is a much smaller fraction of SRAM's overall read access dynamic power consumption (Pdy-read) as reported by the works of [21] and [22]. Using the measured  $\sigma_{OS}$  values of SAs, the net benefit in Pdy-read with the proposed R/L-HYSA-QZ topologies is justified in Section VI.

## V. MEASUREMENT RESULTS

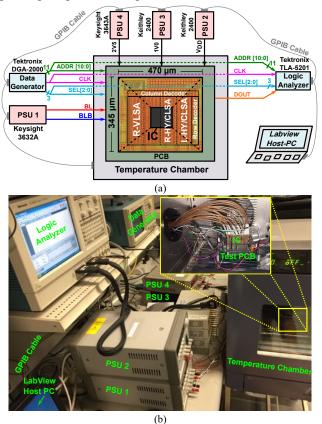

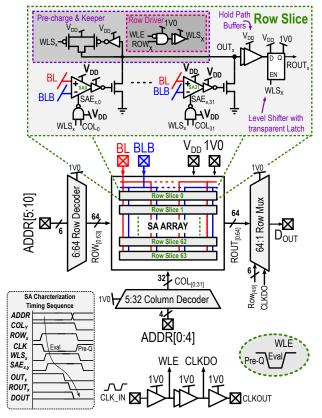

SA arrays of L-HYSAs/CLSAs, R-HYSAs/CLSAs and R-VLSA cells with different configurable modes were implemented in a 65nm-GP CMOS process shown in Fig. 13 with the test chip and the test bench setup. Similar to the works of [6, 10], each SA array was organized with 64 rows, and 8 columns containing total 512 cells that are individually addressable with a row and a column decoder. The test chip architecture for characterizing SA Vos is shown in Fig. 14. Each row slice contains SAs, pre-charge circuitry, pull-down NMOS transistors, and a level shifter with a latch. BL and BLB signals are routed vertically throughout the array. All the control signals for the mode selection transistors and the multiplexers were driven by 1.0 V supply to minimize the timing uncertainty of control signals. The measurements consist of two key aspects of characterization: (1) Directly measured VOS statistics across

#### This is a final version of the accepted manuscript. Published version can be found at http://doi.org/10.1109/TCSI.2019.2899314

$V_{DD}$  and temperatures. (2) Comparison of different topologies on reliability/reproducible results over clock frequency and the operating temperature at a given  $V_{DD}$ .

Fig. 13. (a) 65-nm Sense amplifier array test chip (b) test bench setup.

Fig. 14. Test chip implementation for SA offset characterization

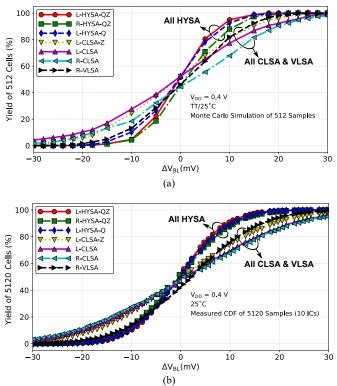

Fig. 15. (a) Simulated Cumulative Distribution of 512 SAs (b) Measured Cumulative Distribution of 5120 SAs across 10 ICs at 1 mV of  $\Delta V_{BL}$  step resolution.

Fig. 16. (a) Simulated Probability Density of  $V_{OS}$  across 512 SAs (b) Measured Probability Density of  $V_{OS}$  across 5120 SAs (10 ICs) at 1 mV of  $\Delta V_{BL}$  step resolution.

Fig. 15 (a) and (b) show simulated and measured Cumulative Distributions (CDF) of topologies analyzed in this work at 0.4 V at 25 °C, respectively. MC simulations and measured CDF plots across 10 ICs with a  $\Delta V_{BL}$  step resolution

This is a final version of the accepted manuscript. Published version can be found at <u>http://doi.org/10.1109/TCSI.2019.2899314</u>

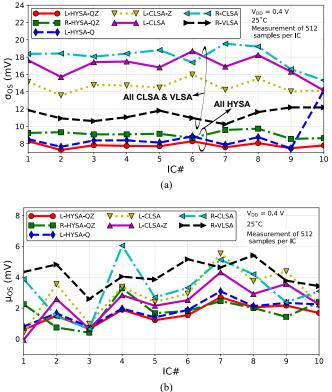

of 1 mV show that the  $\Delta V_{OS}$  distribution is tighter for proposed topologies compared to others with same VT flavor. Simulated and measured  $\sigma_{OS}$  values in Fig. 16 (a) and (b) were obtained by curve fitting (non-linear least-square minimization method) probability density function curves derived from their respective CDF curves illustrated in Fig. 15 (a) and (b), respectively. For example, 512 MC simulations in Fig. 16 (a) show that R-HYSA-QZ has  $\sigma_{OS}$  of 7.0 mV compared to R-CLSA of 11.7 mV, or R-VLSA of 9.6 mV. A similar trend is observed in Fig. 16 (b) over 5120 measured samples from 10 ICs with  $\sigma_{OS}$  of 9.1 mV, 18.1 mV and 11.4 mV for R-HYSA-QZ, R-CLSA and R-VLSA, respectively. The differences between measurements and simulations could be explained by the differences in the sample size, excluded layout parasitics and the inaccuracy of the mismatch model used in MC simulations. Fig. 17 (a) and (b) show the measured  $\sigma_{OS}$  and the mean of offset distribution  $(\mu_{OS})$  of each individual ICs with  $V_{DD} = 0.4 \text{ V}$  at 25 °C, respectively, distinguishing the impact of within-die and inter-die variations. It was evident that  $\sigma_{OS}$  of the proposed R/L-HYSA-QZ remained relatively low and stable (deviated less than  $|\pm 1 \text{ mV}|$ ) across each of the 10 ICs. The  $\mu_{OS}$ of each topologies remained within 0 mV - 6 mV across all 10 ICs.

Fig. 17. Statistics of measured within-die and inter-die offset distribution (a) Measured  $\sigma_{OS}$  across each of the 10 ICs. (b) Measured  $\mu_{OS}$  across each of the 10 ICs. (512 Samples per IC).

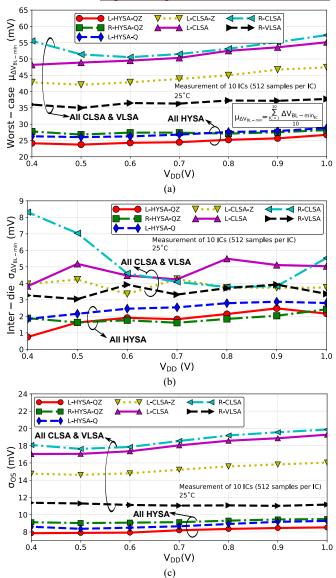

A similar measured statistical analysis was carried out over  $V_{DD}$  between 0.4 V to 1.0 V at 10 MHz. For each topology on each IC, worst case  $\Delta V_{BL}$  ( $\Delta V_{BL-min}$ ) required for 100% yield (0 failures in both logic '1' and '0' from 512 SAs) was extracted. Subsequently, the average of  $\Delta V_{BL-min}$  from 10 ICs,  $\mu_{\Delta V_{BL-min}}$  was computed for each  $V_{DD}$ . Fig. 18 (a) summarizes these measurements, and each data point in the figure represents this value. For example, for R-HYSA-QZ, the  $\mu_{\Delta V_{BL-min}}$  at

Fig. 18. (a) Measured avg. of V<sub>BL-min</sub> ( $\mu_{\Delta V_{BL-min}}$ ) across 10 ICs. (b) Measured Inter-die standard deviation of  $\Delta V_{BL-min}$  ( $\sigma_{\Delta V_{BL-min}}$ ) across 10 ICs. (c) Measured  $\sigma_{OS}$  across 5120 SAs (10 ICs).

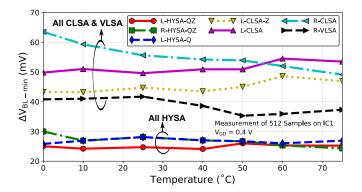

0.4 V is 27.8 mV as compared to 56.0 mV and 36.0 mV of R-CLSA and R-VLSA, respectively. Based on these measured results we conclude that R-HYSA-QZ requires 50.0% and 22.8%, smaller  $\Delta V_{BL-min}$  at the cost of 6.5% and 30.7% gate area overhead compared to R-CLSA and R-VLSA, respectively. Also, using L-V<sub>T</sub> transistors in L-HYSA-QZ lowered  $\mu_{\Delta V_{BL-min}}$  by 13.0% (56.5% w.r.t R-CLSA & 32.9% w.r.t. R-VLSA) compared to using R-VT transistors in R-HYSA-QZ. To validate the inter-die consistency of  $\Delta V_{BL-min}$ , standard deviation of  $\Delta V_{BL-min}$  ( $\sigma_{\Delta V_{BL-min}}$ ) across 10 ICs was computed and shown in Fig. 18 (b). Again, the proposed HYSA-QZs having relatively low  $\sigma_{\Delta V_{BL-min}}$  confirms inter-die consistency in offset tolerance. Also, as shown in Fig. 18 (c),  $\sigma_{OS}$  were extracted across V<sub>DD</sub> from their respective PDF curves to understand the improvement over gate area overhead explained in the next paragraph.  $\Delta V_{BL-min}$  characteristics of the SAs were also characterized across temperature between 0  $^{\circ}C - 75 ^{\circ}C$  at 0.4 V at 10 MHz. As depicted in Fig. 19, measured  $\Delta V_{BL-min}$

shows that all HYSA topologies have relatively more stable and lower  $\Delta V_{BL-min}$  across temperature compared to CLSA and VLSA. Overall, the measured relative trends were in good agreement with the circuit theory predictions, the offset tolerance and the MC simulations of V<sub>T</sub>. They showed that the HYSA topologies had increased offset tolerance as more internal nodes get precharged with bitlines and increased even further by using L-VT transistors. As was also predicted in Section IV, applying bitlines at Q/QB nodes is far more effective (~4.5x at 0.4 V) than applying bitlines at Z/ZB nodes. R-VLSA had relatively more gate area spent on its critical NMOS pair resulting in lower mismatch compared to other SAs. Therefore, despite having low offset tolerance as shown in Figs. 6-8, R-VLSA achieves lower  $\Delta V_{BL-min}$  and lower  $\sigma_{OS}$ compared to, for example, L-CLSA-Z, where it provides only comparable offset tolerance as R-VLSA.

Fig. 19. Measured  $\Delta V_{BL\text{-min}}$  stability across temperature range between 0  $^\circ\text{C}$  to 75  $^\circ\text{C}.$

Due to the gate area penalty in the proposed HYSA-QZ, we analyze measured  $\sigma_{OS}$  from Fig. 18 (c) while substantiating iso-gate area improvement. Pileggi et. al. [10] reported that

VLSA  $\sigma_{os}$  accurately follows Pelgrom's model [12] described by  $\sigma(\Delta V_{\rm T}) = \frac{A_{\rm T0}}{\sqrt{\rm WL}}$ , where  $A_{\rm T0}$ , W and L are the area proportionality constant, and width and length of two devices with close proximity, respectively. Considering this, adding 30.7% extra area to R-VLSA's NMOS pair would give maximum of  $\left(1-\frac{1}{\sqrt{1.307}}\right) \approx 12.5\%$   $\sigma_{OS}$  improvement in R-VLSA whereas R-HYSA-QZ improved measured  $\sigma_{OS}$  by 20.2%; therefore resulting in net iso-gate-area improvement of 7.7% at 0.4 V. However, at super-threshold supply, i.e. 1 V, this improvement reduces to 2.5%. With a similar analysis for R--CLSA, adding 6.5% extra area in R-CLSA's input NMOS sensing pair (best possible case) would give maximum improvement of  $\left(1 - \frac{1}{\sqrt{1.065}}\right) \approx 3.1\%$  which is far less than 49.7% measured  $\sigma_{os}$  improvement from R-HYSA-QZ at 0.4 V. Moreover, comparing the proposed L-HYSA-QZ with L-HYSA-Q, where the latter topology is similar to the one proposed by [14, 15], the former achieves 8.1%  $\sigma_{OS}$ improvement with 6.5% total gate area penalty. This still results in 5.0% iso-gate-area improvement in  $\sigma_{OS}$  at 0.4 V. At 1 V, improvement in measured  $\sigma_{os}$  slightly increases to 5.5%.

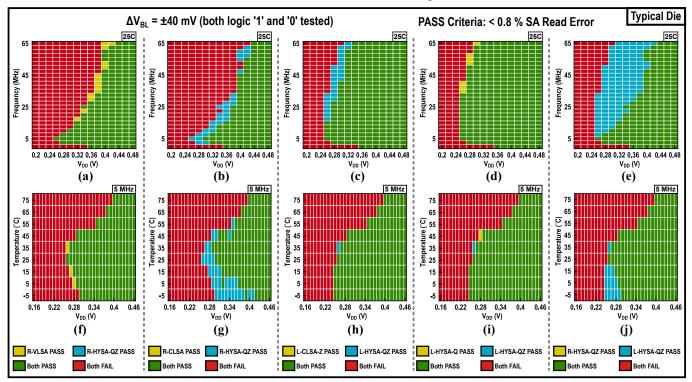

Fig. 20 (a)-(e) and Fig. 20 (f)-(j) shows the measured Temperature-V<sub>DD</sub> Frequency-V<sub>DD</sub> and shmoo plots. respectively. Conventional and intermediate topologies were compared with proposed HYSA-QZ within same VT flavor as shown in Fig. 20 (a-d, f-i). Also, improvement achieved by changing proposed HYSA-QZ's VT flavor from R-VT to L-VT is shown in Fig. 20 (e, j) shmoo plots. All shmoo plots were measured at  $\Delta V_{BL}$  of  $\pm 40 \text{ mV}$  ( $\pm$  for testing both logic '1' and '0') while changing the operating parameters, i.e. frequency, temperature and V<sub>DD</sub>. For a given operating condition, worst case yield (considering both '1' and '0' yields) for a typical die (512 samples) was obtained. The error rate less than 0.8% was considered a pass, and a fail otherwise.

Fig. 20. Measured Frequency vs V<sub>DD</sub> shmoo plots (a-e): (a) R-VLSA vs R-HYSA-QZ (b) R-CLSA vs R-HYSA-QZ (c) L-CLSA-Z vs L-HYSA-QZ (d) L-HYSA-Q vs L-HYSA-QZ (e) R-HYSA-QZ vs L-HYSA-QZ. Measured Temperature vs V<sub>DD</sub> shmoo plots (f-j): (f) R-VLSA vs R-HYSA-QZ (g) R-CLSA vs R-HYSA-QZ (h) L-CLSA-Z vs L-HYSA-QZ (i) L-HYSA-Q vs L-HYSA-QZ (j) R-HYSA-QZ vs L-HYSA-QZ.

Relative trends in Frequency-V<sub>DD</sub> shmoo plots reflect their relative sensing delays where a topology with lower sensing delay would be capable of operating at a relatively higher frequency under the same  $\Delta V_{BL}$  and other operating conditions. Since these measured shmoo plots include the impact of mismatch, they do not perfectly resemble relative sensing delay trends from Fig. 10 (b) which were simulated in perfect matching conditions. For example, R-VLSA is capable of operating at  $\sim 1.5x - 1.7x$  higher frequency than R-HYSA-OZ as seen in sensing delay analysis from Fig. 10 (b). However, from Fig. 20 (a), their relative difference is reduced due to higher offset tolerance in R-HYSA-QZ. In fact, below 0.32 V, R-HYSA-QZ offers identical performance as R-VLSA. Furthermore, Fig. 20 (b) shows R-HYSA-QZ performing better than conventional R-CLSA and Fig. 20 (c) shows L-HYSA-QZ further improving from intermediate topology, L-HYSA-Z; all owing to higher offset tolerance. Fig. 20 (d), however, illustrates L-HYSA-QZ operating slightly slower than L-HYSA-Q. This is because, at  $\Delta V_{BL} = \pm 40$  mV, both topologies have more than enough offset tolerance to overcome the impact of mismatches (as shown in Fig. 18 (a)) and since L-HYSA-QZ has its Z/ZB nodes starting to discharge from relatively higher voltages than the floating Z/ZB in L-HYSA-Q, it marginally takes more time to resolve compared to L-HYSA-Q (also observed in Fig. 10 (b)). Finally, Fig. 20 (e) reflects predicted results from Section IV that L-HYSA-QZ is capable of operating much faster than R-HYSA-QZ due to lower  $\mu_{VT}$  and  $\sigma_{VT}$ .

From the Temperature- $V_{DD}$  shmoo plots, Fig. 20 (f)-(j), measured at 5 MHz, it is clear that R/L-HYSA-QZs have similar

Fig. 21. (a)  $V_{DD-min}$  at  $F_{CLK} = 5$  MHz from the shmoo plots in Fig. 20. (Extracted from the measured shmoo plots.) (b) 5k MC simulations of  $\mu V_T$  (average threshold) across temperature for critical NMOS Transistor in R-V<sub>T</sub> and L-V<sub>T</sub> flavors.

or improved reliability coverage across temperature compared to conventional and intermediate topologies. Importantly, comparing R-HYSA-QZ with L-HYSA-QZ in Fig. 20 (j), latter offers improved coverage at lower temperatures and lower V<sub>DD</sub>. Fig. 21 (a) summarizes the V<sub>DD-min</sub> extracted from the Temperature-V<sub>DD</sub> shmoo plots in Fig. 20 (f)-(j) for each topology across -5 °C, 25 °C and 75 °C. At 25 °C, R-HYSA-QZ equals R-VLSA with the VDD-min of 260 mV whereas R-CLSA requires V<sub>DD-min</sub> of 300 mV. Similarly, at 25 °C, L-HYSA-QZ, L-HYSA-Q and L-CLSA-Z achieved VDD-min of 260 mV whereas V<sub>DD-min</sub> for L-CLSA was limited to 320 mV. All topologies offered reliable operation at and above 400 mV for the temperature range between -5 °C to 75 °C (with a minor exception for R-CLSA with  $V_{DD-min} = 420 \text{ mV}$  at -5 °C). The V<sub>DD-min</sub> for most topologies was mainly dictated by higher temperature as it reduces  $V_T$  (see Fig. 21 (b)) further increasing leakage and hence deteriorating the yield. However, in general terms, the V<sub>DD-min</sub> trend across temperature at a given F<sub>CLK</sub> for SAs in  $R-V_T$  and  $L-V_T$  flavors is dictated by the balance between yield affected by both leakage at higher temperatures and reduced sensing delay due to increased  $V_T$  at lower temperatures (see Fig. 21 (b)).

#### VI. SENSE AMPLIFIERS COMPARISON

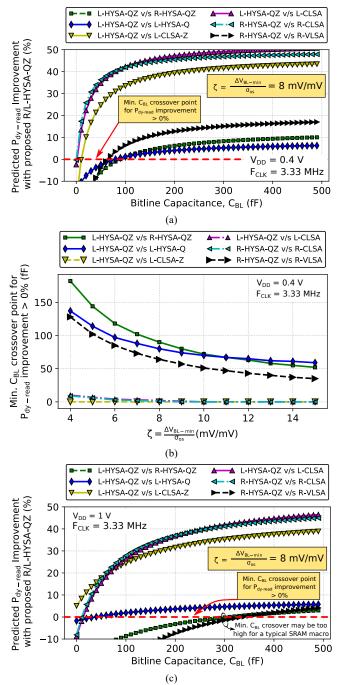

The resulting P<sub>dy-read</sub> with the consideration of increased Pdy-SA in the proposed R/L-HYSA-QZ topologies needs to be analyzed and compared with the resulting Pdy-read with other SAs. The P<sub>dy-read</sub> can be quantified as shown in eq. (1) where the  $P_{dy\text{-}BL/BLB}$  is the power consumption due to the bitline discharge defined by eq. (2) and the Pdy-SA is the SA dynamic power analyzed in Section IV and also defined by eq. (3). Note that other dynamic power components of the read access such as word-line drivers and control/timing are ignored in this comparative analysis as they would remain constant regardless of the choice of an SA. As emphasized by the work of [6], the amount of  $\Delta V_{BL}$  discharge in eq. (4) is determined by the combination of  $\sigma_{OS}$  of a given SA and the  $\zeta$  factor defined in eq. (5). The  $\zeta$  factor is indicated by the amount of  $\Delta V_{BL-min}$  required per  $\sigma_{OS}$  to meet certain Y<sub>read</sub> target for particular SRAM size in a given technology. For example, in the work of [6], for 28-nm CMOS and 16 Mb SRAM, the  $\zeta$  factor was found to be ~10mV/mV for 97 % yield target.

Since the P<sub>dy-read</sub> improvement is a function of bitline capacitance (C<sub>BL</sub>), the P<sub>dy-read</sub> improvement is analyzed across CBL comparing R-HYSA-QZ with R-VLSA and R-CLSA, and comparing L-HYSA-QZ with R-HYSA-QZ, L-HYSA-Q, L-HYSA-Z and L-CLSA. For the calculation of  $P_{dy-read}$ ,  $V_{DD} = 0.4$ V,  $F_{CLK} = 3.33$  MHz, measured  $\sigma_{OS}$  from Fig. 18 (c) and simulated values of  $P_{dy-SA}$  with appropriate  $\Delta V_{BL-min}$  calculated from eq. (4) were used. For example, for the  $\zeta$  factor of 8 mV/mV, Fig. 22 (a) shows the predicted P<sub>dy-read</sub> improvement with proposed R/L-HYSA-QZ. It shows the Pdy-read improvement across different values of CBL where the 0% crossover point is annotated to highlight the minimum CBL requirement for P<sub>dy-read</sub> improvement > 0%. At C<sub>BL</sub> of 150 fF, R-HYSA-QZ results in P<sub>dy-read</sub> improvement of 11% and 45% compared to R-VLSA and R-CLSA, respectively. Also, L-HYSA-QZ results in P<sub>dy-read</sub> improvement of 5%, 3.5%, 38%, and 46% compared to R-HYSA-QZ, L-HYSA-Q, L-CLSA-Z and L-CLSA, respectively. The  $\zeta$  factor is subject to vary depending on the SRAM memory size, target Y<sub>read</sub> and the

technology related effects such as proximity, stress effects, V<sub>T</sub> variations, and active area rounding [6]. Therefore, the minimum C<sub>BL</sub> crossover points were recorded as shown in Fig. 22 (b) for varied values of  $\zeta$  between 4 mV/mV to 15 mV/mV. The values for minimum C<sub>BL</sub> crossover points reduces with the increased values of  $\zeta$ , and for the lower values of  $\zeta$ , minimum C<sub>BL</sub> crossover points are within typical C<sub>BL</sub> range for an SRAM macro. This assures P<sub>dy-read</sub> savings with proposed R/L-HYSA-QZ topologies around threshold region. This analysis also highlights that utilizing L-V<sub>T</sub> flavor transistors in proposed HYSA-QZ topology ultimately provides

Fig. 22. (a) Predicted  $P_{dy-read}$  improvement with proposed R/L-HYSA-QZ at  $V_{DD} = 0.4$  V. (b) Minimum bitline capacitance (C<sub>BL</sub>) crossover point for  $P_{dy-read}$  improvement greater than 0% across different values of  $\zeta$  factor. (c) Predicted  $P_{dy-read}$  improvement with proposed R/L-HYSA-QZ at  $V_{DD} = 1$  V.

$P_{dy\text{-read}}$  savings compared to using  $R\text{-}V_T$  transistors around threshold region.

To further see the impact of the proposed R/L-HYSA-OZ with nominal supply in superthreshold region of operation, the analysis from Fig. 22 (a) was repeated with  $V_{DD} = 1 V$  and  $\zeta = 8 \text{ mV/mV}$ , and is shown in Fig. 22 (c). From Fig. 22 (c) it was evident that the R/L-HYSA-QZ can still provide savings in Pdv-read compared to other topologies within typical CBL range for an SRAM macro except R-VLSA (black line). R-HYSA-QZ can only provide Pdy-read improvement over R-VLSA at 1 V and  $\zeta = 8 \text{ mV/mV}$  if C<sub>BL</sub> is > 350 fF which is relatively high for a typical SRAM macro. Hence, in such situations, R-VLSA is preferred over the proposed R-HYSA-QZ. Similarly, the green line highlights that in such situations, R-HYSA-QZ is preferred over L-HYSA-QZ. In general, with superthreshold supply voltages, the choice of an SA remains debatable between R-VLSA, R-HYSA-QZ, and L-HYSA-QZ depending on the technology and CBL.

$$P_{dy-read} = P_{dy-BL/BLB} + P_{dy-SA} \tag{1}$$

$$P_{dy-BL/BLB} = C_{BL} \cdot V_{DD} \cdot \Delta V_{BL-min} \cdot F_{CLK}$$

(2)

$$P_{dy-SA} = P_{dy-SA-V_{DD}} + P_{dy-SA-BL/BLB} + P_{dy-SA-SAE}$$

(3)

$$\Delta V_{BL-min} = \zeta \cdot \sigma_{OS} \tag{4}$$

$$\zeta = \frac{\Delta V_{BL-min}}{\sigma_{OS}} \left(\frac{mV}{mV}\right) \tag{5}$$

The state-of-the-art on-chip fabricated SA topologies are compared with the proposed R/L-HYSA-QZs in Table II. The proposed SA in [19] relies on small-signal pre-amplification, offering 22% iso-layout-area improvement in  $\Delta V_{BL-min}$ compared to VLSA and VDD-min of 450 mV. The work from [22] deployed with small-signal preamplification circuit and finetuned MOM capacitor-based offset mitigation lowers the biterror-rate (BER) from 12% to 0% with two MOM capacitors area penalty in 2 metal layers compared to VLSA. The offset compensation technique in [23] relies on MOS capacitor-based threshold matching whereas [24] relies on body biasing-based calibration on power-up. SAs in both [23] and [24] achieve ~50% offset improvement with over ~3% overall SRAM layout area penalty compared to VLSA and CLSA, respectively. Our recent work in [25] employed with large signal differential and common mode boosting also implemented in 65 nm-GP CMOS achieves 23% offset improvement compared to R-VLSA at 0.3 V with 12% layout area overhead. The offset improvement in [25] is sensitive to the accuracy of its multi-phase timing and the supply voltage where the boosting benefits diminishes as the supply voltage is increased; as a result, optimum offset improvement was only within narrow supply range (0.3 V -0.6 V). The advantages of simply precharging internal nodes with bitlines in HYSA-QZ are simpler timing and relatively stable offset improvement over wider supply range (0.4 V – 1 V) as evident in Fig. 18 (c). The on-chip work in [16], similar to L-HYSA-Q, brings down BER from 2.8% to 1% with the layout area penalty of 16.8% compared to CLSA while offering record low subthreshold operation at 140 mV. The SA in [16] was implemented in low-leakage and Low-Power (LP) technology whereas this work was implemented in regular General-Purpose (GP) technology where the leakage is relatively higher due to significant degradation in Ion/IoFF ratio, ultimately constraining the data reproducibility in this work.