## University of Toronto, Faculty of Applied Science and Engineering Department of Electrical and Computer Engineering

## ECE 1387F - CAD for Digital Circuit Synthesis and Layout Handout #4 Assignment #1 - Maze Router

September 1999 J. Rose

**Assignment Date:** September 16

**Due Date**: Sept 30 (before lecture begins)

Late Penalty: -1 mark per day late, with total marks available = 10

You are to write an implementation of the FPGA maze router described in class, and have your program display its progress with X11-based graphics. A graphics package is provided for those working in the C language. Please note that your program must be able to run on a SUN/Solaris workstation, such as those in ECF or EECG.

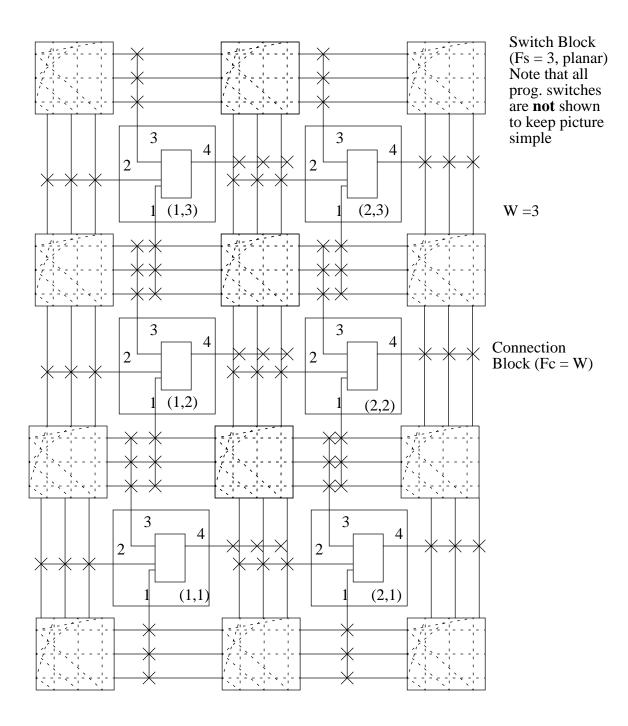

You should use the FPGA architecture described in class, as illustrated below in the figure on the next page. The figure shows the pin numbering scheme, and the x,y position scheme. Note that the entire switch block is not shown, just some of the connections. Make sure that you understand how the complete switch block looks, for any value of W.

Your program should take input from a file that has the following format:

The first line consists of one integer, n, where n is an integer giving the n x n dimension of the chip in logic blocks. The grid cells are numbered from 1 to N in each dimension.

The second line indicates the number of tracks per channel to use, W.

The next set of lines have the form "X1 Y1 P1 X2 Y2 P2". Each of these lines a pair of pins to be connected. The first pin is attached to the block at location X1,Y1, and uses pin number P1, where P1 = 1, 2, 3 or 4. The second pin is specified in the same manner by X2, Y2 and P2. This list is terminated by the pair -1 - 1 - 1 - 1 - 1.

## Example input file:

| 10             | (10 x 10) grid                                     |

|----------------|----------------------------------------------------|

| 3              | (3 tracks per channel)                             |

| 1 2 4 4 4 1    | Pin 4 on block at (1,2) connects to pin 1 at (4,4) |

| 3 3 4 8 9 3    | Pin 4 on block at (3,3) connects to pin 3 at (4,8) |

| -1 -1 -1 -1 -1 | (end of pin pair list)                             |

You should display the progress of your algorithm as it routes each step for each connection using a graphics display. Handout #5 gives details of a graphics package that you can use with the C language. You may use any other package and language as long as

it runs on a SUN sparcstation under X11R5.

You should test your program on the following test files in the directory ~jayar/1387/a1: fcct1, fcct2, fcct3 and fcct4

You are to find the smallest value of W for which those circuits will route successfully.

What to hand in:

- 1. A listing of your program.

- 2. The location of the executable file (where in your home directory), with instructions on how to run it. Make sure that the permissions on the file are set so that anyone can run it.

- 3. A paper plot of the results from the four test files. The graphics package allows you to do this. Include a discussion of the results and any attempts you made to improve the results.

- 4. The smallest number of tracks/channel (W) that your program could successfully route those circuits in. **Be sure that you understand this**: your program should be capable of varying the number of tracks per channel, and you are required to find the smallest number of tracks per channel that you program will successfully route the circuits in.

- 5. The most important part of what you hand in is a two-page description of the flow of your software, describing the major routines and data structures, and how they interact. Where you were faced with choices in your implementation of the algorithm, indicate what choices you made, and why.

Be sure to make all the relevant directories readable.