# ENHANCING AND USING AN AUTOMATIC DESIGN SYSTEM FOR CREATING FPGAS

by

Aaron Charles Egier

A thesis submitted in conformity with the requirements for the degree of Master of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto

Copyright  $\bigodot$  2005 by Aaron Charles Egier

### Abstract

Enhancing and Using an Automatic Design System for Creating FPGAs

Aaron Charles Egier

Master of Applied Science Graduate Department of Electrical and Computer Engineering

University of Toronto

2005

The creation of integrated circuits has progressed from custom design and layout to the less time-intensive implementation media of ASICs and FPGAs. FPGAs provide the lowest development cost and fastest development time; however, the design of the FPGA itself is still a time-consuming, expensive, custom layout task that takes at least 50 person-years to complete. This work explores new techniques to automate the design and layout of FPGAs. An existing automatic layout system is improved by changing the grouping of transistors that form the basic building blocks of the system. These improvements result in a 16.8% area savings over previous versions and only a 36% area increase compared to equivalent custom designs. The system was also extended to create the first automatic layout of an FPGA from a generic architecture description. These improvements and additions suggest that the automatic layout system is a viable alternative to custom layout of FPGAs.

### Acknowledgements

I would like to thank my supervisor, Professor Jonathan Rose, for his advice and guidance in all aspects of this work and my education. Also, Ian Kuon deserves my profound thanks and gratitude for his achievements and co-operation that led to the completion of this work. This work would not have been possible without the people who worked on it before me. They are Ketan Padalia, Ryan Fung, Mark Bourgeault, Josh Slavkin, and Chris Sun.

I am grateful to Simon So for providing additional cell layouts and Kostas Pagiamtzis for sharing his knowledge and experience regarding the fabrication of chips through CMC. In addition, Professor Rose's students and all the students in LP392 have been extremely helpful by offering new perspectives on this work.

Funding for this project was provided by Altera and the NSERC CRD program. CMC granted us silicon area without which it would not have been possible for us to fabricate our FPGA. I received funding for my studies from the University of Toronto and NSERC.

Thanks to my parents for their support and encouragement in all aspects of my life. Last but not least, to Katherine, I hope I can help you reach your goals as well as you have helped me reach mine.

# **Table of Contents**

| A        | bstra | let                                               | ii  |

|----------|-------|---------------------------------------------------|-----|

| A        | ckno  | wledgements                                       | iii |

| Li       | st of | Tables                                            | vii |

| Li       | st of | Figures                                           | ix  |

| Li       | st of | Acronyms                                          | xii |

| 1        | Intr  | oduction                                          | 1   |

|          | 1.1   | Motivation and Goals                              | 3   |

|          | 1.2   | Organization                                      | 3   |

| <b>2</b> | Bac   | kground                                           | 4   |

|          | 2.1   | FPGA Architecture                                 | 4   |

|          | 2.2   | VLSI                                              | 11  |

|          |       | 2.2.1 ASICs                                       | 14  |

|          | 2.3   | Related Prior Work                                | 14  |

|          |       | 2.3.1 Area Estimation                             | 14  |

|          |       | 2.3.2 Automatic Layout                            | 16  |

|          | 2.4   | The GILES Automatic FPGA Design and Layout System | 20  |

|          |       | 2.4.1 Netlist Generator                           | 23  |

|   |     | 2.4.2  | Placer                                          | 24 |

|---|-----|--------|-------------------------------------------------|----|

|   |     | 2.4.3  | Router                                          | 28 |

|   |     | 2.4.4  | Previous Results                                | 29 |

| 3 | Imp | orovem | ents to the GILES Automated FPGA Layout System  | 30 |

|   | 3.1 | A Nev  | v Area Model for Cells                          | 31 |

|   |     | 3.1.1  | Previous Area Model and Measurement of Accuracy | 32 |

|   |     | 3.1.2  | New Area Model                                  | 33 |

|   | 3.2 | Group  | oing Transistors into Cells                     | 40 |

|   |     | 3.2.1  | Functional Groupings                            | 46 |

|   |     | 3.2.2  | Groupings of Configuration SRAMs                | 52 |

|   |     | 3.2.3  | Combined Groupings                              | 66 |

|   | 3.3 | Tile A | area Compared to a Commercial FPGA              | 67 |

| 4 | Aut | comati | c Layout of a Complete FPGA                     | 69 |

|   | 4.1 | Archit | Secture                                         | 70 |

|   |     | 4.1.1  | Periphery Tiles                                 | 71 |

|   | 4.2 | Circui | t Design                                        | 73 |

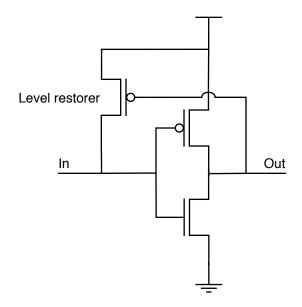

|   |     | 4.2.1  | Level Restorer                                  | 73 |

|   |     | 4.2.2  | Programming Infrastructure                      | 76 |

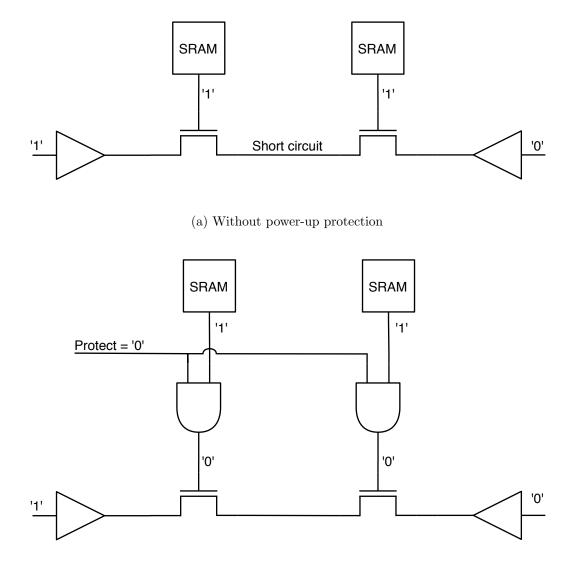

|   |     | 4.2.3  | Power-up Protection                             | 76 |

|   | 4.3 | Metal  | Layer Allocation                                | 77 |

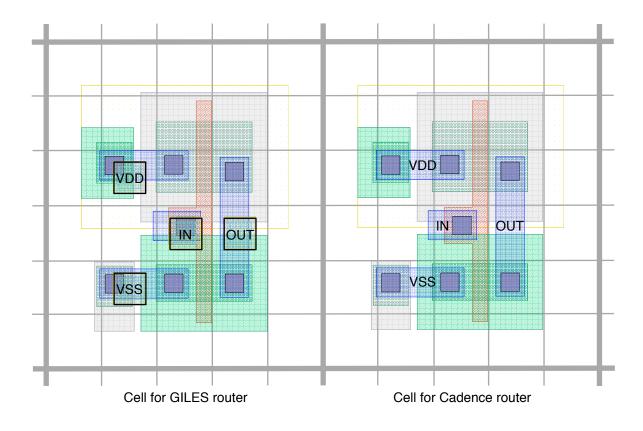

|   | 4.4 | Cell L | ayouts                                          | 80 |

|   | 4.5 | Creati | ing Tile Placements with GILES                  | 82 |

|   | 4.6 | Integr | ating with the Virtuoso Custom Design Platform  | 84 |

|   |     | 4.6.1  | Tile Placements                                 | 84 |

|   |     | 4.6.2  | Power Grid                                      | 85 |

|   |     | 4.6.3  | Clock Tree                                      | 90 |

|                                                             |       | 4.6.4   | Power-up Protection            | 92  |

|-------------------------------------------------------------|-------|---------|--------------------------------|-----|

|                                                             |       | 4.6.5   | Routing                        | 93  |

|                                                             |       | 4.6.6   | Tiling the Array               | 95  |

|                                                             |       | 4.6.7   | I/O Pads and Programmer        | 95  |

|                                                             | 4.7   | Verific | eation                         | 98  |

|                                                             | 4.8   | Design  | n Time                         | 99  |

| 5                                                           | Cor   | nclusio | ns                             | 102 |

|                                                             | 5.1   | Contri  | ibutions                       | 103 |

|                                                             | 5.2   | Future  | e Work                         | 103 |

| Appendix A Experimental Results for Transistor Groupings 10 |       |         | 105                            |     |

| Appendix B POWELL Architecture Description 12               |       |         | 122                            |     |

| $\mathbf{A}_{j}$                                            | ppen  | dix C   | POWELL Cell Layout Information | 124 |

| R                                                           | efere | nces    |                                | 126 |

# List of Tables

| 3.1  | Accuracy of old area model                                                        | 34  |

|------|-----------------------------------------------------------------------------------|-----|

| 3.2  | Accuracy of tile area with old area model                                         | 35  |

| 3.3  | Accuracy of new area model                                                        | 38  |

| 3.4  | Accuracy of tile area with new area model                                         | 39  |

| 3.5  | Verification of new area model                                                    | 39  |

| 3.6  | Parameters of ten experimental architectures                                      | 42  |

| 3.7  | Effect of cell border on tile area                                                | 43  |

| 3.8  | Distribution of cell types                                                        | 45  |

| 3.9  | List of functional groupings                                                      | 47  |

| 3.10 | Benefits of inter-cell SRAM bit swapping for the 2x2 SRAM grouping $\ .$ .        | 60  |

| 4.1  | Metal layer allocation                                                            | 79  |

| 4.2  | Cells used in POWELL and their sizes in 0.66 $\mu m$ by 0.66 $\mu m$ grid squares | 81  |

| 4.3  | Breakdown of time required to design POWELL                                       | 101 |

| A.1  | Tile area before routing for functional groupings                                 | 105 |

| A.2  | Tile area after routing for functional groupings                                  | 106 |

| A.3  | Tile whitespace before routing for functional groupings                           | 106 |

| A.4  | Tile area before routing for 2x2 SRAM grouping                                    | 107 |

| A.5  | Tile area after routing for 2x2 SRAM grouping                                     | 107 |

| A.6  | Tile wirelength before routing for 2x2 SRAM grouping 1                            | 108 |

| A.7  | Programming wirelength before routing for $2x2$ SRAM grouping          | 108 |

|------|------------------------------------------------------------------------|-----|

| A.8  | SRAM output wirelength before routing for 2x2 SRAM grouping            | 109 |

| A.9  | Tile area before routing for 4x4 SRAM grouping                         | 109 |

| A.10 | Tile area after routing for 4x4 SRAM grouping                          | 110 |

| A.11 | Tile wirelength before routing for 4x4 SRAM grouping                   | 110 |

| A.12 | Programming wirelength before routing for 4x4 SRAM grouping $\ldots$ . | 111 |

| A.13 | SRAM output wirelength before routing for 4x4 SRAM grouping            | 111 |

| A.14 | Tile area before routing for SRAM groupings                            | 112 |

| A.15 | Tile area after routing for SRAM groupings                             | 113 |

| A.16 | Tile wirelength before routing for SRAM groupings                      | 114 |

| A.17 | Programming wirelength before routing for SRAM groupings               | 115 |

| A.18 | SRAM output wirelength before routing for SRAM groupings               | 116 |

| A.19 | Tile area before routing for combined groupings                        | 117 |

| A.20 | Tile area after routing for combined groupings                         | 118 |

| A.21 | Tile wirelength before routing for combined groupings                  | 119 |

| A.22 | Programming wirelength before routing for combined groupings           | 120 |

| A.23 | SRAM output wirelength before routing for combined groupings           | 121 |

# List of Figures

| 2.1  | An island-style FPGA                                                    | 5  |

|------|-------------------------------------------------------------------------|----|

| 2.2  | A logic cluster                                                         | 6  |

| 2.3  | Basic logic element (BLE)                                               | 7  |

| 2.4  | Input and output connection blocks                                      | 8  |

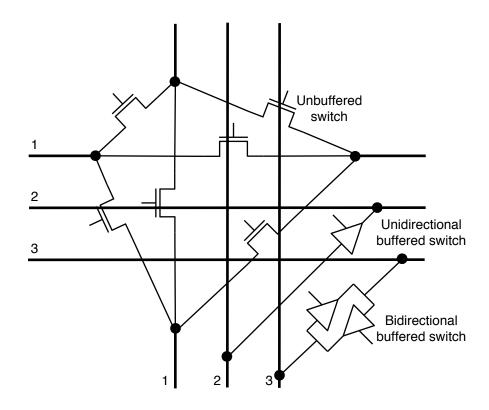

| 2.5  | Switch block                                                            | 9  |

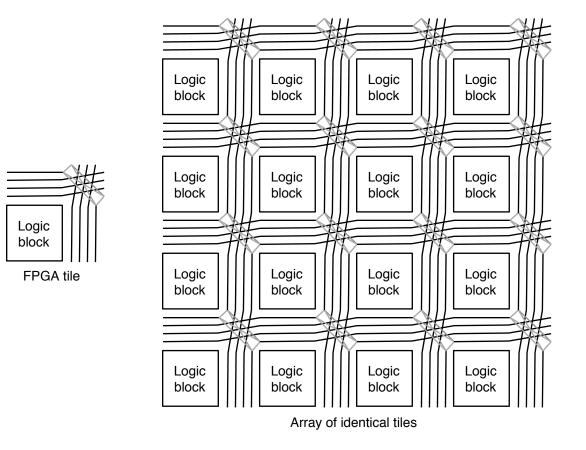

| 2.6  | FPGA tile and array                                                     | 10 |

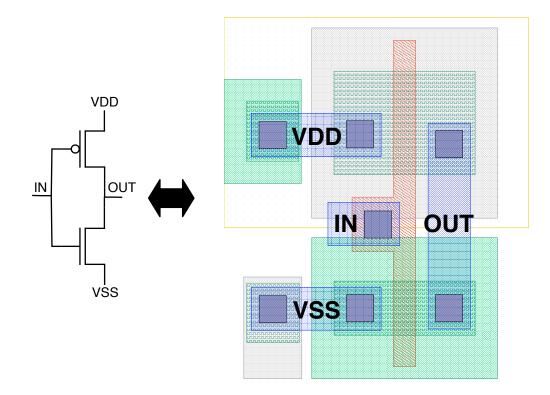

| 2.7  | Schematic and layout of an inverter                                     | 12 |

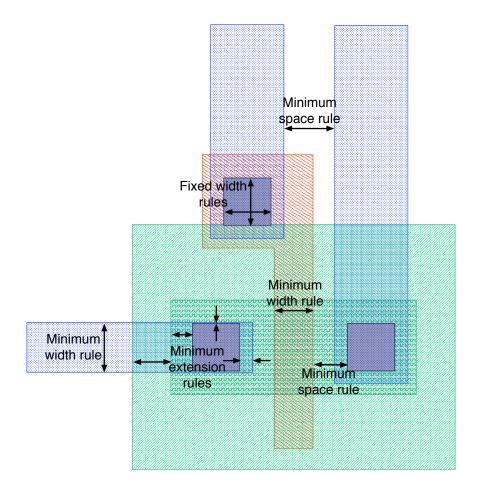

| 2.8  | Examples of design rules                                                | 13 |

| 2.9  | Diode prevents large voltage that could damage transistor gate          | 13 |

| 2.10 | ASIC design flow                                                        | 15 |

| 2.11 | Excerpt from a VPR architecture description file used as input to GILES | 21 |

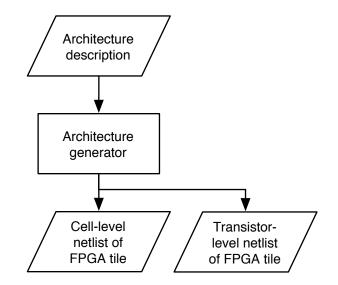

| 2.12 | GILES flow                                                              | 22 |

| 2.13 | VPR flow                                                                | 23 |

| 2.14 | Netlist generator based on VPR                                          | 24 |

| 2.15 | Placer algorithm                                                        | 26 |

| 2.16 | Initial and final tile placements                                       | 27 |

| 2.17 | Placer swaps logically equivalent pins                                  | 27 |

| 2.18 | Reweaving SRAM word and bit lines                                       | 28 |

| 3.1  | Required n-well spacing between inverter cells                          | 36 |

| 3.2  | Grouping cells saves border area                                        | 41 |

| 3.3  | Smaller cells result in less whitespace                                                 | 44 |

|------|-----------------------------------------------------------------------------------------|----|

| 3.4  | Average frequency of cell usage                                                         | 45 |

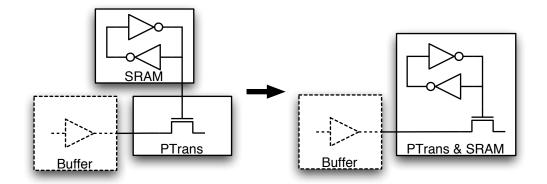

| 3.5  | Functional grouping number 1 (PTrans & SRAM)                                            | 47 |

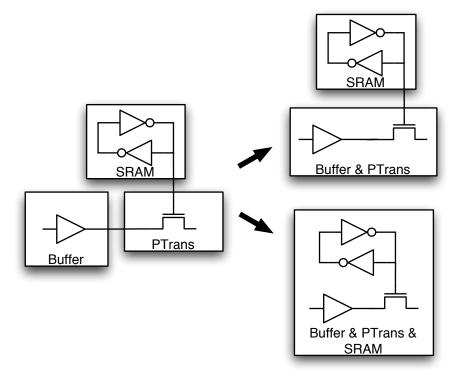

| 3.6  | Functional groupings 2 and 3 (Buffer & PTrans, Buffer & PTrans & SRAM)                  | 48 |

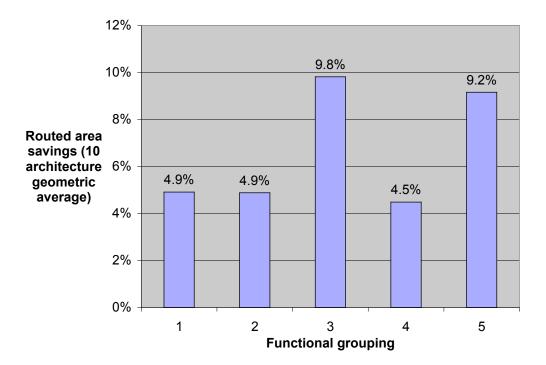

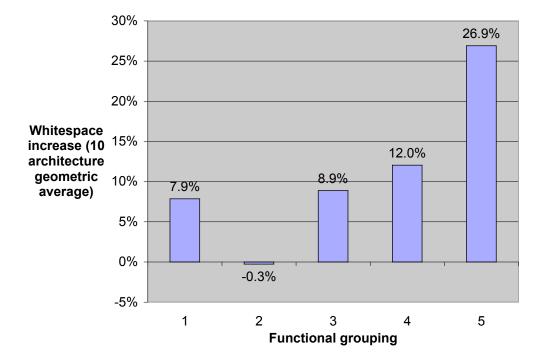

| 3.7  | Routed area comparison for functional groupings                                         | 50 |

| 3.8  | Whitespace comparison for functional groupings                                          | 51 |

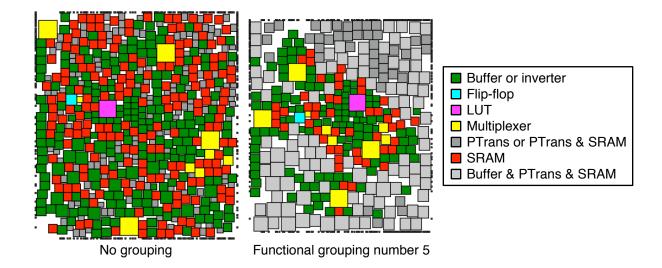

| 3.9  | 1x4-LUT tile placements with and without functional groupings $\ldots$ .                | 51 |

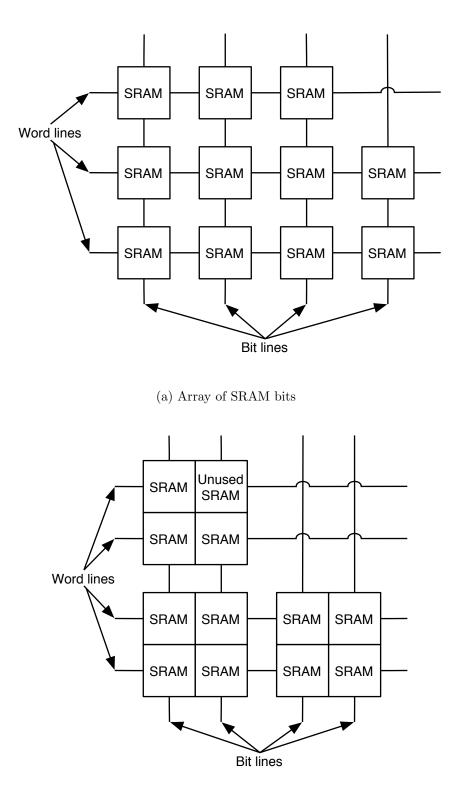

| 3.10 | Grouping of configuration SRAMs                                                         | 53 |

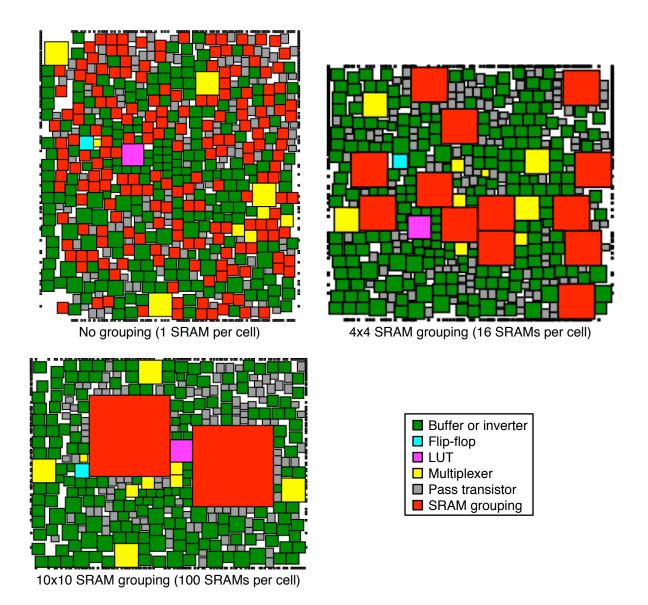

| 3.11 | 1x4-LUT tile placements with groupings of 1x1, 4x4, and 10x10 SRAMs .                   | 55 |

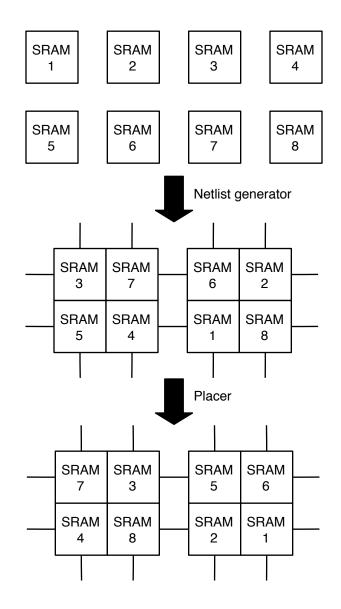

| 3.12 | Netlist generator creates random groupings then placer optimizes them $% \mathcal{A}$ . | 57 |

| 3.13 | SRAM bits cannot be programmed with different values                                    | 58 |

| 3.14 | SRAM bit swaps reduce wirelength                                                        | 59 |

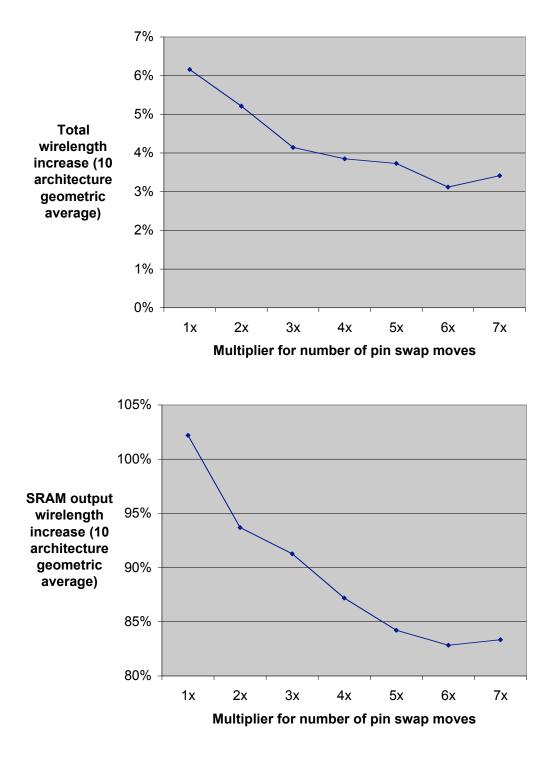

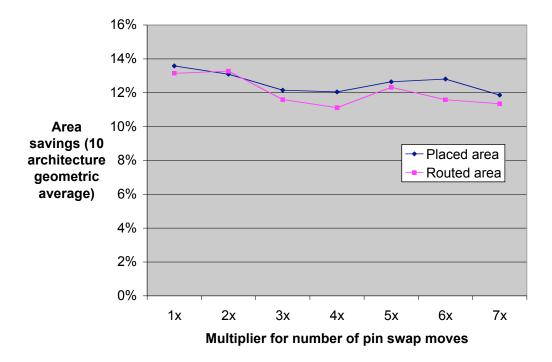

| 3.15 | Number of pin swap moves versus wirelength for 4x4 SRAM grouping $\ .$ .                | 62 |

| 3.16 | Number of pin swap moves versus area for 4x4 SRAM grouping $\ldots$ .                   | 63 |

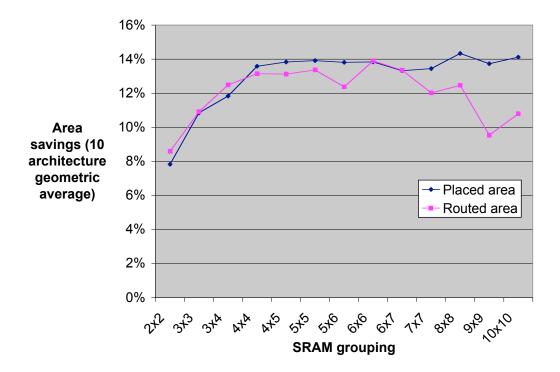

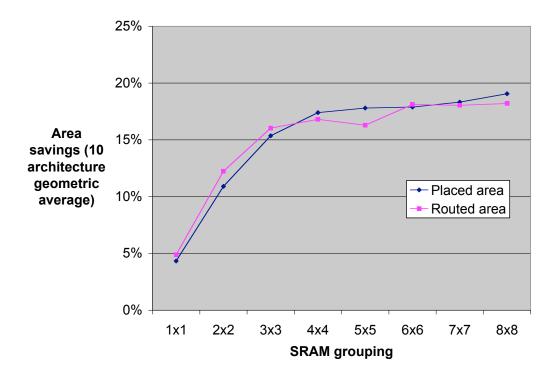

| 3.17 | Area comparison for SRAM groupings                                                      | 64 |

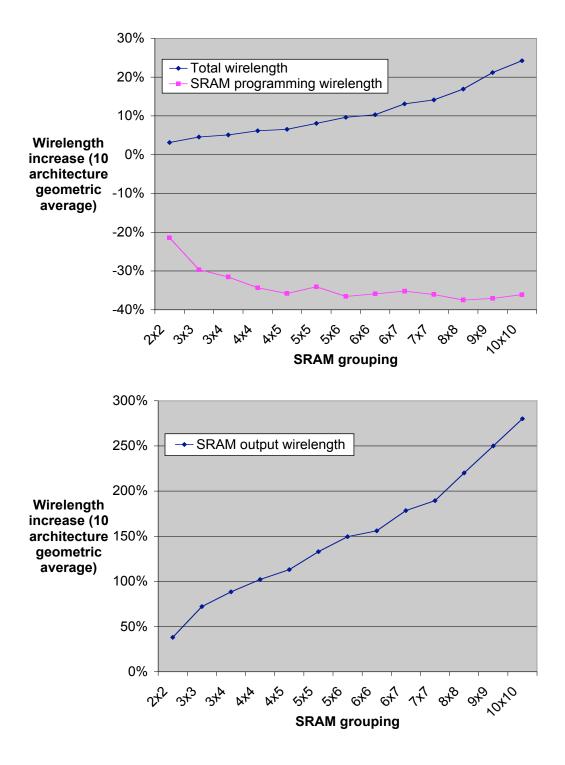

| 3.18 | Wirelength comparison for SRAM groupings                                                | 65 |

| 3.19 | Functional grouping number 2 combined with SRAM grouping                                | 67 |

| 4.1  | Array and periphery tiles                                                               | 72 |

| 4.2  | PMOS level restorer pulls high logic level to full voltage                              | 74 |

| 4.3  | Power-up protection prevents short circuit                                              | 78 |

| 4.4  | Cadence router does not require cell pins to be aligned to routing grid                 | 82 |

| 4.5  | Revised GILES flow                                                                      | 83 |

| 4.6  | Placement of main tile                                                                  | 86 |

| 4.7  | Power grid for main tile                                                                | 88 |

| 4.8  | Power grid regions                                                                      | 89 |

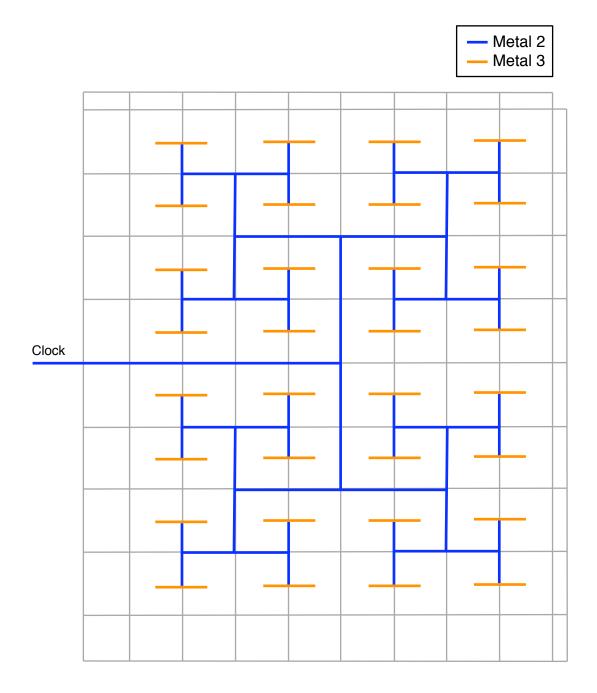

| 4.9  | Clock H-tree                                                                            | 91 |

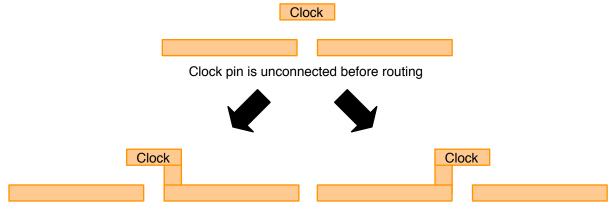

| 4.10 | Procedure for connecting clock pin to H-tree                                            | 92 |

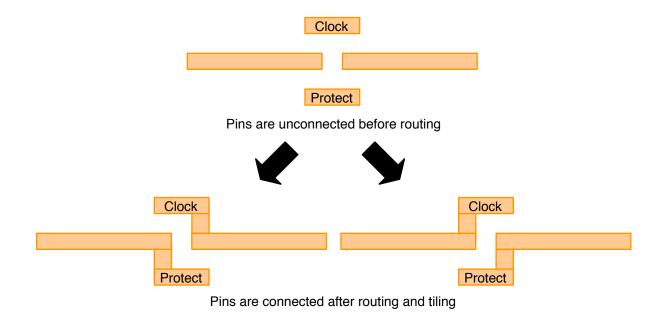

| 4.11 | Power-up protection pin uses unconnected clock wire      | 93  |

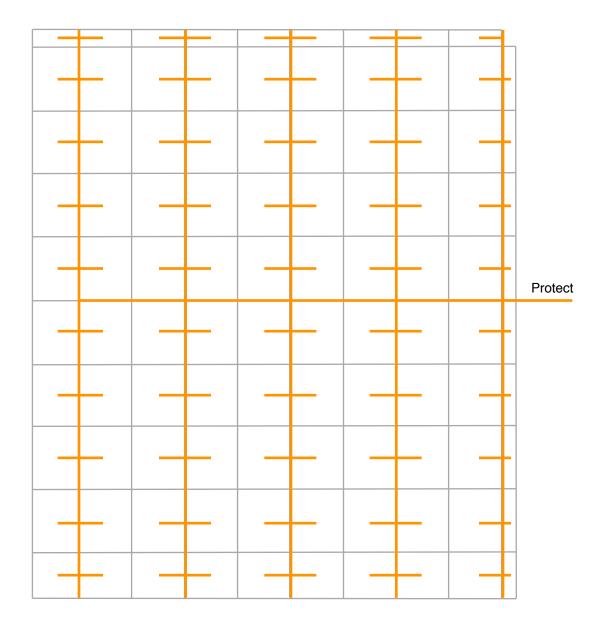

|------|----------------------------------------------------------|-----|

| 4.12 | Connections of power-up protection network between tiles | 94  |

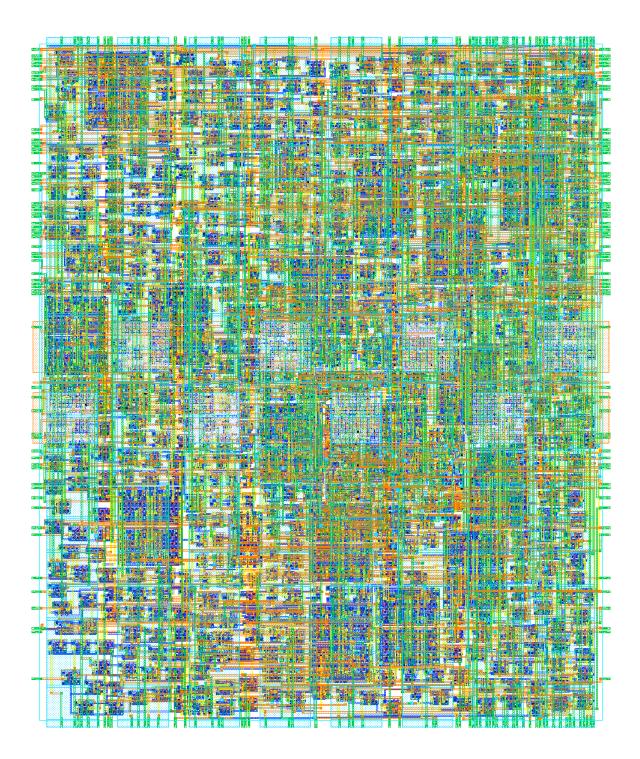

| 4.13 | Fully routed main tile                                   | 96  |

| 4.14 | Array of tiles                                           | 97  |

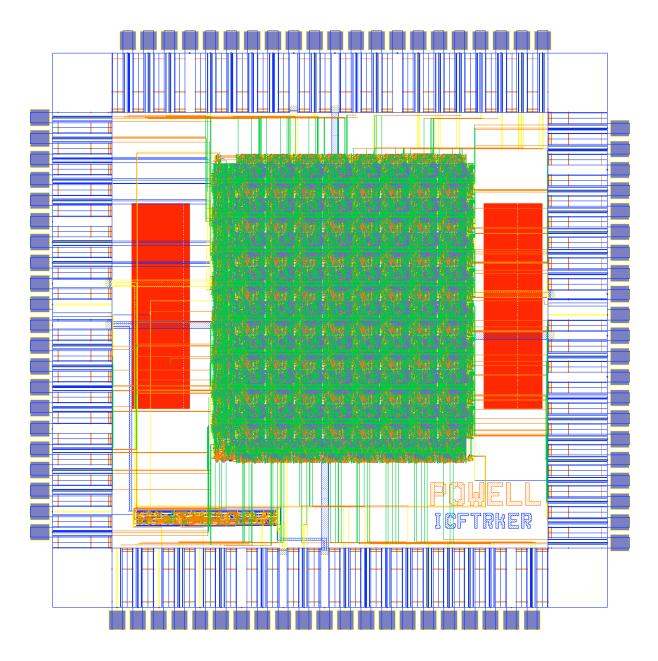

| 4.15 | POWELL layout                                            | 100 |

# List of Acronyms

| ASIC  | application-specific integrated circuit        |

|-------|------------------------------------------------|

| BLE   | basic logic element                            |

| СМС   | Canadian Microelectronics Corporation          |

| CMOS  | complementary metal-oxide-semiconductor        |

| DRC   | design rule check                              |

| FPGA  | field-programmable gate array                  |

| GILES | Good Instant Layout of Erasable Semiconductors |

| HDL   | hardware description language                  |

| IC    | integrated circuit                             |

| I/O   | input/output                                   |

| IP    | intellectual property                          |

| LUT   | look-up table                                  |

| LVS   | layout versus schematic                        |

| NMOS  | n-channel metal-oxide-semiconductor            |

| PGA   | pin grid array                                 |

#### **PMOS** p-channel metal-oxide-semiconductor

- **POWELL** Pushbutton Optimized Widely Erasable Logic Layout

- **SRAM** static random-access memory

- **TSMC** Taiwan Semiconductor Manufacturing Company

- **VLSI** very large-scale integration

- **VPR** Versatile Place and Route

## Chapter 1

## Introduction

The implementation of digital circuits has changed dramatically since the invention of the transistor in 1947 [1]. In the early years, circuits were designed with discrete components and connected on a circuit board. As the technology to create transistors improved, multiple transistors were integrated on a single chip to form logic gates. With time, entire circuits fit on a chip. When the size of integrated circuits (ICs) reached the scale of microprocessors, this level of complexity became know as very large-scale integration (VLSI) [2]. It became possible to create application-specific integrated circuits (ASICs) for unique applications. ASIC tools were developed to automate the design cycle and reduce the time to market [3]. Although these tools create ASICs that occupy more area, run at a slower speed, and consume more power compared to manually-designed, custom ICs, most applications are suitable to accept this tradeoff. Custom ICs are only used for the most advanced designs when area, speed, and power are critical.

In recent years, the complexity of IC fabrication processes has continued to increase requiring more optical lithography masks at an increased price. In addition, once the masks have been made, the cost to modify the IC for bug fixes or feature enhancements is similarly increased. This has created a market for a new class of ICs called field-programmable gate arrays (FPGAs) that can be programmed to implement any circuit [4]. The companies that create FPGAs incur the cost of fabrication and sell them to customers who are willing to spend more per chip to reduce development costs, risks, and manufacturing time. FPGAs also reduce costs because they can be reconfigured for bug fixes and feature enhancements. These savings makes FPGAs attractive even though they are slower and use more power than ASICs.

The market for FPGAs is increasing but so is their complexity and the time required to design them. To compete with ASICs, FPGA companies use custom IC design techniques to reduce area and power while increasing speed. The standard ASIC flow cannot meet these requirements. Thus, FPGA companies must spend on the order of at least 50 person-years to create new FPGAs.

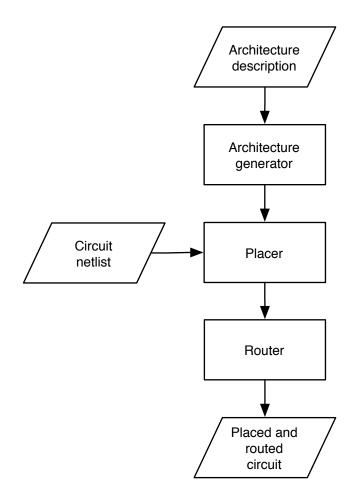

Previous work at the University of Toronto has created a software tool that reduces the time to develop FPGAs [5]. The inputs to that system are an architectural description of the FPGA and the mask layouts of custom cells that implement the basic building blocks of the architecture. The output is a placed and routed netlist of the FPGA tile. The tile is repeated to create large FPGAs. Creating a new FPGA with a different architecture is achieved by changing a few lines in the input file and providing a different set of custom cells optimized for the new architecture. Therefore, the time to design an FPGA is no more than the time required to design the custom cells. This is dramatically less time than the full custom approach.

This tool, named Good Instant Layout of Erasable Semiconductors (GILES), contains a placer and router similar to those used in ASIC tools. However, it addresses some of their shortcomings without sacrificing the benefit of reduced time to market. ASIC tools use standard cells to implement basic logic functions. These cells are generic and not optimized for specific circuits [3]. Instead the custom cells used by GILES are optimized for each specific FPGA architecture. This hybrid custom/ASIC approach allows GILES to achieve silicon area smaller than ASIC tools and near that of custom designs. In addition, GILES places these cells more efficiently than ASIC tools by using optimizations specific to FPGAs.

#### **1.1** Motivation and Goals

The first version of GILES obtained promising results. However, many assumptions were made that can be revisited and explored for improvement. One such assumption, which has a large impact on area, is the choice of custom cells. The first goal of this work is to revisit this choice to achieve area results closer to that of commercial FPGAs designed using custom flows. Part of that goal is to obtain more accurate results by improving the models needed to estimate the area of the custom cells.

The second goal of this work is to extend GILES to create a complete, fully-functional FPGA. In the previous version, many issues were ignored regarding the power grid, clock network, and programming circuitry that must be resolved. The overriding theme is to automate the entire process and to provide the flexibility to quickly implement alternative architectures.

### **1.2** Organization

The remainder of this dissertation is divided into four chapters. Chapter 2 provides a background on FPGA architecture, VLSI design methodologies, and prior work that contrasts with GILES. Chapter 3 describes tradeoffs in choosing the custom cells used by GILES and which choices achieve smaller chip area. Chapter 4 explains our proof-ofconcept FPGA and the issues surpassed during the design process. Also, it discusses the infrastructure implemented to automate most of the steps involved. Finally, Chapter 5 concludes and provides suggestions for future work.

## Chapter 2

## Background

This chapter is divided into four sections. It begins with a review of FPGA architecture focusing on the features used in this work. It follows with a brief background on VLSI design methodologies. Then it examines other approaches to automatic layout of FPGAs. Finally, the chapter concludes with an explanation of the GILES system flow, which is the basis for the present work, and the previous results obtained with it.

## 2.1 FPGA Architecture

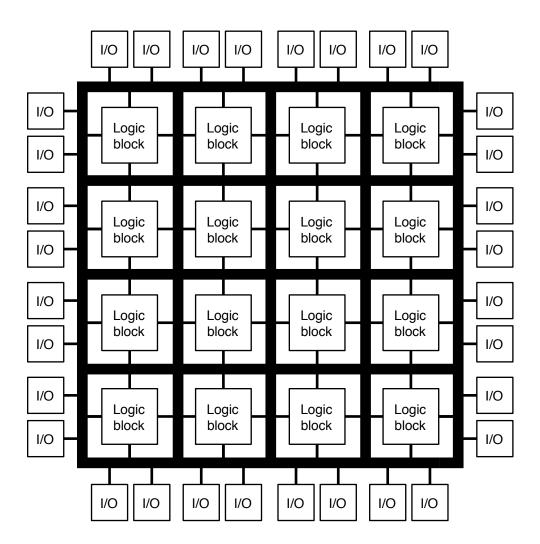

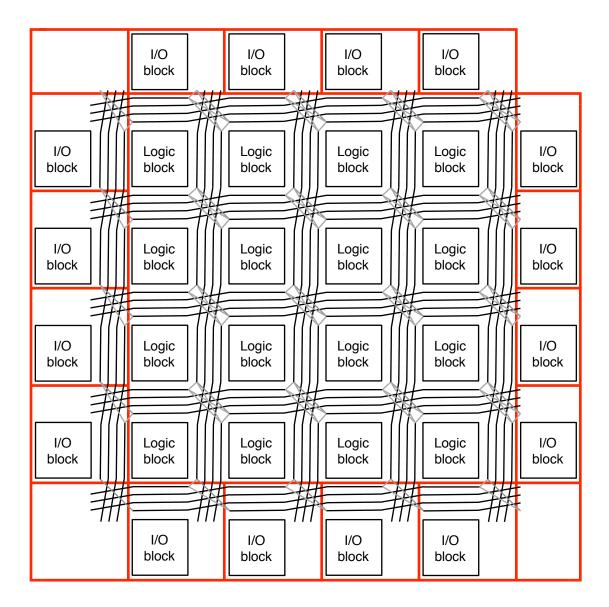

FPGAs are designed to implement any logic circuit. Their inherent reconfigurability derives from their programmable architecture. The main parts of the FPGA are the logic blocks, the input/output (I/O) blocks, and the routing [4]. All are programmable using static random-access memory (SRAM) to allow different connections and functionalities. Their arrangement for an island-style FPGA is shown in Figure 2.1. The logic blocks are distributed in an array with the routing fabric running between them. The I/O blocks surround the logic blocks and routing tracks. The direction of each I/O block and their connections to the routing tracks are configurable.

The logic blocks implement arbitrary logic functions. Connections are made between them with the programmable routing fabric. The inputs and outputs of the logic block

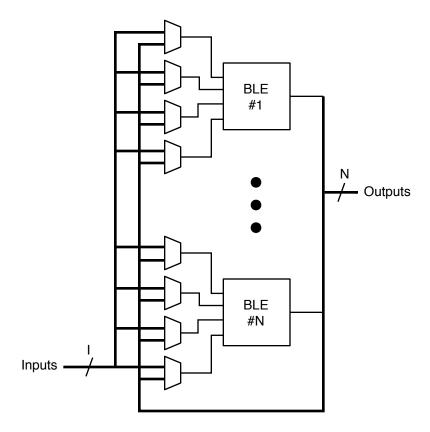

Figure 2.1: An island-style FPGA

Figure 2.2: A logic cluster

connect to some of the adjacent routing tracks. Logic blocks are often implemented with clusters of one or more basic logic elements (BLEs) as shown in Figure 2.2. This structure is called a logic cluster. The inputs to the BLE are selected using multiplexers from the set of inputs to the logic block and the set of BLE outputs. These multiplexers are called input crossbars and in this work they are fully populated meaning all logic block inputs and BLE outputs are connected to each multiplexer. Configuration SRAM bits select which signals are connected to each BLE.

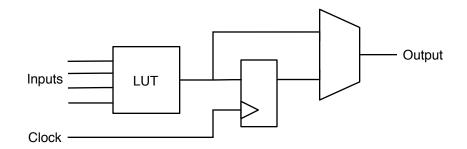

A BLE is often composed of a look-up table (LUT) and a flip-flop. A K-input LUT implements an arbitrary K-input combinational logic function and the flip-flop allows sequential circuits to be created. The BLE circuit used in this work is shown in Figure 2.3 and employs a four-input LUT and a flip-flop. The output of the BLE is either registered or unregistered based on a configurable multiplexer. In this figure, the LUT has four

Figure 2.3: Basic logic element (BLE)

inputs so it can realize any logic function of four inputs. It is typically implemented with a 16-input multiplexer. The four inputs of the LUT connect to the select lines of the multiplexer. They select one of sixteen SRAM bits that correspond to the entries of the truth table.

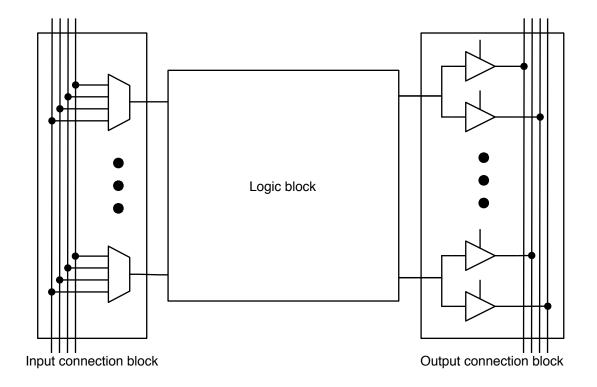

The configurable connections from the routing tracks to the inputs of the logic block are implemented with multiplexers as shown in Figure 2.4. The programmable output connections from the logic block to the routing tracks are made with buffered switches and are also shown in Figure 2.4. These are called the input and output connection blocks, respectively. The number of routing tracks that connect to each logic block input or each output is know as the connection block flexibility and is represented as  $F_{c,input}$ or  $F_{c,output}$  [6]. In Figure 2.4,  $F_{c,input}$  is four and  $F_{c,output}$  is two. Similarly, the number of routing tracks that connect to each I/O block for both input and output is represented as  $F_{c,pad}$ .

The routing wires may stretch the length of one logic block or they may span multiple blocks. The number of logic blocks a routing track spans is know as its length. All routing wires may be of the same length or some fraction of them may be different lengths. Routing wires can be connected together at their ends and where they cross. A set of programmable switches allows these connections. They can be buffered or unbuffered switches as shown in Figure 2.5. The buffered switches can also be unidirectional or bidirectional. The set of switches is called a switch block and the number of possible

Figure 2.4: Input and output connection blocks

connections each wire can make is called the switch block flexibility,  $F_s$  [6]. In this figure,  $F_s$  is three for the first routing track in both the horizontal and vertical channels.

It is desirable to use the regular structure of FPGAs to simplify their design and physical layout. An FPGA tile refers to a logic block and one set of adjacent horizontal and vertical routing tracks. This tile is repeated in an array to form the FPGA as shown in Figure 2.6. Since most FPGA architectures require routing tracks that span more than one tile yet not the entire length of the chip, Figure 2.6 also shows how "twisting" the routing tracks achieves other track lengths [7]. In this figure, all routing tracks are length four.

Figure 2.5: Switch block

Figure 2.6: FPGA tile and array

### 2.2 VLSI

Implementing massive circuits on a single chip is called very large-scale integration (VLSI). These chips are fabricated on silicon wafers using chemical and mechanical processes. Many stages of oxidation, diffusion, deposition, ion implantation, metallization, and polishing are performed to create the chip [8]. Photolithography masks are used to selectively perform each task on different areas of the wafer. These masks are derived from layouts containing two dimensional diagrams of each layer. A complementary metal-oxide-semiconductor (CMOS) process is designed to implement both p-channel metal-oxide-semiconductor (PMOS) and n-channel metal-oxide-semiconductor (NMOS) transistors. Ion implantation dopes the silicon with n+ or p+ impurities. Transistors are created where active n+ and p+ diffusion regions intersect with the polysilicon layer that forms the gate of the transistor [1]. For the process used in this work, PMOS transistors must be contained in a n-well region. Contacts connect active n+ and p+ diffusion regions as well as polysilicon to the first metal layer. Several metal layers exist in modern processes and they are connected with vias. An example layout of an inverter is shown in Figure 2.7. To connect wires off chip, large bonding pads are used. After fabrication, the wafers are cut into chips and wires are bonded between the pads and the pins of the chip package.

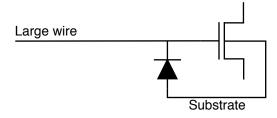

To ensure that the layout is manufacturable, each fabrication process has a list of design rules that must be met [1]. As part of the design flow, these rules must be verified with design rule check (DRC) software. Figure 2.8 shows rules involving minimum width, fixed width, and minimum spacing of some drawing layers as well as extensions of one layer over another. The exact specifications for each rule are different for each process. Other rules involve minimum area of an object and minimum density across the entire chip. For finer geometry processes, large metal wires can act as unwanted antennas and build up charge during fabrication, potentially causing damage to transistor gates [9]. Antenna rules dictate when a wire is likely to cause this problem. Connecting a diode as

Figure 2.7: Schematic and layout of an inverter

shown in Figure 2.9 prevents a large voltage between the gate and the substrate. During normal operation, the substrate is grounded so the diode is reverse biased and the circuit functionality is unaffected.

Making sure the design is free of DRC and antenna errors improves fabrication yield; however, it does not guarantee the design will work to specifications or at all. To verify the design, a schematic is extracted from the layout [1]. The extracted version represents the circuit that is implemented by the layout. It is compared to the original design schematic using a process called layout versus schematic (LVS). If the netlists match it is likely that the layout will behave the same as the schematic simulation. To provide more confidence, the extracted view can be simulated with the extracted parasitic capacitors and the correct diffusion area resistances.

Figure 2.8: Examples of design rules

Figure 2.9: Diode prevents large voltage that could damage transistor gate

#### 2.2.1 ASICs

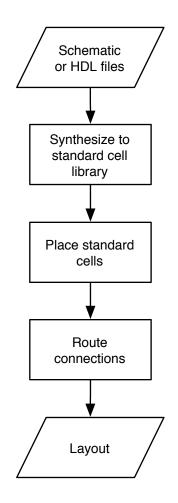

VLSI design methodologies include ASIC and custom flows. Custom IC design involves drawing every geometric shape on every layer needed to create photolithography masks. ASIC tools automate the design process to reduce development time at the expense of decreased speed and increased area and power [3]. A simplified ASIC design flow is shown in Figure 2.10. Design specification is done using a schematic or hardware description language (HDL). This is synthesized to a netlist of components from an ASIC library. These components, called standard cells, contain transistor layouts designed for various functions such as logic gates and flip-flops. The cells, which are required to be of equal height but have variable width, are placed on a grid and the connections between them routed using automated tools.

### 2.3 Related Prior Work

This section divides related prior work into two categories. Section 2.3.1 examines previous techniques to estimate the layout area of cells. Section 2.3.2 reviews relevant portions of the vast field of automatic layout.

#### 2.3.1 Area Estimation

Layout designers often estimate the layout area of an IC before completing the entire design process. This gives designers early information about the IC's size that can help with floorplanning and with evaluating the silicon area and packaging requirements. Several approaches exist for estimating the area of standard cell designs assuming the area of each standard cell is known [10, 11].

In this work, we compare the tile area of many FPGA architectures. An automatic layout tool determines the exact tile area based on the size of the custom cells in the tile netlist. However, the set of custom cells required for an FPGA tile changes with the

Figure 2.10: ASIC design flow

FPGA architecture. It would be very time consuming to layout every cell used in every experimental architecture to obtain the area of all possible cells. Instead, the area of each cell is estimated based on its transistor implementation.

Few researchers have looked at area estimation of ICs based on the transistor implementation. Wu et al. [12] propose formulas for estimating the size of datapath and control logic based on the transistor implementation of standard cells. They sum the number of transistors in the design and multiply by the pitch between transistors and the height of the standard cells.

Betz et al. [4] estimate the layout area of FPGAs. They measure area in terms of the number of minimum-width transistors that exist in the layout. However, many transistors are larger than minimum width to increase their drive strength. Betz et al. devised an equation to determine the area of each transistor, i, in terms of the number of minimum-width transistors that occupy the same area:

$$area_i(minWidthTransistors) = 0.5 + \frac{driveStrength_i}{2 \times minWidthDriveStrength}$$

(2.1)

This equation recognizes that a transistor with 2x drive strength takes up less space than two 1x transistors. Betz et al. sum the result of Equation 2.1 for all the transistors in the FPGA. Then to obtain the area in  $\mu$ m<sup>2</sup>, they multiply by the layout area required for a minimum-width transistor. They also assume custom designers achieve 60% of the maximum transistor density so they divide the final area by 0.6.

#### 2.3.2 Automatic Layout

There is an extensive body of work on automatic layout [13, 14] as well as widely used commercial tools. These projects and tools can be classified depending on whether the layout is performed at the transistor-level or the cell-level. In addition, floorplanning, which determines the high-level layout structure, can be performed using automatic tools. After reviewing different techniques, this section examines automatic layout projects that target FPGAs.

#### **Transistor-Level Layout**

A research project by Serdar and Sechen [15] explored automatic layout at the transistorlevel. Their tool, AKORD, performs automatic layout for small groups of transistors. Their results indicate automatic layout is comparable to manual layout for up to fifty transistors; however, no results are presented for larger designs. Synopsys has a commercial tool called Cadabra for the automatic creation of standard cells from a transistor-level netlist [16]. Again it is designed for small circuit sub-blocks (typically standard cells) and not a whole chip. While these tools could be used to create cells for cell-level automatic layout, they do not scale well enough to create automatic layouts of entire FPGAs or even FPGA tiles on their own.

#### Cell-Level Layout

An approach that scales to a larger number of transistors is to break the problem into two levels of hierarchy. At the bottom-level, the transistors are grouped into cells with two to twenty transistors and their layout is performed manually or with transistor-level automatic layout tools. The top-level netlist is composed only of these cells. The position of the cells in the top-level layout is determined automatically using a placement tool and connected automatically using a router.

Cell-level layout can be classified into standard cell layout and general cell (or building block) layout [13]. Standard cells have a fixed height and variable width. They have power and ground wires running along the top and bottom of the cells. Abutting standard cells horizontally connects the power and ground nets. General cells have variable width *and* height. The power and ground connections must be connected by a router. Standard cells are part of the ASIC design flow described in Section 2.2.1. Libraries of these cells are available so the layouts are created once and used repeatedly. The present work uses general cells like the work by Ogawa et al. [17] and Onodera et al. [18]. General cells are not used in ASIC designs because of the lack of cell libraries and the increased difficulty in routing power and ground.

Chinnery and Keutzer [3] compare automated ASIC designs that use standard cells to custom designs where the layout of the entire IC is performed manually. While ASIC tools dramatically reduce layout time, they found that ASIC designs are three to eight times slower than custom designs. This performance gap is partially attributed to restrictive standard cell ASIC libraries that often limit the choice of cells and result in non-optimal drive strength. The standard cell libraries also provide poor latches and lack dynamic logic gates used in high-performance custom ICs. Chinnery and Keutzer give suggestions for improving the quality of ASIC designs. They suggest adding application-specific standard cells to the library as well as better logic design, pipelining, and floorplanning. In one chapter of their book, which was contributed by Chang and Dally, an ASIC implementation of a 64-bit microprocessor register fetch stage was found to be 14.5x larger and 3.72x slower than a custom implementation. By adding some manual layout effort to exploit the regularity of each bit-slice and to add application-specific standard cells to the library, the partially automated design was only 1.64x larger and 1.11x slower than the custom implementation.

#### Floorplanning

Floorplanning determines the placement of large blocks such as intellectual property (IP) cores, embedded memories, and groups of standard cells. The area of each block is fixed but there may be several alternative layouts with different shapes [14]. It is similar to general cell layout but the shape of each block has to be determined in addition to its placement. Floorplanning is performed manually or with automatic tools. Some of these tools attempt to minimize the placement area and eliminate the whitespace between blocks [19] while others optimize the placement within a fixed area [20]. When the

area is fixed, the goal is to distribute the whitespace between the cells to reduce routing congestion. Some floorplanning tools also allow the blocks to be mixed with standard cells and the tool will perform standard cell placement at the same time as floorplanning [21].

#### Automatic Layout of FPGAs

Most previous approaches to the automatic layout of FPGAs have employed the standard cell design flow. Phillips and Hauck applied a standard cell flow to implement a reconfigurable datapath architecture called RaPiD [22]. This architecture is similar to a one-dimensional FPGA with datapath operations for logic blocks. They obtain a standard cell version of RaPiD that is 42% larger and 64% slower than the custom implementation. They improve this result by targeting a specific set of circuits and removing reconfiguration flexibility that is not necessary for those specific circuits. This technique achieves designs that are up to 46% smaller and 36% faster than the original custom implementation. While the results are promising, these chips are not nearly as flexible as a general purpose FPGA. Phillips and Hauck also achieve benefits from adding FPGA-specific standard cells to the ASIC library. They reduced the area of their various standard cell versions by 9% to 18.9% and improved the speed by 7% to 36%.

A similar approach by Kafafi, Bozman, and Wilton uses a standard cell flow to create small customizable FPGA cores for use as part of an IC [23]. They simplify the programmable architecture by removing flip-flips and combinational loops and rely on external logic to perform these functions. The results show that the automated approach creates designs 6.4 times larger than the custom implementations of their FPGA cores. Clearly, it is challenging to create FPGAs using existing ASICs tools that are similar in size to custom FPGAs.

In the present work, we employ an automatic layout tool called GILES [5]. The next section discusses how GILES works compared to previous approaches.

## 2.4 The GILES Automatic FPGA Design and Layout System

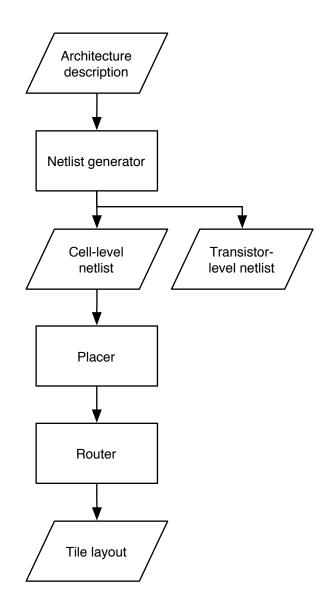

There are several features that make GILES [5] unique compared to other previous work on automatic layout of FPGAs. It is similar to the general cell layout approach so it handles large numbers of transistors; however, it uses a custom placer with optimizations specific to FPGAs so it outperforms standard cell design flows on FPGA-specific layouts. A key feature is that it is the only automatic layout tool that uses a high-level architectural description as input to specify the FPGA structure. The architecture description is easily understandable and configures most of the architectural parameters described in Section 2.1. Its format is the same as the architecture file used in the architecture exploration tool called Versatile Place and Route (VPR) [4].

An excerpt of an architecture description file is shown in Figure 2.11. It specifies one BLE per cluster with a four-input LUT. The logic block has four inputs, one output, and a clock for the flip-flop. The connection block flexibilities are specified as a fraction of the routing tracks instead of an absolute number so they adjust when a different number of routing tracks is used. The file also specifies that half the routing tracks are buffered. All the routing tracks have a length of four.

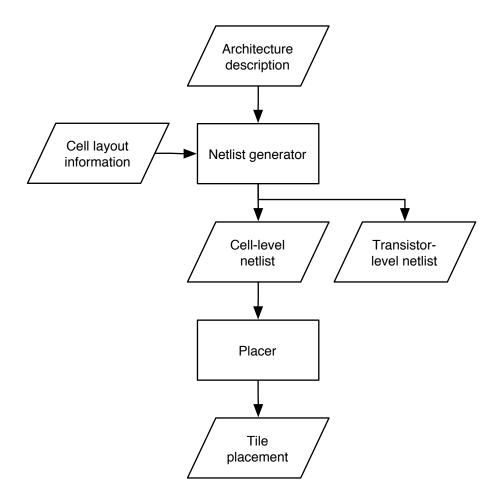

The previous version of GILES focused on the automatic layout of a single FPGA tile. The tile is repeatable as illustrated in Figure 2.6. The GILES tool flow is illustrated in Figure 2.12. It begins with an architecture description and finishes with the layout of the tile. The first stage is the netlist generator. It translates the architecture description into two netlists: one composed of cells and one of transistors. The next stage places the cell-level netlist. Finally, the connections are routed to obtain the layout.

```

# Logic block parameters

subblocks_per_clb 1  # 1 BLE per logic cluster

subblock_lut_size 4 # 4-input LUTs

# Logic block inputs and outputs

inpin class: 0 bottom

inpin class: 0 left

inpin class: 0 top

inpin class: 0 right

outpin class: 1 bottom  # Logic block output

inpin class: 2 global left # Clock input

# Connection block flexibilities

Fc_type fractional# Specified as fractional number of tracksFc_input 0.5625# Flexibility of input connection blockFc_output 1# Flexibility of output connection block

Fc_pad 1

# Flexibility of I/O pads

# Switch types

switch 0 buffered: no ...

switch 1 buffered: yes ...

# Length 4 routing tracks, half buffered

segment frequency: 0.5 length: 4 wire_switch: 0 ...

segment frequency: 0.5 length: 4 wire_switch: 1 ...

```

Figure 2.11: Excerpt from a VPR architecture description file used as input to GILES

Figure 2.12: GILES flow

Figure 2.13: VPR flow

#### 2.4.1 Netlist Generator

The netlist generator is based on the architecture exploration tool called VPR [4]. VPR places and routes circuits on an FPGA. The goal of VPR is to easily implement circuits on different architectures. As shown in Figure 2.13 the inputs are a circuit netlist and an architecture description of the FPGA on which to implement that circuit. The output is the placement and routing of an application circuit on the specified FPGA. This should not be confused with the goal of this work, which is the placement and routing of the FPGA itself.

VPR was not designed to create FPGAs. However, it has an internal representation of the FPGA and its programmable routing in the form of a routing-resource graph. The

Figure 2.14: Netlist generator based on VPR

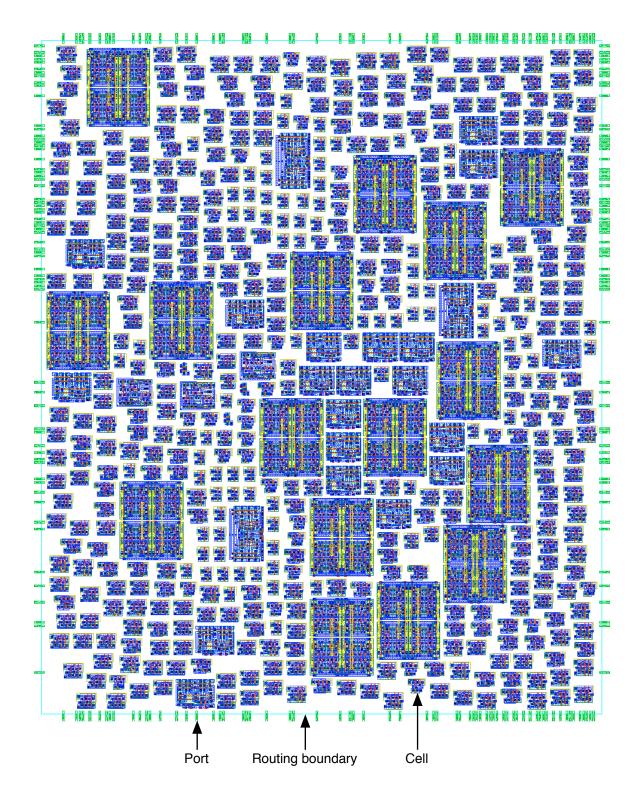

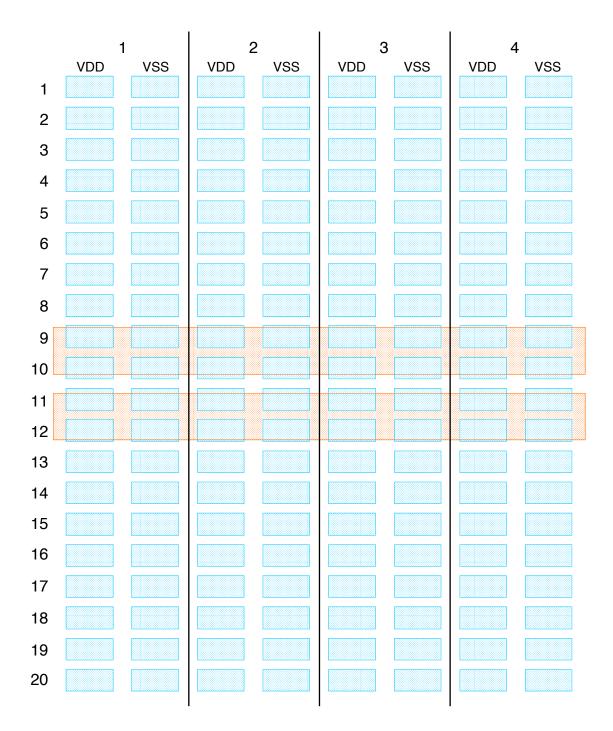

netlist generator of GILES is a modified version of VPR that outputs a transistor-level netlist and a cell-level netlist of the FPGA tile based on the logic block structure and the routing-resource graph as shown in Figure 2.14 [24]. Instead of using standard cells taken from an ASIC library for the cell-level netlist, the netlist generator assumes the creation of custom, general cells optimized for the specific FPGAs architecture. The transistor-level netlist contains the transistor implementation of each cell. Additionally, the netlists describe the connections out of the tile, called ports. Because the tile will be abutted to copies of itself to create the array, ports on each side of the tile will connect to ports on the opposite side. Therefore, each port must match up with another port called its "tiling partner". The tiling partners are labelled so the placer knows to keep them aligned.

# 2.4.2 Placer

The placer reads in the cell-level netlist and outputs the placement of the tile. The placer's goal is to minimize area and wirelength [5]. It begins with a random placement and moves the cells to minimize its cost function. Whether an attempted move is accepted

is based on a simulated annealing algorithm [25, 26].

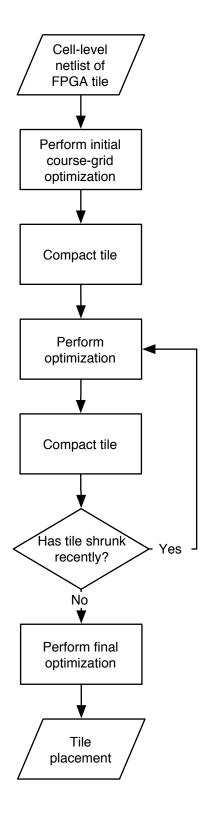

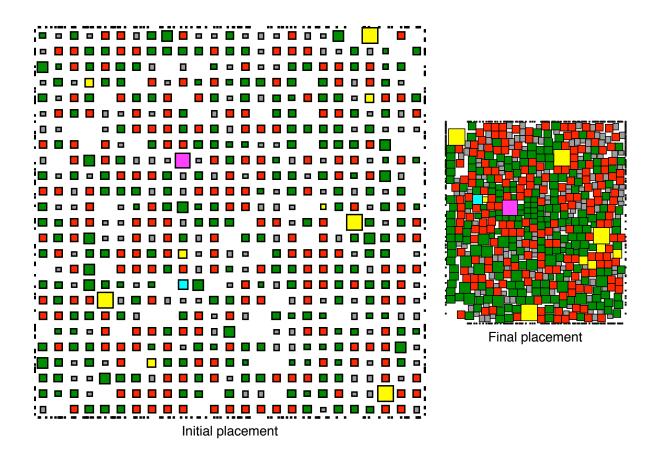

A unique feature of the placer is that it compacts the tile between placement phases as illustrated in Figure 2.15 [5]. The entire process begins with a course grid that is the size of the largest cell. Cells are forced to spread out so they have plenty of space to move around the grid. The placer performs an optimization phase to obtain good relative positions for the cells. Then the first compaction phase removes as much empty space as possible by shrinking the tile. After compaction, a new optimization phase reduces the wirelength and strives to move the blocks off the tile edges. Afterwards another compaction phase tries to reduce the area further. These phases alternate until the tile has not shrunk in several iterations. A final optimization phase is performed without biasing cell moves that help to compact the tile. An example of initial and final placements is shown in Figure 2.16.

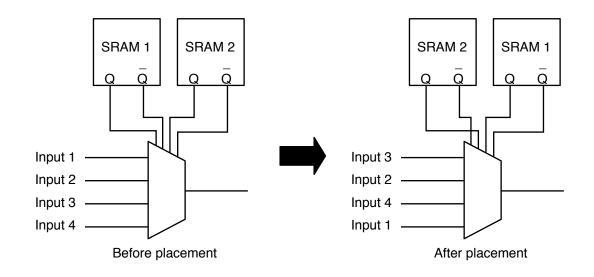

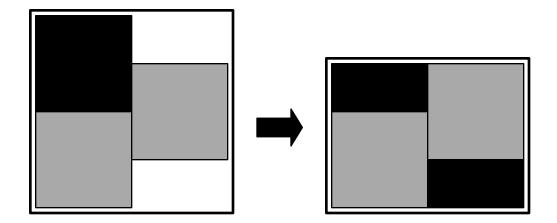

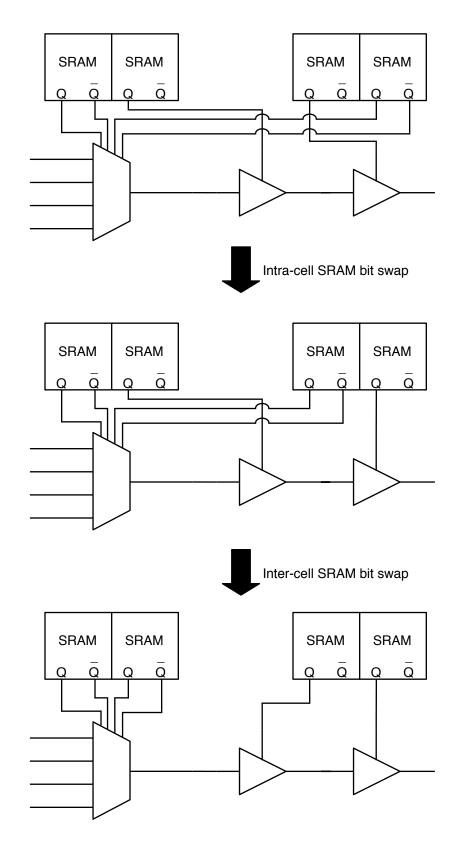

Another unique feature of the placer is its ability to make FPGA specific optimizations. The inputs and outputs of the cells are called pins. Many of the connections to these pins can be swapped because the pins are logically equivalent [27]. In other words, the circuit would still perform the same function whether the pin connections are swapped or not. The benefit of swapping the pins is that it reduces wirelength. Examples of swappable pins are the input and select signals of multiplexers. Because SRAM bits connect to the select lines, the input lines can be swapped and the SRAM bits will be programmed to reflect the change. The case is similar for swapping the select lines as well as the input and select signals of LUTs. The multiplexers in this work require both regular and complemented select lines so the SRAM cells output both signals. For both cells, the two signals can be swapped by flipping the value programmed into the SRAM bit. All these pin swaps are illustrated in Figure 2.17. ASIC flows also allow connections to standard cells be swapped but our placer has more options because it allows changes in how the SRAM bits are programmed.

The logical equivalence of SRAM bits is also leveraged to minimize the wirelength

Figure 2.15: Placer algorithm

Figure 2.16: Initial and final tile placements

Figure 2.17: Placer swaps logically equivalent pins

Figure 2.18: Reweaving SRAM word and bit lines

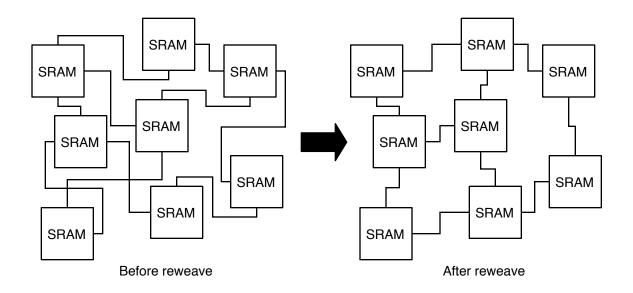

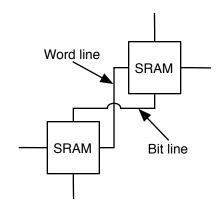

of their programming lines. A word line selects a row of SRAM bits for writing and a series of bit lines drive individual values into each SRAM bit. These lines may get tangled when the placer moves cells. To untangle the wires, the placer rips up and rewires the programming lines after each anneal [27]. This process is called reweaving and is illustrated in Figure 2.18.

# 2.4.3 Router

The router is the last stage of GILES. It routes the connections between the cells and to the tile ports. The input is the tile placement and the number of metal layers used for routing. The output is a description of the routing. It is an implementation of the maze router algorithm [28]. A unique feature of the router is that when it fails to route a design, it adds space in congested regions and starts again [29].

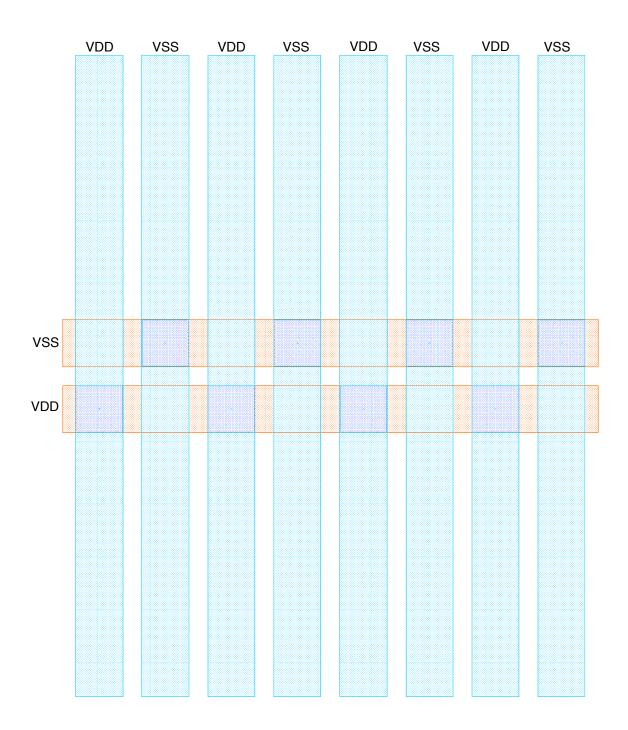

The router uses a grid on which it draws wires. The grid is sized so that two minimum size vias can be placed in adjacent grid squares and meet minimum spacing design rules. When the router completes, all wires in the design are connected, including power, ground, and clock networks. However, there are no special structures such as a clock tree or power grid. Therefore, they must be implemented separately on metal layers not used for routing. The router is not capable of avoiding existing metal traces so the layers used for routing cannot be used by the power grid, clock tree, or the cells.

# 2.4.4 Previous Results

Padalia et al. [5] compared GILES to two commercial FPGAs: the Xilinx Virtex-E and the Altera Apex 20K400E. The comparisons were very approximate because GILES is limited to VPR architectures and cannot reproduce the features of these commercial chips exactly. Using a total of eight metal layers, the FPGA tiles created by GILES were 47% and 97% larger than the tiles of the Virtex-E and Apex 20K400E, respectively. This is quite impressive considering the ease in which the tiles are generated. Instead of performing the layout of the entire tile, only the set of cells used by GILES is required.

# Chapter 3

# Improvements to the GILES Automated FPGA Layout System

The goal of the GILES automated layout project is to significantly reduce the development time of FPGAs while maintaining competitive area, speed, and power compared to custom designs. Competitive area results are critically important since any increase in silicon area increases production costs and detracts from cost benefits resulting from reduced development time. Smaller, compact designs also have side benefits affecting speed and power by reducing the length of connecting wires. The previous results mentioned in Section 2.4.4 compare the area of FPGA tiles made with GILES to commercial FPGAs. The results show GILES creates FPGA tiles that are 47% to 97% larger than commercial FPGAs [5]. The primary goal of this chapter is to improve these results.

To accomplish this goal, this chapter explores the set of cells that make up the netlist of the FPGA tile. These cells are the basic building blocks used by the GILES placer and router. The size of these cells have an impact on the density of the layout and the effectiveness of the placer. The original version of GILES used arbitrary groupings of transistors to form these cells. This chapter revisits these groupings to determine how they affect the area results and then chooses the best groupings to minimize the area. To obtain accurate area results for comparison, the layout of each unique cell in the tile is required. New cells are required for different groupings and different FPGA architectures. However, the only information needed from the layout is the size and pin positions of each cell. So, to avoid manual layout, the GILES netlist generator estimates the size of each cell based on its transistor implementation and assigns pin positions such that they are spread out over the cell. The accuracy of the area results are dependent on the accurate modelling of the cell sizes. Therefore, before improving the results of GILES, Section 3.1 devises a new area model for estimating cell area with better accuracy. Then Section 3.2 examines the area results of different groupings of transistors into cells. Section 3.3 compares the area of tiles generated with GILES to the layout area of a commercial FPGA.

# 3.1 A New Area Model for Cells

GILES is capable of automatically generating the layout of any FPGA that can be described using the VPR architecture description. This implies that the netlist of the FPGA tile will be different depending on the architecture. Some cells are needed for some architectures but not for others. Examples of cells are inverters, buffers, SRAMs, multiplexers, flip-flops, and pass transistors. All but the SRAMs and flip-flops have transistors that are sized based on the architecture description file. Instead of manually creating the layout of each cell for numerous architectures, GILES contains an area model for estimating the layout area of a cell based on the number and size of transistors. This section measures the accuracy of the area model used in the previous version of GILES. Then a new area model is derived that achieves better results.

#### 3.1.1 Previous Area Model and Measurement of Accuracy

We measure cell area in grid squares corresponding to the granularity of the placement and routing grid. The grid size is set to 0.66  $\mu$ m by 0.66  $\mu$ m, which is the minimum distance allowed between metal vias in 0.18  $\mu$ m technology. The previous GILES area model [27] uses the following equation to estimate the area in grid squares of each cell:

$$cellArea(gridSquares) = max(2.25 \times \sum_{i \in xtors} driveStrength_i, 3 \times numPins)$$

(3.1)

This equation sums the drive strengths of the transistors in a cell to obtain a rough estimate of the number of minimum-width transistors that occupy the same area. It assumes that a 1x drive strength transistor is equal to one minimum-width transistor. Therefore, a transistor with 2x drive strength is equivalent in area to two minimum size transistors. The number of minimum-width transistors is multiplied by 2.25 for the number of grid squares required to layout a minimum-width transistor in 0.18  $\mu$ m technology. For some cells, this area is not enough to fit all the pins and routing needed for external connections. In these cases, the area is set to be three times the number of pins in the cell.

The GILES placer obtains the best results when the cells are as close to square as possible [27]. Therefore, the width of each cell is determined by taking the square root of its area. The width is rounded up to the nearest integer since cells cannot occupy a fraction of a grid square. The cell height is determined by dividing the cell area by the rounded width. The cell height is rounded up as well. The final cell area is equal to the product of the rounded width and height.

To determine the accuracy of the previous model, we examined the layouts of sixteen cells of various types with sizes ranging from 20 to 418 grid squares. These cells were laid out using a 0.18  $\mu$ m technology and Micro Magic MAX. The layout area is compared to the estimated area obtained from the model in Table 3.1. The area model of Equation 3.1 underestimates the area of all the cells except the 15x buffer cell. Overall, the previous

model has an average absolute error of 43.7%.

To see how this error impacts the use of GILES and its comparisons, we examined the same two tiles as Padalia et al. [5]. These tiles have similar features to the tiles in the Xilinx Virtex-E and the Altera Apex 20K400E. The differences between our tiles and the commercial FPGA tiles are a result of the limitations of the VPR architecture description language. We ran GILES with the actual cell layouts and the modelled cell layouts for both tiles. As shown in Table 3.2, when using the modelled cell layouts instead of the actual cell layouts, GILES underestimates the tile areas by 33.7% and 7.5%. The error for the tile areas is smaller than for individual cell areas because the router adds space between the cells to ease routing congestion.

#### 3.1.2 New Area Model

To improve these results, we derive a new area model based on the area model by Betz et al. [4]. The area of each transistor, i, is measured in terms of the number of minimumwidth transistors that occupy the same area using the following equation:

$$area_i(minWidthTransistors) = 0.5 + \frac{driveStrength_i}{2}$$

(3.2)

This equation is the same as Equation 2.1 except the *minWidthDriveStrength* term in the denominator is missing. GILES specifies all drive strengths relative to the drive strength of a minimum-width transistor so this term is not needed.

Cell areas are estimated by summing the result of Equation 3.2 for each transistor in the cell:

$$cellArea(minWidthTransistors) = \sum_{i \in xtors} area_i(minWidthTransistors)$$

(3.3)

In this equation, the cell area is still represented in terms of the number of minimum width transistors that occupy the same area. To convert the area to the number of grid squares used by the cell, we multiply by the number of grid squares required to lay out

| Cell                   | Layout area    | Estimated area | Error  |

|------------------------|----------------|----------------|--------|

|                        | (grid squares) | (grid squares) |        |

| 1x inverter            | 25             | 12             | -52.0% |

| 2x inverter            | 30             | 16             | -46.7% |

| 4x inverter            | 36             | 30             | -16.7% |

| 4x buffer              | 56             | 36             | -35.7% |

| 5x buffer              | 90             | 64             | -28.9% |

| 15x buffer             | 121            | 144            | +19.0% |

| SRAM                   | 49             | 20             | -59.2% |

| 2-input multiplexer    | 25             | 20             | -20.0% |

| 12-input multiplexer   | 156            | 72             | -53.8% |

| 24-input multiplexer   | 306            | 110            | -64.1% |

| 32-input multiplexer   | 342            | 144            | -57.9% |

| 36-input multiplexer   | 418            | 169            | -59.6% |

| LUT                    | 196            | 81             | -58.7% |

| Flip-flop              | 90             | 42             | -53.3% |

| 3x pass transistor     | 20             | 12             | -40.0% |

| 8x pass transistor     | 30             | 20             | -33.3% |

| Average absolute error |                |                | 43.7%  |

Table 3.1: Accuracy of old area model

| Approximate architecture | Tile area (         | Error                 |        |

|--------------------------|---------------------|-----------------------|--------|

|                          | Actual cell layouts | Modelled cell layouts |        |

| Xilinx Virtex-E          | 52,268              | 34,640                | -33.7% |

| Altera Apex 20K400E      | 124,161             | 114,873               | -7.5%  |

Table 3.2: Accuracy of tile area with old area model

a minimum-width transistor:

$$cellArea(gridSquares) = 3.3 \times cellArea(minWidthTransistors)$$

(3.4)

The number of grid squares required to lay out a minimum-width transistor has been changed from 2.25 in the previous area model to 3.3 to include the space needed *between* transistors.

Using Equation 3.4, we determined that the areas of SRAMs and multiplexers are underestimated, which can be attributed to their relatively complex layout. In comparison, inverters, buffers, flip-flops, and pass transistors are more simple structures and/or take greater advantage of diffusion region sharing. Accordingly, a complexity factor is added to Equation 3.4 to increase the cell area when it is more difficult to create a compact layout:

$$cellArea(gridSquares) = complexity \times 3.3 \times cellArea(minWidthTransistors)$$

(3.5)

The complexity factor is calibrated to 1.455 for SRAMs and multiplexers and to 1.0 for the remaining cells to closely estimate the area of the test cells. At the end of this section, the value of this factor is verified against a new set of cells. An important difference between the new and old area models is that the previous area model of Equation 3.1 depends on the number of pins in the cell. The new area model of Equation 3.5 does not have this dependency because the areas of our actual cell layouts are not pin-limited.

i.

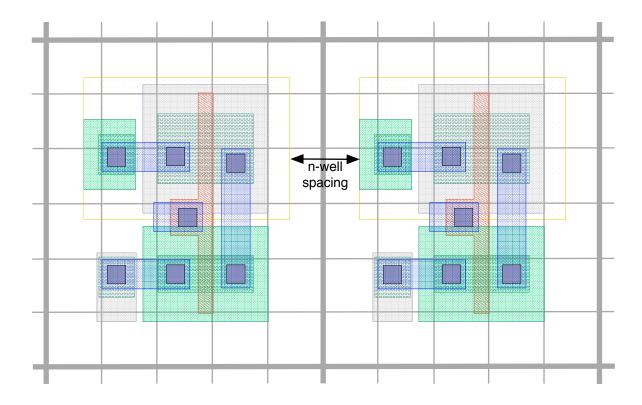

Figure 3.1: Required n-well spacing between inverter cells

The width and height of each cell are calculated as before to obtain cells that are approximately square. However, the width and height are rounded to the nearest integer instead of rounding up since two grid squares are now added to both the width and the height to create a one grid square border around each cell. This models the n-well, n+, and p+ regions that extend beyond the transistors as well as the design rules for the space required between these regions. Figure 3.1 shows the space needed between two inverter cells. The space is designed so that any side of one cell can be abutted against any side of another cell without violating design rules. The final area estimates include this border as do the actual areas obtained from the layouts. This is one reason why the previous area model underestimated the cell areas.

To measure the accuracy of the new area model, the actual layout area of each cell is compared to the area estimated by Equation 3.5. The percent error for each cell and the average absolute error for all cells is shown in Table 3.3. The average absolute error has been reduced to 5.8% from 43.7% with the previous area model. The worst area estimate of any cell is for the largest buffer with an error of +28.9%. Its area is overestimated due to extensive use of diffusion region sharing in the layout.

To see how the new area model impacts the area of the tile, we ran GILES with the new area model on the approximate Virtex-E and Apex 20K400E from Table 3.2. The results using the new area model are shown in Table 3.4. Now the tile areas are 3.2% and 8.0% larger than when using the actual cell layouts. These results are more accurate than when using the previous area model and they also show that tile areas are likely to be slightly pessimistic when using the new area model.

The cells in Table 3.3 were used to formulate the new area model so it is not surprising that it performs well for these cells. To verify the area model accuracy in general, we examine a new set of cells. Chapter 4 discusses using GILES to create an FPGA. To accomplish this, new cells were laid out in Cadence's Virtuoso Layout Editor [30] using a 0.18  $\mu$ m technology library that has small differences compared to the 0.18  $\mu$ m library used with Micro Magic MAX. In addition, new types of cells were required. The layout area of each cell is compared with the estimated area using the area model of Equation 3.5 in Table 3.5. The average absolute error of these fifteen new cells is 16.4%.

The area model was not tuned to these cells yet it still performs reasonably well. Many of the cell areas are overestimated but this is to be expected since when these cells were laid out, we had more experience and were able to create more compact layouts. The worst estimate is the 4x buffer and pass transistor grouping with an error of +52.4%. The layout of this cell makes extensive use of diffusion region sharing to compact the layout. It may be possible to use a complexity factor of less than one to estimate the area of cells with high levels of optimization; however, it is difficult to predict which cells will use these optimizations.

| Cell                   | Layout area    | Estimated area | Error  |

|------------------------|----------------|----------------|--------|

|                        | (grid squares) | (grid squares) |        |

| 1x inverter            | 25             | 25             | 0.0%   |

| 2x inverter            | 30             | 30             | 0.0%   |

| 4x inverter            | 36             | 42             | +16.7% |

| 4x buffer              | 56             | 56             | 0.0%   |

| 5x buffer              | 90             | 90             | 0.0%   |

| 15x buffer             | 121            | 156            | +28.9% |

| SRAM                   | 49             | 49             | 0.0%   |

| 2-input multiplexer    | 25             | 25             | 0.0%   |

| 12-input multiplexer   | 156            | 156            | 0.0%   |

| 24-input multiplexer   | 306            | 289            | -5.6%  |

| 32-input multiplexer   | 342            | 380            | +11.1% |

| 36-input multiplexer   | 418            | 420            | +0.5%  |

| LUT                    | 196            | 196            | 0.0%   |

| Flip-flop              | 90             | 81             | -10.0% |

| 3x pass transistor     | 20             | 20             | 0.0%   |

| 8x pass transistor     | 30             | 36             | +20.0% |

| Average absolute error |                |                | 5.8%   |

# Table 3.3: Accuracy of new area model

| Approximate architecture | Tile area (         | Error                 |       |

|--------------------------|---------------------|-----------------------|-------|

|                          | Actual cell layouts | Modelled cell layouts |       |

| Xilinx Virtex-E          | 52,268              | 53,957                | +3.2% |

| Altera Apex 20K400E      | 124,161             | 134,050               | +8.0% |

# Table 3.4: Accuracy of tile area with new area model

Table 3.5: Verification of new area model

| Cell                                   | Layout area    | Estimated area | Error  |

|----------------------------------------|----------------|----------------|--------|

|                                        | (grid squares) | (grid squares) |        |

| 1x inverter (with level restorer)      | 35             | 30             | -14.3% |

| 2x inverter                            | 30             | 30             | 0.0%   |

| 4x inverter                            | 36             | 42             | +16.7% |

| 4x buffer                              | 42             | 56             | +33.3% |

| SRAM $(4x4 \text{ grouping})$          | 480            | 462            | -3.75% |

| 2-input multiplexer                    | 20             | 25             | +25.0% |

| 11-input multiplexer                   | 110            | 144            | +30.9% |

| 12-input multiplexer                   | 120            | 156            | +30.0% |

| 20-input multiplexer                   | 252            | 240            | -4.8%  |

| LUT                                    | 198            | 196            | -1.0%  |

| Flip-flop                              | 108            | 90             | -16.7% |

| Flip-flop with enable                  | 126            | 110            | -12.7% |

| 4x buffer and pass transistor grouping | 42             | 64             | +52.4% |

| Level restorer                         | 30             | 30             | 0.0%   |

| AND gate                               | 40             | 42             | +5.0%  |

| Average absolute error                 |                |                | 16.4%  |

# 3.2 Grouping Transistors into Cells

Now that GILES has a more accurate area model, we focus on the primary goal of this chapter: to reduce the area of FPGA tiles created with our automatic layout system. One of the key steps in the GILES system is the choice of which groups of transistors should form the cells for the placement and compaction stage. In the original GILES [5], these are set somewhat arbitrarily to be inverters, buffers, SRAMs, multiplexers, LUTs, flip-flops, and pass transistors. There are several tradeoffs involved with these choices that could markedly affect the quality of results. These tradeoffs are discussed here.

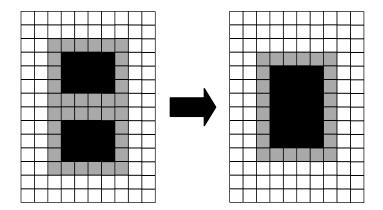

In general, using smaller cells (in the extreme, each cell would be a single transistor) gives the placement and compaction stage more freedom to move individual cells, providing opportunity to produce placements with less wirelength and less "whitespace" (space that does not contain cells). However, the layout of each cell has an empty border around it, as shown in Figure 3.1, to ensure that design rules are not violated when cells are placed next to each other. If transistors are grouped into larger cells, the amount of border space needed is reduced.

For example, on the left of Figure 3.2, there are two cells that contain 12 grid squares of transistors each (shown in black) but occupy a total of 30 grid squares each due to the border (shown in grey). Placed side-by-side as neighbours, they occupy 60 grid squares, but their transistors only occupy 24 grid squares so 60% of the area is wasted. If the same transistors are grouped into a new cell, shown on the left, the transistors occupy the same 24 grid squares but no longer need the space between them. The layout designer can intelligently remove this space because he or she knows the implementation of the cells. The border is still needed around the new cell so the total cell area is 48 grid squares, a 20% savings from the total of 60 grid squares for the two separate cells. Smaller cells have a greater perimeter to area ratio so they have the most to gain from grouping.

To determine an estimate of the largest possible gain from eliminating borders, we used the new area model to estimate the area of the cells with and without the border.

Figure 3.2: Grouping cells saves border area

We ran GILES using cells with the border and again without the border. Then we calculated the change in tile area between the two runs. We performed this procedure for ten FPGA architectures and obtained the geometric average of the area savings for each architecture.

The parameters of the ten FPGA architectures are summarized in Table 3.6. These are the same architectures used by Padalia et al. [5]. The main difference between these ten architectures is that each one has a different cluster size ranging from one to ten. The number of routing tracks and the connection block flexibilities,  $F_c$ , for input and output are set to optimize routability using minimal area for each architecture. All the architectures use four-input LUTs and a switch block flexibility,  $F_s$ , of 3. In each architecture all the routing tracks are length four wires and half of the routing switches are buffered. The GILES inter-cell router uses all but three of the available metal layers for routing. The three reserved layers are used for intra-cell connections and global distribution networks for power and clocking.

We ran GILES with and without the space around the cells for these ten FPGA architectures. The tile area for each case is shown in Table 3.7. For each architecture, we calculated the ratio of the tile area without cell borders to the tile area with cell borders. The geometric average of the ratios over the ten architectures is 0.659, which means that

| # of LUTs per cluster | # of tracks (W) | $F_{c,input}$ | $F_{c,output}$ | Metal layers |

|-----------------------|-----------------|---------------|----------------|--------------|

| 1                     | 32              | 0.56W         | 1.00W          | 7            |

| 2                     | 56              | 0.44W         | 0.50W          | 8            |

| 3                     | 80              | 0.30W         | 0.33W          | 8            |

| 4                     | 96              | 0.23W         | 0.25W          | 8            |

| 5                     | 120             | 0.19W         | 0.20W          | 8            |

| 6                     | 144             | 0.15W         | 0.17W          | 8            |

| 7                     | 160             | 0.13W         | 0.14W          | 8            |

| 8                     | 176             | 0.11W         | 0.13W          | 8            |

| 9                     | 192             | 0.10W         | 0.11W          | 8            |

| 10                    | 200             | 0.10W         | 0.10W          | 8            |

Table 3.6: Parameters of ten experimental architectures

removing the border reduces the tile area of the ten architectures by an average of 34.1%. This gives us an approximate upper bound on the gain we can achieve by merging cells and eliminating the empty space between them.

Another advantage of merging cells is that the connections between them no longer have to be routed. This eases the congestion faced by the inter-cell router. The human designer will connect the cells internally in the new cell. The designer may also be able to compact the design even further by using techniques such as diffusion region sharing.

One disadvantage of combining cells is that the separate cells may still be required in the tile. For example, a buffered switch is made up of a buffer and a pass transistor switch. The buffered switch could be implemented using a single cell or two cells that make up its components. In either case, the amount of manual layout effort is similar. However, if a single cell is used for the buffered switch and the buffers and pass transistors are used elsewhere in the FPGA then all three cells will have to be laid out. This increases

| Architecture      | Tile area         | Ratio                |       |

|-------------------|-------------------|----------------------|-------|

|                   | With cell borders | Without cell borders |       |

| 1                 | 26350             | 15812                | 0.600 |

| 2                 | 50007             | 27692                | 0.554 |

| 3                 | 71273             | 43870                | 0.616 |

| 4                 | 96084             | 56862                | 0.592 |

| 5                 | 126374            | 90846                | 0.719 |

| 6                 | 156832            | 97175                | 0.620 |

| 7                 | 180994            | 126324               | 0.698 |

| 8                 | 203320            | 148500               | 0.730 |

| 9                 | 225094            | 166690               | 0.741 |

| 10                | 252324            | 190569               | 0.755 |

| Geometric average |                   |                      | 0.659 |

Table 3.7: Effect of cell border on tile area

Figure 3.3: Smaller cells result in less whitespace

the number of cells and the total amount of manual layout effort.

A second disadvantage of making larger cells is that there is a point where the cells are made so large that the placer/compacter has limited freedom to place the cells. A simple example of this is shown in Figure 3.3. The placement on the left cannot be compacted any further; however, if the black cell is divided into two smaller cells then the whitespace is filled in and the placement area is reduced.

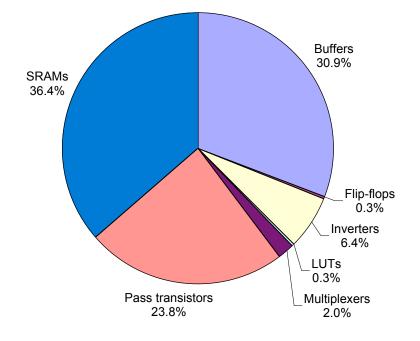

The potential for area savings is greatest when combining cells that are used more frequently. Therefore, we analyzed the distribution of cell types for the architectures in Table 3.6. The number of cells of each type in a single tile is summarized in Table 3.8. The frequency of each cell type increases linearly with the total number of cells in the tile so the percent of each cell type out of the total number of cells is approximately constant across the ten architectures. The average of this percent for each cell type across the ten architectures is shown in Figure 3.4. The number of flip-flops and LUTs each account for only 0.3% of the total number of cells in each tile so merging these cells will not save much area compared to merging SRAMs, which account for 36% of the cells. Buffers and pass transistors are also common since they form the routing fabric that occupies a larger percentage of the total area than the logic elements.

Because SRAMs, buffers, and pass transistors are by far the most common cells,

| Architecture     | 1   | 2   | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10   |

|------------------|-----|-----|------|------|------|------|------|------|------|------|

| Buffers          | 156 | 291 | 403  | 472  | 591  | 686  | 757  | 822  | 910  | 965  |

| Flip-flops       | 1   | 2   | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10   |

| Inverters        | 30  | 52  | 74   | 96   | 118  | 140  | 162  | 184  | 206  | 228  |

| LUTs             | 1   | 2   | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10   |

| Multiplexers     | 9   | 16  | 23   | 30   | 37   | 44   | 51   | 58   | 65   | 72   |

| Pass transistors | 120 | 210 | 301  | 360  | 450  | 540  | 601  | 660  | 726  | 750  |

| SRAMs            | 169 | 298 | 440  | 542  | 695  | 832  | 940  | 1046 | 1159 | 1230 |

| Total            | 486 | 871 | 1247 | 1508 | 1901 | 2254 | 2525 | 2786 | 3084 | 3265 |

Table 3.8: Distribution of cell types

Figure 3.4: Average frequency of cell usage