## Technology Mapping and Architecture of Heterogeneous Field-Programmable Gate Arrays

by

## Jianshe He

A thesis submitted in conformity with the requirements for the degree of Master of Applied Science in the Dept. of Electrical and Computer Engineering University of Toronto, Toronto Ontario, Canada

©Jianshe He 1993

### Abstract

As Field-Programmable Gate Arrays (FPGAs) become more accepted and integral to the digital design process, there will be a strong drive to produce faster and higher-density devices. One architectural dimension that needs to be explored for its speed and density benefits is that of *heterogenous* FPGAs which employ more than one basic kind of logic block instead of the common homogeneous FPGA with identical logic blocks. There are two architectural reasons to believe that an FPGA with a selection of heterogenous blocks will provide superior speed and density:

1. Different logic may be more efficiently implemented with different kinds of blocks.

2. Previous studies have shown that coarse grain blocks exhibit superior speed to

fine grain blocks, yet the smaller blocks have better density. A mixture of the two

may provide superior speed-area tradeoff.

This thesis makes two contributions in the area of heterogeneous FPGAs. First it presents a technology mapping algorithm for heterogeneous FPGAs with two different sizes of lookup table (LUT) logic block. Synthesis for this type of FPGA is more difficult than for homogeneous FPGAs because the cost function is not a linear count of the number of LUTs used. To solve this problem a general optimization approach is proposed and applied at the tree-level and across multiple trees. The latter algorithm is shown to be optimal. Experimental results show that this approach is superior to synthesizing heterogeneous FPGAs from a post-process of a homogeneous mapper.

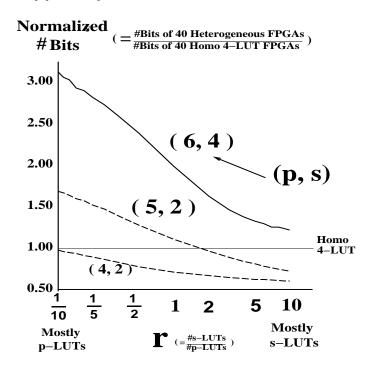

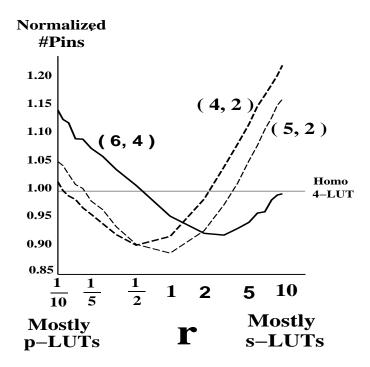

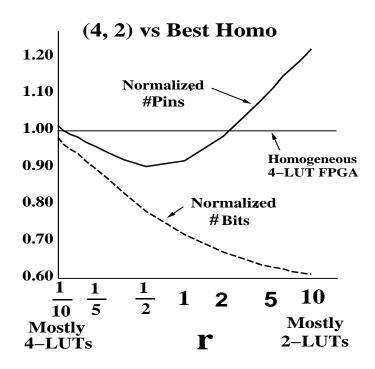

Secondly, the thesis also presents an architectural investigation into the area-efficiency of heterogeneous FPGAs. Experimental results on a set of benchmark circuits indicate that several heterogeneous architectures achieve significant reduction in the number of programming bits and logic block pins compared to the best homogeneous FPGA: a 4-input lookup table (4-LUT) FPGA. Furthermore, a 6-LUT/4-LUT combination will likely exhibit better performance with nearly equivalent area to a homogeneous 4-LUT FPGA.

## Acknowledgements

First and foremost, I would like to thank my supervisor, Professor Jonathan Rose, for his guidance and support. His patience, wisdom, and advice have provided me with a continuous source of inspiration and encouragement. I also thank Jonathan for introducing me to the exciting FPGA world and later to the heterogeneous FPGA area.

I would like to thank Dr. Bob Francis, Kevin Chung, Qing Zheng, Qiang Wang, and Keith Farkas for many helpful discussions. Many thanks to the Ph.D and Master's students and staff of the Computer and Electronics Groups for their cooperation.

Financial assistance from Information Technology Research Center is gratefully acknowledged.

Last but not the least, I thank my wife, Yingchun, for her continuous understanding, encouragement, and especially wholehearted support in bringing up our son, George, while she was studying.

# Contents

| 1        | Inti | roduction                                                | 1         |

|----------|------|----------------------------------------------------------|-----------|

|          | 1.1  | Field-Programmable Gate Arrays                           | 1         |

|          | 1.2  | Thesis Motivation                                        | 2         |

|          | 1.3  | Thesis Organization                                      | 4         |

| <b>2</b> | Bac  | ckground and Previous Work                               | 6         |

|          | 2.1  | LUT and LUT-Based FPGAs                                  | 6         |

|          | 2.2  | Technology Mapping for LUT-Based FPGAs                   | 7         |

|          |      | 2.2.1 The Chortle Technology Mapper                      | 9         |

|          | 2.3  | Previous Work on Heterogeneous FPGAs                     | 11        |

|          |      | 2.3.1 Heterogeneous NAND Gates                           | 11        |

|          |      | 2.3.2 Investigation of LUT-based Heterogeneous FPGAs     | 13        |

|          | 2.4  | Commercial FPGAs with Heterogeneity                      | 16        |

|          |      |                                                          | 16        |

|          |      | 2.4.2 The Architecture of AT & T ORCA FPGAs              | 17        |

|          |      | 2.4.3 The Altera's LAB Architecture                      | 18        |

|          |      | 2.4.4 Actel's Act2 FPGAs                                 | 20        |

|          | 2.5  | Summary                                                  | 21        |

| 3        | Het  | terogeneous Technology Mapping                           | <b>22</b> |

|          | 3.1  | Notation and Problem Definition                          | 23        |

|          | 3.2  | General Approach and Overall Flow                        | 24        |

|          | 3.3  | Mapping on a Single Tree                                 | 25        |

|          |      |                                                          | 25        |

|          |      |                                                          | 27        |

|          |      | 3.3.3 Forming a Tree                                     | 29        |

|          | 3.4  | Multi-tree Optimization                                  | 30        |

|          |      |                                                          | 30        |

|          |      | 3.4.2 Proof of Optimality of The Multi-tree Optimization | 32        |

|          |      | - • -                                                    | 37        |

|          | 3.5  |                                                          | 38        |

|          | 3.6  | Summary                                                  | 13        |

| 4  | Arc   | hitectural Investigation of Heterogeneous FPGAs                 | 46 |

|----|-------|-----------------------------------------------------------------|----|

|    | 4.1   | Architectural Questions                                         | 46 |

|    | 4.2   | Experimental Procedures                                         | 47 |

|    | 4.3   | Experimental Results                                            | 49 |

|    | 4.4   | Summary                                                         | 55 |

| 5  | 5.1   | Conclusions and Future Work Conclusions Future Work Conclusions |    |

| Bi | bliog | graphy                                                          | 59 |

## Chapter 1

## Introduction

### **1.1** Field-Programmable Gate Arrays

The Field-Programmable Gate Array(FPGA) is a new implementation medium for Application Specific Integrated Circuits (ASICs). It provides the user with large scale integration and user programmability. An FPGA consists of a general array of uncommitted logic blocks that are interconnected by programmable routing switches. The user can program and sometimes reprogram an FPGA into different devices by turning on or turning off these switches in the "field". The user-programmability of the FPGA results in a reduction of the turn-around time from months to minutes and cuts the manufacturing costs of a prototype of ASIC by a factor of a thousand over traditional fabrication techniques.

While the FPGA offers significant advantages over traditional ASIC fabrication technologies, such as Mask-Programmable Gate Arrays (MPGAs), it has lower density and slower speed due to the technology used in the programmable switches. In commercial architectures this programming technology is one of pass transistors driven by static RAM, anti-fuses, or floating gate transistors [Brow92]. In all cases these programming technologies have large resistance and capacitance which require much larger area and cause more delay than the metal wires used in an MPGA to make connections. As a result, an FPGA has lower logic density and is slower than an MPGA. The effect of these two drawbacks can be reduced by careful choice of the FPGA *architecture*.

### **1.2** Thesis Motivation

Most FPGAs consist of an array of identical logic blocks [Cart86] [Hsie90] [ElGa89] [Ahre90] [Wong89] [Wils92] [Algo89], or logic blocks that have very similar levels of functionality. Such an FPGA is termed *homogeneous*. Previous studies on logic block architecture [Rose90] [Koul92] have concluded that while 4-input lookup tables (4-LUTs) make efficient use of area, more coarse-grained blocks such as 5-LUTs, 6-LUTs and 7-LUTs are superior in terms of system speed [Koul91] [Sing91] [Sing92]. These results suggest that a mixture of different size LUTs (for example 4-LUTs and 6-LUTs) may provide a better tradeoff between speed and density.

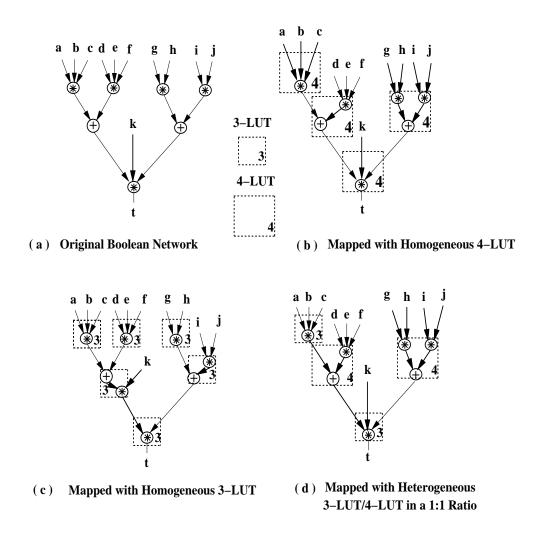

Furthermore, all such studies have considered only the homogeneous case; it is possible that a heterogeneous mixture of logic blocks may provide superior area-efficiency (which relates to logic density) because some parts of logic may simply be more efficiently implemented with one particular type of logic block than another. For example, consider the boolean network pictured in Figure 1.1a. Figure 1.1b is a mapping of that network using 4-LUTs and Figure 1.1c is a mapping of that network using 3-LUTs. As shown in Table 1.1, the 4-LUT solution uses one-third more lookup table bits (64 vs 48) but 20% fewer pins than the 3-LUT solution. Note that a single 3-LUT has 8 bits and 4 pins and a single 4-LUT uses 16 bits and 5 pins. Pin counts and bit counts are common metrics of area cost in a LUT-based FPGA. We will discuss these metrics in more detail in Chapter 4.

Now suppose that the network is mapped into a heterogeneous FPGA that contains 3-LUTs and 4-LUTs in equal numbers, as illustrated in Figure 1.1d. This circuit uses exactly two 3-LUTs and two 4-LUTs and hence requires only 48 bits and 18 pins. This heterogeneous FPGA requires 25% fewer bits and 10% fewer pins than the 4-LUT homogenous FPGA implementation. It also has the same number of bits and 25% fewer pins than the 3-LUT homogenous FPGA to implement this example. While this is a "cooked" example, it demonstrates that a heterogeneous mixture of logic blocks *may* exhibit superior area-efficiency. In practice, this situation often occurs.

One difficulty with heterogeneous FPGAs is that there are no CAD tools aimed at solving the heterogeneous mapping problem. Although many technology mappers have been developed for homogeneous architectures [Fran90] [Fran91] [Fran91b] [Murg90] [Murg91a] [Murg91b], [Abou90] [Filo91] [Karp91] [Woo91] [Chen92] [Cong92] [Sawk92], to our knowledge there is no prior re-

Figure 1.1: An illustration of homogeneous and heterogeneous mappings

|               | LUT types   | #LUTs | #Bits | #Pins |

|---------------|-------------|-------|-------|-------|

| Homogeneous   | only 3-LUT  | 6     | 48    | 24    |

|               | only 4-LUT  | 4     | 64    | 20    |

| Heterogeneous | 3-LUT/4-LUT | 2/2   | 48    | 18    |

Table 1.1: Comparison of Hetero. vs. Homo. FPGAs for Circuit in Figure 1.1

search on the heterogeneous problem.

It should be noted that Xilinx's 4000 series FPGA does use two sizes of lookup table. However, in the Xilinx 4000, two 4-LUTs are *hardwired* to a 3-LUT and so are tightly linked. The notion of heterogeneity used in this thesis is that the different logic blocks must be completely independent in the routing.

The goal of this thesis is two-fold:

1. Develop a technology mapping algorithm for heterogeneous FPGAs and

implement it.

2. Use this new CAD tool to investigate the advantages of heterogeneous FPGAs

using an empirical approach: implementing benchmark circuits in a variety of

heterogeneous FPGAs and measuring their area-efficiency.

### 1.3 Thesis Organization

This thesis is organized as follows: Chapter 2 provides the necessary background and discusses previous related work. Chapter 3 describes a new technology mapping algorithm for heterogeneous FPGAs and compares the algorithm's effectiveness with a modified homogeneous mapper. Chapter 4 presents the experimental method used to evaluate a set of heterogeneous architectures and gives the experimental results and conclusions. The final chapter contains the conclusions of the thesis work and suggestions for future work.

## Chapter 2

## **Background and Previous Work**

This chapter presents the background and previous related work on heterogeneous FPGAs. This includes lookup table (LUT)-based FPGA technology mapping and previous work on heterogeneous FPGA architecture. Finally, the architectures of commercial FPGAs with some heterogeneity are briefly described.

## 2.1 LUT and LUT-Based FPGAs

The logic block of an FPGA is used to implement combinational and sequential logic. Logic blocks can be designed in many different ways. Some FPGA logic blocks are as simple as 2-input NAND gates, while other blocks have more complex structures, such as lookup tables, multiplexers, or very wide-input AND-OR structures.

Previous studies have shown that lookup tables are a good choice due to their high functionality [Sing91] and now LUT-based FPGAs are the most common type of commercial FPGAs [Hsie90] [Wils92] [Brit93]. A K-input lookup table (K-LUT) is a digital memory with K address lines and a one-bit output. This memory contains  $2^{K}$  bits and is capable of implementing any boolean function of K variables. A lookup table of K inputs can implement  $2^{2^{K}}$  different boolean functions.

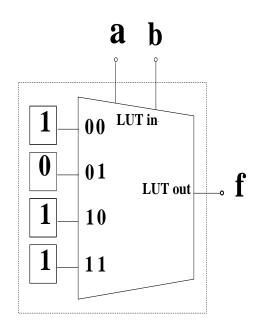

A simple example of a 2-input lookup table implementing a function  $f = a + \overline{b}$  is shown in Figure 2.1, where the LUT is described in terms of a

multiplexer. In the lookup table, there are two address lines (a and b) and  $4(2^2)$  memory cells. The inputs to the lookup table are the select lines of the multiplexer and the memory cells serve as the inputs to the multiplexer. If a = 0 and b = 1, for example, then the memory cell corresponding to select line **01** will be connected to the output f. The contents of the memory cells are calculated from the evaluation of  $f = a + \overline{b}$  for all the combinations of logic values of a and b.

Figure 2.1: An Illustration of 2-LUT Implementing  $f=a+\bar{b}$

## 2.2 Technology Mapping for LUT-Based FP-GAs

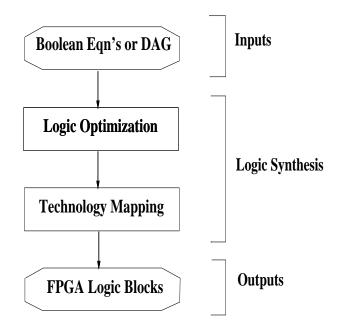

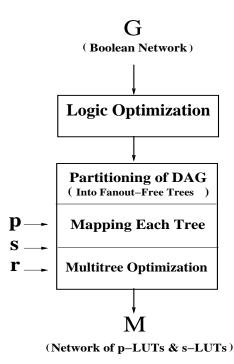

As logic design becomes more complicated, there is an increasing need for automatic synthesis of logic. Logic synthesis is the process of translating a register-transfer-level description of a design into a gate-level representation. Typically, there are two separate phases in the logic synthesis: technology-independent logic optimization and technology mapping [Bray90]. The technology-independent logic optimization step optimizes a network by algebraic and boolean simplifications such as removing redundancy and eliminating common sub-expressions to reduce the complexity of the network. As shown in Figure 2.2, the inputs to the logic synthesis or logic optimization step are boolean equations or its graph representation, the directed acyclic graph (DAG). The output of this step is an optimized network. Since this phase doesn't consider the type of block that will be used for the final circuit, it is called technology-independent logic optimization.

Figure 2.2: The Flow of Logic Synthesis

For FPGAs, the technology mapping step transforms the optimized boolean expressions into a circuit using the FPGA's particular logic blocks. The goal of technology mapping is to optimize the resulting netlist of logic blocks for area, delay, or some combination of area and delay constraints. Technology mapping for lookup table-based FPGAs is the problem of mapping a given DAG into LUTs with a fixed set of sizes. The technology mapping problem is called *homogeneous* if only one size of LUT is used in the mapping; otherwise it is called *heterogeneous*.

Many LUT technology mappers have been developed in the past few years, including Chortle [Fran90] [Fran91a] [Fran91b], MIS-pga [Murg90] [Murg91a] [Murg91b], Asyl [Abou90], Hydra [Filo901], Xmap [Karp91a], VISMAP [Woo91a], and DAG-Map [Cong92]. All of these map a boolean network into a homogeneous circuit of K-input LUTs, attempting to minimize either the total number of LUTs or the number of levels of LUTs (to improve speed). In the following section, only the Chortle technology mapper is described. A summary of other algorithms is provided in [Brow92] and [Fran92a].

#### 2.2.1 The Chortle Technology Mapper

Chortle has two versions, Chortle-crf and Chortle-d. The former is used to minimize the total number of lookup tables, while the latter minimizes the number of levels of logic blocks. Only Chortle-crf is described below.

The input to Chortle is a boolean network in the form of a DAG of only AND, OR, and NOT nodes. The DAG is first partitioned into a forest of fanout-free trees and each tree is separately mapped into a K-input lookup table circuit using dynamic programming. Each tree is traversed from its leaf nodes to its root. At each node, an optimal circuit of LUTs is constructed implementing the cone rooted at this node and extending to the leaves of the tree. To find the solution at the current node, only the immediate fanin information is important. The order of the traversal ensures that these immediate fanin circuits have been previously constructed.

At each node during the traversal, the problem solved by Chortle is how to implement the current node and its fanin LUTs by using the fewest number of LUTs possible. Chortle converts this problem into a bin-packing problem. Given the previously mapped fanin LUTs (called "boxes" in [Fran91a]) to each node, the bin-packing problem is to find the smallest number of "bins" (the set of resulting LUTs) that the boxes can be fitted into.

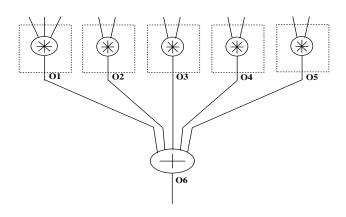

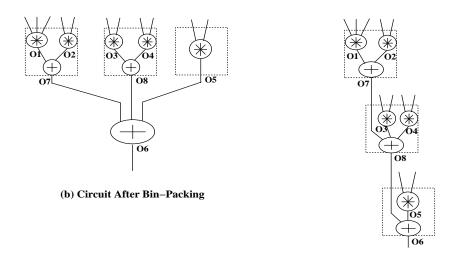

Figure 2.3 illustrates how a node is mapped. In the figure, each dashed rectangle represents a lookup table whose size is K = 5. The figure illustrates the point where all of the famins to the current node have already been mapped, but the node itself has not yet been mapped. Clearly, the LUTs in Figure 2.3a are not used to their full capacity. These LUTs can be packed into a set of "bins" to achieve higher utilization. Figure 2.3b shows such a

re-arrangement. The fanin LUTs O1 and O2 have been packed into a new LUT output at O7, and the fanin LUTs O3 and O4 are packed into the LUT output at O8. Note that the packing process is accompanied by a gate-level decomposition of the current node.

The bin-packing is a process for re-arranging the *fanin* LUTs with a decomposition of the current node. To this point the current node has not been completely implemented. In realizing the current node, Chortle makes further use of the unused inputs of the packed LUTs by placing a LUT's output into another LUT's input if possible. In figure 2.3c the node is further decomposed to connect all the packed LUTs. Output O7 is placed into the LUT that produces output O8. As few used inputs as possible are packed into the root LUT to benefit implementation of the next stage, since the root LUT of the current node will be the fanin LUT of the next stage.

[Fran92a] proves that for each input tree, Chortle generates an optimal tree implementation provided that the value of K is less than or equal to 5. However, partitioning the original DAG into a set of fanout free trees makes the final solution sub-optimal. To improve the quality of the mapping, Chortle exploits reconvergent paths and replicates logic at fanout nodes after each mapped tree is assembled into a circuit [Fran91a].

## 2.3 Previous Work on Heterogeneous FP-GAs

There were two previous projects that performed initial investigations of heterogeneous FPGA architecture. Carl Mizuyabu's Bachelor's thesis [Mizu92] looked at heterogeneous LUTs and Keith Farkas investigated heterogeneous NAND gates [Fark92], in a course project.

#### 2.3.1 Heterogeneous NAND Gates

#### **Technology Mapping**

[Fark92] employed an experimental approach to investigate heterogeneous NAND gates based FPGAs. One key issue here is the technology mapping problem for heterogeneous NAND gates. Since there are no existing software

(a) Circuit Before Bin-Packing

(c) Circuit After Further Decomposition

Figure 2.3: An Illustration of Node-Mapping in Chortle

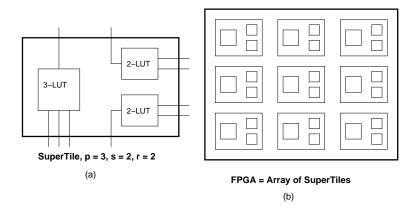

tools, as an approximation, the MIS [Bray87] software package was used as a technology mapper to map the input boolean network into a circuit of two sizes of NAND gates. In this work, the concept of a *supertile* was introduced. A supertile is defined as a group of a single primary gate (*p*-NAND) plus a number of secondary gates (*s*-NANDs), where p > s. Another important parameter is the ratio of the number of *s*-NANDs to p-NANDs, *r*, in each supertile. The heterogeneous nature of an FPGA is thus characterized by p, s, and r. The goal of the mapping is to minimize the number of supertiles to implement a boolean network, given p, s, and r. The mapping process used was as follows:

First, logic minimization and technology mapping was performed by using MIS to implement the given network into an FPGA of p-NANDs and s-NANDs. This is done by creating a library of p-NAND and s-NAND, each of which has a different cost. MIS will map the nodes of the network into either a p-NAND or an s-NAND or a mixture of them depending on their cost. The cost can affect the use of the NANDs, but the ratio r cannot be controlled, because the MIS algorithm cannot be constrained in this way.

After mapping, the number of *p*-NANDs and the number of *s*-NANDs are counted. If the number of *p*-NANDs used is  $N_p$  and the number of *s*-NANDs used is  $N_s$ , then the number of supertiles,  $N_{sup}$ , for a given value of *r*, can be calculated from equation (2.1):

$$N_{sup} = \max(N_p, \lceil \frac{N_s}{r} \rceil)$$

(2.1)

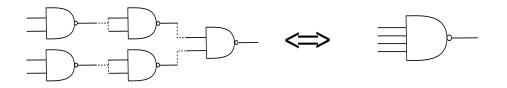

To minimize  $N_{sup}$ , the two terms in the **max** function of equation (2.1) should be equalized. In case  $N_p \neq \lceil \frac{N_s}{r} \rceil$ , conversion of a *p*-NAND into an *s*-NAND or a set of *s*-NANDs into a *p*-NAND is made. Figure 2.4 illustrates such a conversion where five 2-NANDs are used to replace a 4-NAND. Note that the conversion procedure will always improve or maintain the supertile count, never making it worse.

#### Architectural Investigation

To test the hypothesis that a heterogeneous NAND-gate FPGA will have superior density to a homogeneous one, 57 MCNC benchmark circuits were mapped into heterogeneous FPGAs with different combinations of p and sand then the number of supertiles were counted. Since supertiles for different

Figure 2.4: A set of 2-NANDs used to make a 4-NAND

p, s, and r have different sizes, comparison of number of supertiles cannot be used for the evaluation of area. Thus [Fark92] uses an area cost function based on the total number of gate pins as the routing area from pins is far more important than the active area used by logic blocks. The total number of pins of an FPGA is calculated by multiplying the total number of supertiles by the number of I/O pins per supertile.

[Fark92] finds that in the best case a 17% reduction in pins is achieved by using heterogeneous logic blocks. The best (p, s) is found to be (3, 2), (4, 2), or (5, 2), with ratios of three to five 2-NANDs to one of the larger size NAND gate.

### 2.3.2 Investigation of LUT-Based Heterogeneous FP-GAs:

Heterogeneous architectural investigation of LUT-based FPGAs was first tried in [Mizu92]. Since there was no heterogeneous technology mapper available then, the investigation was done using the Chortle homogeneous mapper [Fran92a] and some post-processing of the output. After running the homogeneous mapper, a mapped circuit consisting of homogeneous K-LUTs was obtained. Since not all inputs of the LUTs will be completely used, those LUTs whose number of used inputs is fewer than K may be replaced by LUTs with fewer than K inputs. In this way a heterogeneous FPGA circuit may be realized from processing a homogeneous mapping. This method of mapping is called *post-process-homo* (PPH). In the following discussion, the same terminology is used as those in mapping the NAND gates in section 2.3.1 except that it is applied to lookup table logic blocks.

Technology Mapping: Post-Process of a Homogeneous Mapper

The post-process-homo method works as follows: to map a network with a given p, s, and r, the homogeneous mapper is executed to map the network into LUTs of size p. For each LUT produced by the homogeneous mapper, let the number of inputs that are actually used be u. The LUTs for which  $u \leq s$ , are mapped directly into s-LUTs, resulting in  $N_s$  s-LUTs. The LUTs for which  $s < u \leq p$  are mapped into p-LUTs, resulting in  $N_p$  p-LUTs. The number of supertiles  $N_{sup}$  can be calculated from equation (2.1). Whenever there is an imbalance of  $N_p$  and  $\lceil \frac{N_s}{r} \rceil$ , a transformation between p-LUTs and s-LUTs can always be beneficial. The transformation process is described as follows:

When the post-process-homo results in fewer *p*-LUTs than  $\lceil \frac{N_s}{r} \rceil s$ -LUTs, that is, if  $N_p < \lceil \frac{N_s}{r} \rceil$ , then some of the *p*-LUTs will be left unused if we take an FPGA with  $\max(N_p, \lceil \frac{N_s}{r} \rceil)$  supertiles. In this case the extra *p*-LUTs in the supertiles can be used to implement *s*-LUTs to reduce the number of supertiles. Note that each *p*-LUT can be used to replace one and only one *s*-LUT. Let  $\triangle_s$  be the total number of *s*-LUTs converted from *p*-LUTs, then to minimize the number of supertiles we have

$$\begin{split} N_p + \triangle_s &= \left\lceil \frac{N_s - \triangle_s}{r} \right\rceil \\ \text{Solving this equation for } \triangle_s \text{ results in } \\ \triangle_s &= \lfloor \frac{N_s - rN_p}{r+1} \rfloor. \end{split}$$

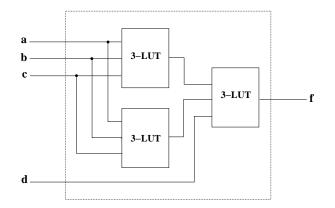

In the case that  $N_p > \lceil \frac{N_s}{r} \rceil$ , however, more *p*-LUTs are needed to achieve a balance and some of the *s*-LUTs can be transformed into *p*-LUTs. Since an *s*-LUT has less functionality than a *p*-LUT, several *s*-LUTs are needed to implement a *p*-LUT. The number of *s*-LUTs needed for a *p*-LUT depends on both *s* and *p*. Figure 2.5 shows how three 3-LUTs are converted to a 4-LUT, where the last LUT serves as a 2-input multiplexer with selection input *d*. Table 2.1 gives the number of *s*-LUTs needed to implement a *p*-LUT for various combinations of *p* and *s* [Mizu92]. We refer to this number as *n*.

Given p, s, r, and n, the number of p-LUTs needed to be transformed from s-LUTs can be easily calculated. Let  $\Delta_p$  be the total number of p-LUTs converted from s-LUTs, then we have

$$N_p - \triangle_p = \left\lceil \frac{N_s + n \triangle_p}{r} \right\rceil$$

Further solving for  $\triangle_p$  gives  $\triangle_p = \left\lfloor \frac{rN_p - N_s}{r + n} \right\rfloor$ .

#### Architectural Results

Based on the method described in the previous subsection, [Mizu92] con-

Figure 2.5: Realization of a 4-LUT by using three 3-LUTs

|              |          | р |    |    |    |     |  |  |

|--------------|----------|---|----|----|----|-----|--|--|

| ľ            | n        |   | 4  | 5  | 6  | 7   |  |  |

|              | <b>2</b> | 5 | 13 | 29 | 61 | 125 |  |  |

|              | 3        |   | 3  | 7  | 15 | 31  |  |  |

| $\mathbf{S}$ | 4        |   |    | 3  | 7  | 15  |  |  |

|              | 5        |   |    |    | 3  | 7   |  |  |

|              | 6        |   |    |    |    | 3   |  |  |

Table 2.1: Number of s-LUTs required to implement a p-LUT

ducted many experiments using the Chortle technology mapper to make an area comparison between homogeneous and heterogeneous FPGAs. The overall conclusion is that there is no advantage in using heterogeneous FPGA for area. [Mizu92] attributed this failure to the poor quality of the heterogeneous mapper. However, from Table 2.1 it is clear that the transformation of small LUTs to a large LUT will cause a significant increase in the number of pins and bits. For example, to make one 5-LUT, three 4-LUTs are needed. However, using one 5-LUT requires only 6 pins and  $2^5 = 32$  bits, while 3 4-LUTs costs  $3 \times (4+1) = 15$  pins and  $3 \times 2^4 = 48$  bits, which is much worse than an individual 5-LUT.

This method can be improved by translating s-LUTs into an u-LUT instead of a p-LUT when  $N_p > \lfloor \frac{N_s}{r} \rfloor$ , where u is the number of used inputs of a p-LUT after homogeneous mapping and  $u \leq p$ . Detailed discussion of this improvement is postponed to Chapter 3.

### 2.4 Commercial FPGAs with Heterogeneity

#### 2.4.1 Xilinx FPGAs

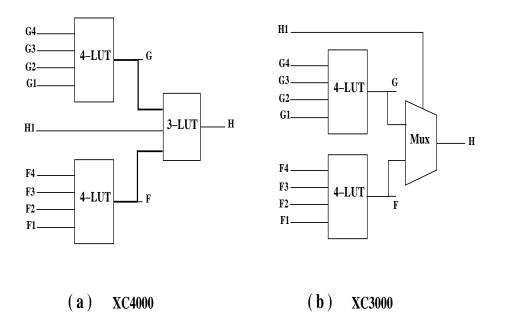

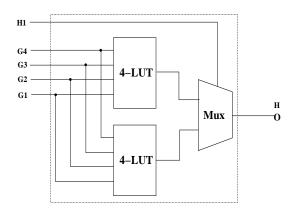

Xilinx FPGAs are a symmetrical array of logic blocks called Configurable Logic Blocks (CLBs). There are three generations of Xilinx FPGAs, the XC2000, XC3000, and XC4000. The core component of the CLBs of all the three generation FPGAs are lookup tables. As shown in Figure 2.6 (a), the XC4000 CLB contains two kinds of LUT, two 4-LUTs hardwired into a 3-LUT [Hsie90].

This kind of architecture contains limited heterogeneity. By "limited" it is meant that the LUTs are not entirely independent, since outputs of the two 4-LUTs must be hardwired to a 3-LUT. This constraint may prevent the free selection of LUTs in the mapping.

It is interesting that the Xilinx 3000 FPGAs also has an aspect of heterogeneity. As shown in Figure 2.6 (b), the XC3000 logic blocks are made of two 4-LUTs fed into a multiplexer. The two 4-LUTs can be either used as separate LUTs or made into a 5-LUT as in Figure 2.7. This kind of architecture can be used to make a heterogeneous FPGA provided that a mapper can make use of the heterogeneous property. Note that the XC2000 has similar heterogeneous property of the XC3000 except that the XC2000 logic block is

Figure 2.6: XC3000 and XC4000 Logic Block Architectures.

made of two 3-LUTs fed into a multiplexer.

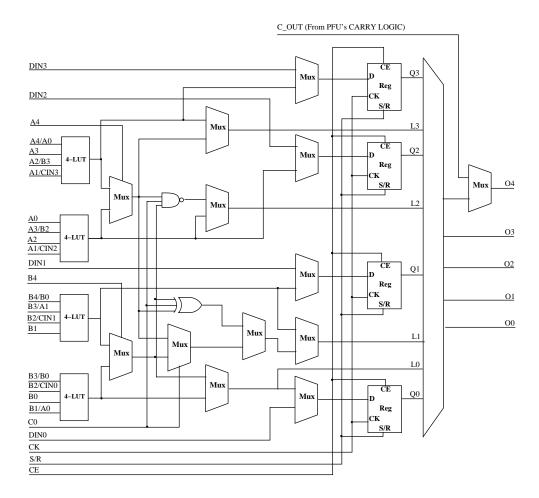

#### 2.4.2 The Architecture of AT&T ORCA FPGAs

AT&T's second generation of SRAM-based FPGAs, the Optimized Reconfigurable Cell Array (ORCA) [Brit93], also contains some aspects of heterogeneity. While the ORCA FPGA consists of array of identical, symmetrical logic blocks, called Programmable Logic Cells (PLCs), the PLCs can be used to implement different functions. Figure 2.8 shows a PLC block diagram. There are four 4-LUTs and four registers in each PLC. The four 4-LUTs can be used individually as 4-LUTs or used as into two 5-LUTs or one 6-LUT by properly programming the multiplexers shown in Figure 2.7.

This property of variable functionality of the logic block offers some of the advantages of heterogeneity. In the critical paths, PLCs can be made into coarse-grain blocks (6-LUTs, for example) to reduce the number of levels of logic blocks, while in the non-critical paths PLCs can be used as 4-LUTs to improve density (since 4-LUT is best for area [Rose90] [Koul92]). The

Figure 2.7: Two 4-LUTs is transformed into a 5-LUT

ORCA architecture has the significant advantage that during the technology mapping it is not necessary to control the ratio of the number of coarsegrained LUTs and the number of fine-grained LUTs. The conversion of 4-LUTs into larger-than 4-LUTs is done only when needed. However, the architecture also has a significant drawback: to make a 6-LUT from four 4-LUTs, the routing resources needed to connect to the many more pins of the four 4-LUTs are still in place, making this 6-LUT very expensive in area.

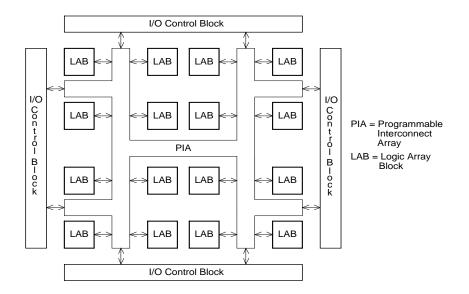

#### 2.4.3 The Altera MAX Architecture

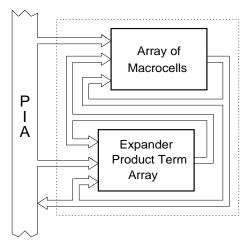

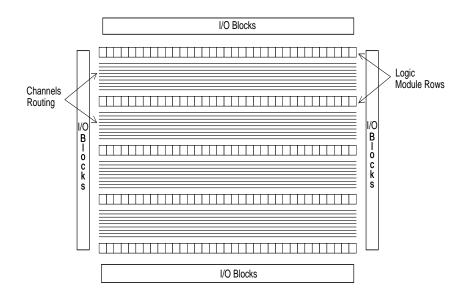

The logic block architecture of the Altera MAX EPLD family [Wong89] offers another example of a heterogeneous FPGA. The MAX FPGAs consist of an array of Logic Array Blocks (LABs), interconnected by a routing resource called the Programmable Interconnect Array (PIA). The general architecture of Altera FPGAs is shown in Figure 2.9 [Wong89].

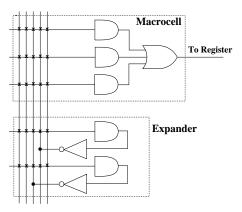

Each LAB contains two kinds of logic blocks, the macrocells and the expanders, as illustrated in Figure 2.10. There are between 16 and 32 macrocells in a LAB. In each of the macrocells three product terms are ORed together to feed into a register or bypass it. Expanders are single product terms with inverted outputs feeding back into the LAB. A simplified diagram of the macrocell and expander is given in Figure 2.11. The expanders are shared by all the macrocells in a LAB. If there are more than three product terms are required, the expanders will meet such a need. This kind of architecture

Figure 2.8: AT&T PLC Block Diagram

Figure 2.9: Altera FPGA Architecture (Figure From [Brow92])

Figure 2.10: Altera Logic Array Blocks (Figure From [Brow92])

is heterogeneous.

Figure 2.11: An Illustration of the Altera Macrocells and Expanders

#### 2.4.4 Actel's Act2 FPGAs

Actel FPGAs are row-based devices. Its logic blocks, called Logic Modules (LM), and horizontal routing channels are alternated in rows, as depicted in Figure 2.12.

There are two generations of Actel FPGAs, Act-1 and Act-2. The Act-1 device uses only one general purpose module (and hence is homogeneous) which can implement all combinational functions of 2 inputs, many of 3 or 4 inputs, and others ranging up to 8 inputs. A sequential macro can be configured from one or more modules by using appropriate feedback routing.

The Act-2 FPGA, an enhanced version of the Act-1, contains two kinds of blocks, the C (Combinational) module which is used to implement combinational logic and the S (Sequential) module which is optimized to realize sequential elements.

Actel claimed that by using heterogeneous scheme, the number of modules required for a block of logic can be reduced by up to a factor of 3 [Ahre90]. On average, logic density per module is increased by over 50%. Furthermore, because the density is increased, the number of routed nets in a typical critical path is reduced. This heterogeneous architecture significantly improves

Figure 2.12: General Architecture of Actel FPGAs (Figure From [Brow92])

speed. Note that the functionalities of the combinational parts of the C and S modules are almost identical, and so this is not the kind of heterogeneity discussed in this thesis.

## 2.5 Summary

In this Chapter, we first introduced LUT and LUT-based FPGA technology mapping. A technology mapper for LUT was then described. Two previous initiatives of heterogeneous architecture were discussed for NAND and LUT-based FPGAs. A method for technology mapping of heterogeneous FPGAs based on a post-process of a homogeneous mapper was described. This method suffers from serious deterioration when the resulting number of heterogeneous blocks are heavily unbalanced.

Commercial FPGA architectures with heterogeneity were also outlined in this chapter.

In the next chapter, an algorithm designed specifically for heterogeneous FPGA technology mapping will be described and it will be shown that it overcomes the difficulties with the PPH mapping.

## Chapter 3

# Heterogeneous Technology Mapping

This chapter presents a technology mapping algorithm for heterogenous FP-GAs with two different sizes of lookup table (LUT) logic blocks. Synthesis for such FPGAs is more difficult than for homogeneous FPGAs. For example, if there are two kinds of LUT which are present in equal numbers then the mapper must use the LUTs in equal proportion. This leads to a cost function that is not a linear count of the number of LUTs used and hence is difficult to optimize.

In this chapter a general method to solve problems of this nature is presented. This encompasses three steps. First, partition the input boolean network, in the form of a Directed Acyclic Graph (DAG), into a forest of fanout-free trees, then map each tree, and finally conduct an optimization amongst these trees. The cross-tree optimization algorithm will be shown to be optimal.

This chapter is organized as follows: the next section describes the basic notation and defines the technology mapping problem. Section 2 gives an overall strategy to solve the heterogeneous mapping problem. Section 3 describes the heterogeneous technology mapping algorithm on a single tree, while Section 4 provides the multi-tree algorithm and a proof of its optimality. The last section compares the quality of the proposed algorithm with a post-process of a homogeneous mapper.

### **3.1** Notation and Problem Definition

In this work we will consider heterogeneous FPGAs with only two sizes of lookup table. The larger lookup table will be referred to as the p-LUT, and the smaller as the s-LUT (p > s). An important architectural parameter of a heterogenous FPGA is the ratio r which is defined as the number of s-LUTs to the number of p-LUTs in the FPGA. This ratio is fixed for a given FPGA, because FPGAs are pre-fabricated. For simplicity, r is assumed to be either an integer, when  $r \ge 1$ , or the reciprocal of an integer, when r <1. Thus if  $r \ge 1$  then there are r s-LUTs for each p-LUT, and if r < 1 there are  $\frac{1}{r}$  p-LUTs for every s-LUT. Therefore, the tuple H = (p, s, r) defines a heterogeneous FPGA block architecture.

The heterogenous technology mapping problem can be stated as follows: given a boolean network, G, produce a mapped circuit M, which is a network of p-LUTs and s-LUTs of equivalent functionality to G. We are interested in minimizing the size of the FPGA needed to implement the boolean network. Since r is fixed for heterogenous FPGAs, the basic unit of *size* of a heterogenous FPGA is r s-LUTs and one p-LUT for  $r \ge 1$  ( $r \ge 1$  will usually be assumed for the sake of brevity, but similar definitions apply when r <1). Hence we wish to minimize the number of these units, which we call a *supertile*.

Figure 3.1(a) gives an example of supertile with H = (3, 2, 2). Figure 3.1(b) illustrates an array of such supertiles.

Figure 3.1: Example Supertile and Heterogenous FPGA

If we designate the number of p-LUTs in the mapped network M to be  $N_p$ , and the number of s-LUTs to be  $N_s$ , then the number of supertiles,  $N_{sup}$ , is given by:

$$N_{sup} = \max(N_p, \lceil \frac{N_s}{r} \rceil) \quad (r \ge 1)$$

The max function makes it a non-linear cost function and hence it is difficult to minimize. For example, if r = 1, then for every *p*-LUT that is used in M, an *s*-LUT *must* be used by the mapper, or else it is wasted. This is different from standard technology mapping into an ASIC library, in which a mapper is free to choose *any* number of each kind of library element.

It is important to note that Figure 3.1 displays only the *abstraction* of a supertile, and is not meant to speak to the actual positioning or interconnection of the lookup tables. While this is an important issue, our purpose in this work is to explore the benefits of heterogenous architectures at the logic level. Should it prove successful, this will motivate subsequent work on the actual physical design of such an FPGA.

### **3.2** General Approach and Overall Flow

To solve the non-linear optimization problem, the general approach used here is to break it up into a set of linear optimization problems, each of which is more tractable. The essence of the approach is that we map the network several times, with different constraints each time. In the first mapping the number of *p*-LUTs  $(N_p)$  in the circuit is constrained to be zero and the number of *s*-LUTs  $(N_s)$  is minimized. In the second mapping,  $N_p$  is constrained to be exactly one, and  $N_s$  is again minimized. This process continues with the fixed value of  $N_p$  increasing by one until the value of  $N_s$  achieved reaches zero. This process results in several mappings. Given the value of *r*, one of these mappings will result in the minimum number of supertiles, as defined above, and the number of supertiles can be easily determined by calculating  $N_{sup}$  for each mapping.

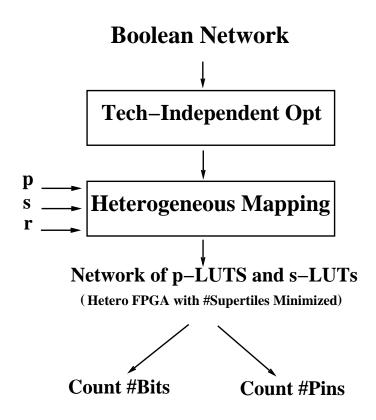

The overall flow of the algorithm is as follows: as in [Keut87], it begins by breaking the boolean network into a forest of maximal fanout-free trees, and thereafter each tree is mapped separately. Each tree is mapped several times as described above, resulting in multiple implementations for each tree. This is followed by an algorithm which optimally selects the set of mappings, one for each tree, that minimizes the number of supertiles in the entire circuit. The mapping flow is depicted in Figure 3.2.

Figure 3.2: Overall Flow of the Heterogeneous FPGA Synthesis

## 3.3 Mapping a Single Tree

The principal tree mapping technique used in the algorithm is a generalized version of dynamic programming [Corn87]. As in dynamic programming for technology mapping, the combinational network is traversed from the inputs of the tree and proceeds to the root. Every node is mapped based on the mapped fanin information. The ordering of traversal guarantees that the fanin circuits have already been constructed.

#### 3.3.1 Mapping a Node

At each node, a *list* of best circuits is constructed, each of which has a different number of *p*-LUTs. That is, each node is implemented several times, for  $N_p = 0, 1, 2$  and so on, while the number of *s*-LUTs,  $N_s$ , is minimized. The circuit list terminates when  $N_s = 0$ . Each circuit implements the cone extending from the node to the inputs of the tree.

If the node is a leaf, an s-LUT is used since it is smaller than a p-LUT and can always be changed into a p-LUT later if that is beneficial. For a non-leaf node, a set of best circuits are constructed from the list of circuits that have already been constructed on its fanin edges. Figure 3.3 gives the pseudo-code to illustrate the mapping of a single tree.

```

MapTree(tree,p,s)

```

Figure 3.3: Pseudo-code of Dynamic Programming for Mapping a Tree

Figure 3.4 gives a pseudo-code description for mapping a single non-leaf node. The input is a list of best circuits (one circuit for each value of  $N_p$ ) for each fanin edge. The output is a similar list describing the best circuits (with the fewest *s*-LUTs) for each value of  $N_p$ .

Notice that many different combinations of the fanin circuits will lead to a node circuit that has a fixed value of  $N_p$ . For example, suppose there are two fanin edges, a and b, to a node and each of the edges has a list of two circuits,  $\{C_0^a, C_1^a\}$  and  $\{C_0^b, C_1^b\}$ , where subscript in each circuit represents its number of p-LUTs. There are three combinations of these fanin circuits that may lead to a node circuit with  $N_p = 1$ :  $C_1^a \& C_0^b$ , or  $C_0^a \& C_1^b$ , or  $C_0^a \& C_0^b$ . In the last case the p-LUT would be created in the mapping of the node itself; in the two former cases the *p*-LUTs are inherited from the fanins and no *p*-LUTs are created in these two cases. Note that once a *p*-LUT is created it cannot turn back into an *s*-LUT, because p > s. However, an *s*-LUT can later become a *p*-LUT.

Since it is not known which of the fanin circuits will result in the very best value of  $N_s$ , every possible combination of the input circuit lists is evaluated, and the best is selected.

While this could result in a large number of combinations, experience on a range of benchmark circuits indicates that the number is tractable. In the worst case the total number of combinations did not exceed 414,724 and only 13 cases fall in the range  $10^4 - 10^6$  for 40 MCNC benchmark circuits. Over 98.7% of the nodes required fewer than 50 combinations of input fanin circuits. This happens likely because we operate on fanout-free trees, which are typically small.

The outer loop in procedure MapNode is to enumerate each such combination. In each inner loop iteration in procedure MapNode, the desired number of p-LUTs is fixed. The lower limit on this value is the sum of the number of p-LUTs in the immediate fanin circuits. The loop runs until the number of s-LUTs is reduced to zero.

Inside the inner loop, the following problem is solved: given a fixed number of p-LUTs to create,  $N_p$ -create, and a fixed set of mapped fanin circuits, map the current node using exactly  $N_p$ -create p-LUTs and the minimum number of s-LUTs.

At this point the algorithm uses a bin-packing strategy similar to [Fran91a]. The problem to be solved is more difficult, however, because there are two kinds of LUTs to pack the logic into. The following sections describe the *packing* of the fanin circuits into two different sizes of bins, and the final construction of the tree at the current node.

#### 3.3.2 Packing Fanin Lists into Heterogeneous LUTs

Francis' Chortle algorithm [Fran91a] makes use of a bin-packing algorithm to pack the root LUTs of the fanin circuits and the current node into an optimal tree circuit with the best possible decomposition of the current node. This is based on the observation that only the number of used inputs in the LUTs is important in determining if logic will fit into a LUT. In [Fran91a] the fanin

```

MapNode(node)

```

```

\{ \text{ BestList}[node] \leftarrow empty \\ \text{For each combination of fanin circuits to node } \{ \\ N_{p}\text{-in} \leftarrow \text{total } \#p\text{-LUTs of immediate fanins} \\ N_{p}\text{-create} \leftarrow N_{p}\text{-in} \\ \text{While } (N_s \neq 0) \\ \{ \\ // \text{ pack into } N_p\text{-create } p\text{-LUTs and minimum } \#s\text{-LUTs} \\ \text{Packing} \leftarrow \text{BinPack}(node, N_p\text{-create}) \\ // \text{ make packed LUTs into a tree} \\ \text{Tree} \leftarrow \text{TreeForm}(\text{Packing}) \\ \text{ if Tree best so far with value of } N_p, \text{ then} \\ \text{ record it in BestList}[node] \\ N_p\text{-create} \leftarrow N_p\text{-create} + 1 \\ \} \\ \} \\ \end{cases}

```

Figure 3.4: Pseudo-code for Mapping a Node

root LUTs correspond to "boxes" to be packed, and the resulting LUTs are the receiving "bins", of size K. We apply the same approach, except that the problem is more difficult because there are now two sizes of bin, p and s.

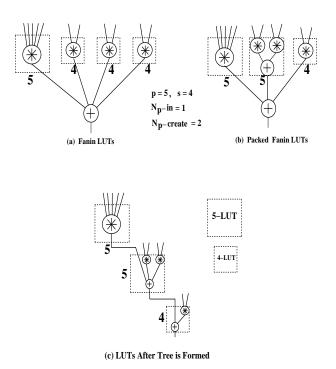

An illustration of heterogeneous bin packing is given in Figure 3.7(a) and 3.7(b), for  $N_{p}$ -create = 2, where p = 5 and s = 4.

The heterogeneous bin packing problem can be stated as follows: given a number of *p*-LUTs to create ( $N_{p}$ -create), and the fanin circuits' root LUTs, pack the fanin root LUTs into exactly  $N_{p}$ -create *p*-LUTs and a minimum number of additional *s*-LUTs.

We apply a variation of the First-Fit Decreasing algorithm: first create the number of p-LUTs that already exist in the fanin root LUTs. Then sort the remaining fanin root LUTs ("boxes") into decreasing order and put them into the first LUTs fitted. If a new "bin" is needed, create a p-LUT if  $N_p$ -create p-LUTs have not yet been created, and otherwise create an s-LUT. Figure 3.5 gives the pseudo-code outline of this packing algorithm. Although not shown in Figure 3.5, we also apply the re-convergent fanout optimization by using the Maximum Share Decreasing algorithm described in [Fran92a] and [Brow92]. However, replication of logic is not exploited due to the complexity of such a procedure.

#### 3.3.3 Forming a Tree

After the packing of the fanin root LUTs is completed, these packed LUTs are connected to form a tree to realize the current node and its fanins. The LUTs are sorted by decreasing order of number of used inputs and the output of the largest is connected to any unused inputs in the subsequent bins. The purpose of this procedure is to make the root node have as many unused inputs as possible. This is beneficial because the unused inputs can be utilized by subsequent nodes, as described in [Fran91a].

If there are insufficient inputs to connect all the LUTs together, then new s-LUTs are created. Figure 3.6 gives the pseudo code of the tree forming procedure and Figure 3.7(c) illustrates the tree forming procedure for the packed circuit of Figure 3.7(b).

### 3.4 Multi-tree Optimization

#### 3.4.1 The Multi-tree Optimization Procedure

After each tree  $T_i$  (i=1, 2,..., m) has been mapped, the algorithm has produced a set of circuits {  $C_j{}^i$  } where *i* is the tree number, and j is the number of *p*-LUTs in the mapped solution for that tree. For each circuit,  $C_j{}^i$ , let  $S_j{}^i$  be its number of *s*-LUTs. Table 3.1 gives an example of several typical values of  $S_j{}^i$  for p = 5 and s = 4.

Recall that the optimization goal is to find the minimum number of supertiles given by:  $N_{sup} = \max(N_p, \lceil \frac{N_s}{r} \rceil)$ , where for Table 3.1,  $N_p = j$  and  $N_s = S_j^i$ .

For each tree,  $N_{sup}$  can be easily calculated simply from  $N_p$  and  $N_s$  in each mapped solution, and the best selected. For example, from Table 3.1,

| $\mathbf{j} \ (= N_p)$ | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|------------------------|---|---|---|---|---|---|---|---|

| $S_j^i \ (= N_s)$      |   |   |   |   |   |   |   |   |

Table 3.1: Example mapping counts of *p*-LUTs and *s*-LUTs for one tree

if r = 1, then the solution with  $N_p = 4$ ,  $N_s = 4$  (4 supertiles) table entry is minimal and the corresponding circuit should be selected. If r = 2, then  $N_p = 3$ ,  $N_s = 6$  (3 supertiles) is minimal.

While this is simple for a single tree, the problem becomes more difficult when optimizing the number of supertiles across a number of trees. It may be that one tree is efficiently implemented using mostly s-LUTs and a second tree is better with mostly p-LUTs. If the number of supertiles in the trees were optimized individually, as above, this advantage may never be realized, since such a procedure seeks to balance the s-LUTs and p-LUTs according to ratio r on an individual tree basis.

A naive algorithm, however, that evaluates all possible combinations of table entries across all trees has enormous complexity. If the number of table entries per tree is n, and there are m trees, then the number of different combinations of tree solutions is  $n^m$ . In the following we will present an algorithm to solve this problem optimally with complexity  $O((m \times n)^2)$ .

We will first illustrate the basic algorithm on the combination of two trees, with family of solutions  $\{C_j^{\ 1}\}$  and  $\{C_j^{\ 2}\}$ . Let the number of *s*-LUTs be  $S_0^{\ 1}, S_1^{\ 1}, S_2^{\ 1}, \dots S_{n_1}^{\ 1}$  for Tree 1, and  $S_0^{\ 2}, S_1^{\ 2}, S_2^{\ 2}, \dots S_{n_2}^{\ 2}$  for Tree 2, where  $n_1$  and  $n_2$  are integers. When the two trees are taken together, we need to determine  $MS_n^{\ 1\cup 2}$ , the smallest number of *s*-LUTs for a fixed number of *p*-LUTs, n, where  $n = 0, 1, 2, \dots n_1 + n_2$  and  $MS_n^{\ 1\cup 2} = \min(S_n^{\ 1\cup 2})$ .  $MS_0^{\ 1\cup 2}$  can be found by summing  $S_0^{\ 1}$  and  $S_0^{\ 2}$ . The value of  $MS_1^{\ 1\cup 2}$  is given by  $\min(S_0^{\ 1} + S_1^{\ 2}, S_1^{\ 1} + S_0^{\ 2})$ . Similarly, for higher values of  $n, MS_k^{\ 1\cup 2}$  can be determined by finding the minimum sum of all possible pairs of  $S_x^{\ 1}$  and  $S_y^{\ 2}$ , for which x + y = n.

Table 3.2 gives an example of this calculation for two small trees, in which  $n_1 = 3$  and  $n_2 = 2$ . The rows labelled  $T_1$  and  $T_2$  provide the values of  $\{S_j^1\}$  and  $\{S_j^2\}$ . The next three rows show the possible combinations that provide the corresponding entries of  $S_j^{1\cup 2}$ . The final row gives the best of these combinations (that with the smallest number of *s*-LUTs). Note that if there

|                | $S_0$              | $S_1$              | $S_2$                 | $S_3$              | $S_4$              | $S_5$              |

|----------------|--------------------|--------------------|-----------------------|--------------------|--------------------|--------------------|

| $T_1$          | $5(C_0^1)$         | $3(C_{1}^{1})$     | $2(C_{2}^{1})$        | $0 (C_{3}^{1})$    |                    |                    |

| $T_2$          | $4 (C_0^2)$        | $2 (C^2_1)$        | $0 (C^2{}_2)$         |                    |                    |                    |

|                | $5 (C_0^1)$        | $3 (C_{1}^{1})$    | $2 (C_{2}^{1})$       | $0 (C_{3}^{1})$    |                    |                    |

|                | $4 (C_0^2)$        | $4 (C_0^2)$        | $4 (C_0^2)$           | $4 (C^2_0)$        |                    |                    |

| $T_1$ combined |                    | $5 (C_0^1)$        | $3(C_{1}^{1})$        | $2 (C_{2}^{1})$    | $0 (C^{1}_{3})$    |                    |

| with $T_2$     |                    | $2 (C^{2}_{1})$    | $2 (C_{1}^{2})$       | $2 (C_{1}^{2})$    | $2 (C_1^2)$        |                    |

|                |                    |                    | $5 (C_0^1)$           | $3 (C_{1}^{1})$    | $2 (C_{2}^{1})$    | $0 (C^{1}_{3})$    |

|                |                    |                    | $0 (C^2{}_2)$         | $0 (C_2^2)$        | $0 (C^2{}_2)$      | $0 (C^2{}_2)$      |

| $MS^{1\cup 2}$ | 9                  | 7                  | 5                     | 3                  | 2                  | 0                  |

| Circuit        | $(C^1{}_0C^2{}_0)$ | $(C^1{}_1C^2{}_0)$ | $(C^1 {}_1 C^2 {}_1)$ | $(C^1{}_1C^2{}_2)$ | $(C^1{}_3C^2{}_1)$ | $(C^1{}_3C^2{}_2)$ |

Table 3.2: Example of Tree Combination

is a tie, the circuit first encountered is chosen.

This algorithm can be extended to multiple trees by combining, in turn, a subsequent tree with the results of the previous trees. This forms, in turn,  $MS^{1\cup 2\cup 3}$ ,  $MS^{1\cup 2\cup 3\cup 4}$ , ....., and  $MS^{1\cup 2\cup \ldots \cup m}$ . Using this final table, the optimal number of supertiles can be determined for a given ratio, r, by applying the above equation for  $N_{sup}$ , and choosing the entry with the minimal numbers. This choice implies a set of choices of a specific  $C_j^{\ i}$  from each tree, and hence a complete mapping. This algorithm is optimal with respect to the number of supertiles, as shown below.

#### 3.4.2 Proof of Optimality of The Multi-tree Optimization

In this section, we will prove that the multi-tree combination algorithm is optimal. Recall that the input to this step is m mapped trees  $T_1, T_2, \dots, T_m$ . Let  $C_j^i$  be the mapped circuit in  $T_i$  with j p-LUTs and  $S_j^i$  be the number of s-LUTs in  $C_j^i$ . Then, the multi-tree optimization problem can be stated as follows:

Given: m trees:

$T_1: \quad S_0^1, S_1^1, S_2^1, \cdots, S_{n_1}^1$

where  $n_1, n_2, \dots, n_m$  are integers and  $S_j^i$  is the number of *s*-LUTs in the solution for tree *i* constrained to have j p-LUTs. **Find**: A final table  $MS^{* \ 1 \cup 2 \cup \dots \cup m}$  which has minimal number of *s*-LUTs

for a given number of p-LUTs for the entire circuit, i.e., find:

$$\begin{split} MS^{* \ 1 \cup 2 \cup \cdots \cup m} &= MS_0^{* \ 1 \cup 2 \cup \cdots \cup m}, MS_1^{* \ 1 \cup 2 \cup \cdots \cup m}, \cdots, MS_{k_m}^{* \ 1 \cup 2 \cup \cdots \cup m}. \\ where & k_m = \sum_{t=1}^m n_t, \\ MS_{j_m}^{* \ 1 \cup 2 \cup \cdots \cup m} &= \min_{(\forall i_t s.t. \ \sum_{t=1}^m i_t) = j_m} (\sum_{t=1}^m S_{i_t}^t) \\ where \ 0 \le i_t \le n_t, j_m = 0, 1, \cdots, k_m. \end{split}$$

The multi-tree optimization algorithm described in the previous section can

be re-written as the following calculation steps:

1.

$$MS^{1\cup 2} = MS^{1\cup 2}_0, MS^{1\cup 2}_1, \cdots, MS^{1\cup 2}_{k_2}$$

where  $k_2 = n_1 + n_2$ ,

$$MS_{j_2}^{1\cup 2} = \min_{\forall i_1, i_2, s.t. i_1 + i_2 = j_2} (S_{i_1}^1 + S_{i_2}^2)$$

where  $i_1 = 0, 1, \dots, n_1, i_2 = 0, 1, \dots, n_2, and$

$$j_2=0,1,\cdots,k_2.$$

2.

$$MS^{1\cup 2\cup 3} = MS^{1\cup 2\cup 3}_0, MS^{1\cup 2\cup 3}_1, \cdots, MS^{1\cup 2\cup 3}_{k_3}$$

$$k_3 = n_1 + n_2 + n_3,$$

$$MS_{j_3}^{1\cup 2\cup 3} = \min_{\forall j_2, i_3, s.t. j_2 + i_3 = j_3} (MS_{j_2}^{1\cup 2} + S_{i_3}^3),$$

where  $j_2 = 0, 1, \dots, k_2, i_3 = 0, 1, \dots, n_3, and$

$j_3 = 0, 1, \dots, k_3.$

$$\begin{array}{ll} \vdots \\ m. \ MS^{1\cup 2\cup \cdots \cup m} &= \ MS^{1\cup 2\cup \cdots \cup m}_{0}, MS^{1\cup 2\cup \cdots \cup m}_{1}, \cdots, MS^{1\cup 2\cup \cdots \cup m}_{k_{m}} \\ where & k_{m} = \sum_{t=1}^{m} n_{t}, \\ MS^{1\cup 2\cup \cdots \cup m}_{j_{m}} &= \min_{\forall j_{m-1}, i_{m}, s.t. j_{m-1}+i_{m}=j_{m}} (MS^{1\cup 2\cup \cdots \cup (m-1)}_{j_{m-1}} + S^{m}_{i_{m}}), \\ where \ j_{m-1} = 0, 1, \cdots, k_{m-1}, i_{m} = 0, 1, \cdots, n_{m}, and \end{array}$$

$$j_m = 0, 1, \cdots, k_m.$$

where  $MS^{1\cup 2\cdots \cup m}$  represents the solution obtained in the multi-tree optimization procedure.

**Theorem:** The multi-tree optimization algorithm described above is optimal. The solution,  $MS^{1\cup 2\cdots \cup m}$ , obtained in the multi-tree optimization procedure, has the minimal number of s-LUTs for a given number of p-LUTs for the entire circuit. That is,  $MS^{1\cup 2\cdots \cup m} = MS^{* \ 1\cup 2\cdots \cup m}$ .

#### **Proof:**

We prove the *optimality* of the above algorithm by *induction*.

m = 2 (the base case): m = 2 is trivial since the calculation of  $MS^{1\cup 2}$  is exhaustive. Therefore,  $MS^{1\cup 2} = MS^{* 1\cup 2}$ .

To make the induction step simple and more intuitive we first show how m = 2 optimality implies m = 3 optimality, by contradiction. m = 3:

Assume that when m = 2,  $MS^{1\cup 2} = MS^{*1\cup 2}$ .

Suppose, for contradiction, that for some  $j_3$ ,  $MS_{j_3}^{1\cup 2\cup 3}$  (where  $0 \le j_3 \le k_3$ ) is not the optimum (minimum); the optimum value is  $MS_{j_3}^{*\ 1\cup 2\cup 3}$ , which implies  $MS_{j_3}^{1\cup 2\cup 3} > MS_{j_3}^{*\ 1\cup 2\cup 3}$ .

Since  $MS_{j_3}^{* \ 1\cup 2\cup 3}$  must have one of the  $S_{i_3}^3$  as its component, where  $i_3 = 0, 1, \dots, n_3$ , let that number be  $S_{i_3}^3$ .

Thus,  $MS_{j_3^*}^{*\ 1\cup 2\cup 3} = MS_{j_2^*}^{1\cup 2} + S_{i_3^*}^3$ , where  $i_3^* \in \{0, 1, \dots, n_3\}, j_2^* \in \{0, 1, \dots, k_2\}$  and  $k_2 = n_1 + n_2$ , and  $j_3^* \in \{0, 1, \dots, k_3\}$ .

Since  $MS^{1\cup 2} = MS^{* \ 1\cup 2}$  and

$$MS_{j_3}^{1\cup 2\cup 3} = \min_{\forall j_2, i_3, s.t. j_2 + i_3 = j_3} (MS_{j_2}^{1\cup 2} + S_{i_3}^3) = \min_{\forall j_2, i_3, s.t. j_2 + i_3 = j_3} (MS_{j_2}^{*1\cup 2} + S_{i_3}^3),$$

we can show the contradiction  $MS^{1\cup 2}_{j_2^*} < MS^{*\,1\cup 2}_{j_2^*}$  from the following arguments

Since we have:

$$MS_{j_3}^{1\cup 2\cup 3} > MS_{j_3}^{*\ 1\cup 2\cup 3}$$

,  $for some j_3 \in \{0, 1, \dots, k_3\}$

$\Rightarrow MS_{j_3}^{1\cup 2\cup 3} > MS_{j_3}^{*\ 1\cup 2\cup 3}$ , for  $j_3 = j_3^* \in \{0, 1, \dots, k_3\}$

$\Rightarrow MS_{j_3}^{1\cup 2\cup 3} > MS_{j_3}^{*\ 1\cup 2\cup 3} \mid_{\forall i_3, j_2 s. t. i_3 + j_2 = j_3^*}$

$\Rightarrow MS_{j_2^*}^{*\ 1\cup 2} + S_{i_3}^3 > MS_{j_2^*}^{1\cup 2} + S_{i_3}^3$

$\Rightarrow MS_{j_2^*}^{*\ 1\cup 2} > MS_{j_2^*}^{1\cup 2}$ .

Contradiction! since  $MS^{* \ 1 \cup 2}$  is the minimum. Therefore,  $MS^{1 \cup 2 \cup 3} = MS^{* \ 1 \cup 2 \cup 3}$ .

Now we prove the general case in a similar way [Hutt93]. m = K-1: assume that when m = K-1,  $MS_{j_{K-1}}^{1\cup 2\cdots \cup (K-1)} = MS_{j_{K-1}}^{* \ 1\cup 2\cdots \cup (K-1)}$

then we will prove the optimality for m = K (very similar to the proof for m = 3).

m = K: proof by contradiction.

Suppose that  $MS_{j_K}^{1\cup 2\cup \cdots \cup K} \neq MS_{j_K}^{*\ 1\cup 2\cup \cdots \cup K}$  which implies that  $MS_{j_K}^{1\cup 2\cup \cdots \cup K} > MS_{j_K}^{*\ 1\cup 2\cup \cdots \cup K}$ . Let  $S_{i_K}^K$  be the component for  $MS_{j_K}^{*\ 1\cup 2\cup \cdots \cup K}$  and  $MS_{j_K}^{*\ 1\cup 2\cup \cdots \cup K} = MS_{j_{K-1}}^{1\cup 2\cup \cdots \cup (K-1)} + S_{i_K}^K$ , where

$k_{K-1} = \sum_{t=1}^{K-1} n_t, k_K = \sum_{t=1}^{K} n_t, i_K^* \in \{0, 1, \dots, n_K\}, j_{K-1}^* \in \{0, 1, \dots, k_{K-1}\},$ and  $j_K^* \in \{0, 1, \dots, k_K\}.$

Then we have  $MS_{j_{K-1}^*}^{* \ 1 \cup 2 \cup \dots \cup (K-1)} > MS_{j_{K-1}^*}^{1 \cup 2 \cup \dots \cup (K-1)}$  since

xxxviii

$$\begin{aligned} \forall j_{K} \in \{0, 1, \cdots, k_{K}\}, MS_{j_{K}}^{1 \cup 2 \cup \cdots \cup K} > MS_{j_{K}}^{* 1 \cup 2 \cup \cdots \cup K} \\ \Rightarrow MS_{j_{K}}^{1 \cup 2 \cup \cdots \cup K} > MS_{j_{K}}^{* 1 \cup 2 \cup \cdots \cup K} |_{j_{K}=j_{K}^{*}} \\ \Rightarrow MS_{j_{K}^{*}}^{1 \cup 2 \cup \cdots \cup K} > MS_{j_{K}^{*}}^{* 1 \cup 2 \cup \cdots \cup K} \\ \Rightarrow MS_{j_{K}^{*}}^{1 \cup 2 \cup \cdots \cup K} > MS_{j_{K}^{*}}^{* 1 \cup 2 \cup \cdots \cup K} |_{\forall i_{K}, j_{K-1}s.t.i_{K}+j_{K-1}=j_{K}^{*}} \\ \Rightarrow MS_{j_{K-1}}^{* 1 \cup 2 \cup \cdots \cup (K-1)} + S_{i_{K}}^{K} > MS_{j_{K-1}^{*-1}}^{1 \cup 2 \cup \cdots \cup (K-1)} + S_{i_{K}^{*}}^{K} |_{i_{K}=i_{K}^{*}, j_{K-1}=j_{K-1}^{*}} \\ \Rightarrow MS_{j_{K-1}^{*}}^{* 1 \cup 2 \cup \cdots \cup (K-1)} + S_{i_{K}^{*}}^{K} > MS_{j_{K-1}^{*-1}}^{1 \cup 2 \cup \cdots \cup (K-1)} + S_{i_{K}^{*}}^{K} \\ \Rightarrow MS_{j_{K-1}^{*}}^{* 1 \cup 2 \cup \cdots \cup (K-1)} + S_{i_{K}^{*}}^{K} > MS_{j_{K-1}^{*-1}}^{1 \cup 2 \cup \cdots \cup (K-1)} + S_{i_{K}^{*}}^{K} \\ \Rightarrow MS_{j_{K-1}^{*}}^{* 1 \cup 2 \cup \cdots \cup (K-1)} > MS_{j_{K-1}^{*-1}}^{1 \cup 2 \cup \cdots \cup (K-1)} \end{aligned}$$

Contradiction! since  $MS^{* \ 1 \cup 2 \cup \cdots \cup (K-1)}$  is optimal for m = K - 1. Therefore,  $MS^{1 \cup 2 \cdots \cup m} = MS^{* \ 1 \cup 2 \cdots \cup m}$ .

### 3.4.3 Complexity of the Multi-tree Optimization Algorithm

Let N be the complexity of the multi-tree optimization algorithm,  $N_i$  be the complexity of each step in the calculation of  $S'_c$  in section 3.4.2, and  $n = \max_{i=1,2,\dots,m}(n_i)$ . Then

$$N_{1} = (n_{1} + 1) \times (n_{2} + 1)$$

$$N_{2} = (n_{1} + n_{2} + 1) \times (n_{3} + 1)$$

$$N_{3} = (n_{1} + n_{2} + n_{3} + 1) \times (n_{4} + 1)$$

$$\cdots = \cdots$$

$$N_{m-1} = (\sum_{t=1}^{m-1} n_{t} + 1) \times (n_{m} + 1)$$

and

$$N = \sum_{i=1}^{m-1} N_i$$

xxxix

$$= \sum_{i=1}^{m-1} (\sum_{t=1}^{i} n_t + 1)(n_{i+1} + 1)$$

$$\leq \sum_{i=1}^{m-1} (\sum_{t=1}^{i} n + 1)(n + 1)$$

$$= (n+1) \sum_{i=1}^{m-1} (i \times n + 1)$$

$$= (n+1) \times (n \sum_{i=1}^{m-1} i + m - 1)$$

$$= (n+1) \times (n \times \frac{m \times (m-1)}{2} + m - 1)$$

$$= (n+1) \times (m - 1) \times (\frac{(m \times n + 2)}{2})$$

$$= \mathbf{O}(m^2 n^2)$$

#### 3.5 Comparison with PPH Mapping Algorithm

This section gives a comparison between the quality of the heterogenous mapping algorithm with the best alternative approach that could be found: a post-process of output from a homogenous LUT mapper, which takes the non-homogeneity into account.

As mentioned in Chapter 2, the post-process-homo (PPH) was developed in [Mizu92]. To generate a heterogeneous FPGA, this method first used a homogeneous mapper (Chortle) [Fran91a] to map a given network into p-LUTs and then convert those LUTs whose number of used inputs are less than or equal to s into s-LUTs.

Following this step the number of supertiles used in this mapping was calculated using  $N_{sup} = \max(N_p, \lceil \frac{N_s}{r} \rceil)$  where  $N_p$  is the number of *p*-LUTs,  $N_s$  the number of *s*-LUTs, and *r* the ratio of number of *s*-LUTs to the number of *p*-LUTs. In the case that there is an imbalance between  $N_p$  and  $\lceil \frac{N_s}{r} \rceil$ , a transformation of *p*-LUTs and *s*-LUTs is performed in the following way. If  $N_p < \lceil \frac{N_s}{r} \rceil$ , then *p*-LUTs will be transformed to *s*-LUTs on a one-to-one basis. When  $N_p > \lceil \frac{N_s}{r} \rceil$ , several *s*-LUTs will be used to make a *p*-LUT, as described in section 2.3.2 of Chapter 2. This algorithm assumed that every *p*-LUT had all its inputs used. Hence to make a *p*-LUT from a

network of *s*-LUTs requires many *s*-LUTs, as shown in Table 2.1. In this section we compare the heterogeneous mapper with an improved version of this algorithm which is described below [Fran92b]:

After the homogeneous mapping step, the result is a set of LUTs. The number of inputs actually used on each LUT will range from 1 to p, where p is the size of a homogeneous LUT. Let  $D = \{D_1, D_2, \dots, D_u, \dots, D_p\}$  describe the distribution of this number, where  $D_u$  is the number of p-LUTs having u used inputs. As before the number of supertiles is calculated as  $N_{sup} = \max(N_p, \lceil \frac{N_s}{r} \rceil)$ , where  $N_s = \sum_{u=1}^s D_u$  and  $N_p = \sum_{u=s+1}^p D_u$ . If  $N_p > \lceil \frac{N_s}{r} \rceil$ , instead of transforming a network of s-LUTs into p-LUT, we transform s-LUTs into (s + 1)-LUTs to achieve a balance. If there are not enough (s + 1)-LUTs, then we transform s-LUTs into (s + 2)-LUTs and so on. This is better than the previous algorithm because the LUTs with fewer inputs require fewer s-LUTs in the implementation.

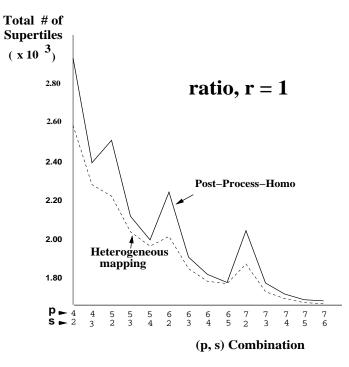

The Chortle-crf homogeneous mapper [Fran92a] was used as the basis for comparison since both the homogeneous mapper and the heterogeneous one have a similar mapping process. Both the new heterogeneous mapper and the post-process-homo mapper were run on 40 MCNC logic synthesis benchmarks circuits, and for many different values of s and p. The total number of supertiles obtained for each case was calculated, and these are illustrated in the plot in Figure 3.8. The Y-axis is the total number of supertiles for all the circuits and the X-axis gives the different combinations of s and p, with the ratio r = 1 for all cases. It is clear that the new algorithm is superior to the PPH algorithm. On average, for r = 1, the new algorithm produces 0.3% to 11.7% fewer supertiles than PPH. As will be shown below, for r > 1 the new algorithm provides even greater advantage over PPH.

The trends in Figure 3.8 (in particular, the large "jumps") can be explained as follows.

First, for each given p, as s increases, the number of supertiles decreases. This makes sense since for the same p increasing s will increase functionality of a supertile and this will decrease the number of supertiles needed.

Secondly, for each increase in p, there is a jump in the supertile count. For the heterogeneous FPGAs, this is likely caused by the decrease in functionality of a supertile. For example, supertile (p, s, r) = (6, 2, 1) has less functionality than (5, 4, 1) and a (7, 2, 1) is less than a (6, 5, 1).

For the PPH algorithm, however, there is another important reason to cause these increases besides the one just mentioned. Recall that in the post-processing of homogeneous FPGAs, there is a transformation between the *p*-LUTs and the *s*-LUTs. In the combinations where a big increase occurs, *p* and *s* differ significantly. In such cases, when a *p*-LUT is converted to an *s*-LUT or *s*-LUTs to a *p*-LUT, there can be a significant waste. For example, for p = 6 and s = 2. If we transform a 6-LUT into a 2-LUT (i.e. to use a 6-LUT to implement a 2-LUT), there will be a large waste of functionality. On the other hand, however, if we implement a 6-LUT using 2-LUTs, a total of 61 2-LUTs are needed (see Table 2.1). The cost is even more since one 6-LUT uses 7 pins and 64 bits but 61 2-LUTs require 183 pins and 244 bits. Therefore, the increase is bigger for PPH than for heterogeneous FPGA at each change of *p* values.

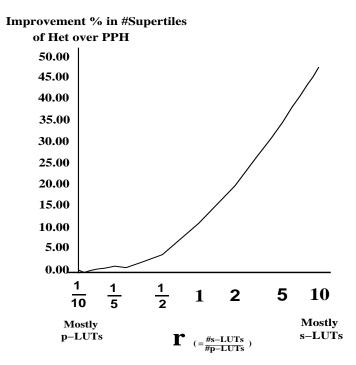

Figure 3.9 gives another view of the comparison of the heterogeneous and the PPH mappings. This figure presents the improvement percentage of the number of supertiles versus ratio r for combination (p, s) = (5, 2) which is typical of all the (p, s) combinations. The improvement is calculated using equation 3.1.

$$Improve\_pct = -\frac{(N_{sup} \ of \ Het) - (N_{sup} \ of \ PPH)}{N_{sup} \ of \ PPH} \times 100$$

(3.1)

where  $N_{sup}$  is the total number of supertiles needed for implementing the 40 benchmark circuits for combination (p, s, r) = (5, 2, r). Observe that for larger values of r, the new algorithm achieves more than 30% fewer supertiles than PPH.

Figure 3.9 can be explained as follows. First, when r is very small (e.g.  $r = \frac{1}{10}$ ), the difference between the heterogeneous and the PPH mappings is not very great. This is because the problem being solved is close to the homogeneous problem for p-LUTs. Both homogeneous and heterogeneous mappings are optimized at this point. Note that the PPH algorithm is tuned for this case, but the heterogeneous algorithm is tuned for all r. Thus as r increases, the relative improvement increases greatly. This increase is largely due to the fact that as r increases, there are more s-LUTs in each supertile in a given FPGA, while the number of s-LUTs and the number of p-LUTs after a PPH mapping are fixed for a fixed combination (p, s). This implies that we will need to transform more s-LUTs into p-LUTs for an implementation if r is large. As mentioned previously in this section, this kind of transformation is very costly.

|          | $\mathbf{s} \setminus \mathbf{p}$ | 7    | 6    | 5    | 4    | 3    |

|----------|-----------------------------------|------|------|------|------|------|

|          | post-homo                         | 2066 | 2263 | 2532 | 2954 | 3748 |

| <b>2</b> | hetero.                           | 1892 | 2035 | 2242 | 2607 | 3366 |

|          | decrease $(\%)$                   | 8.4  | 10.1 | 11.5 | 11.7 | 10.2 |

|          | post-homo                         | 1798 | 1927 | 2140 | 2414 |      |

| 3        | hetero.                           | 1750 | 1868 | 2058 | 2301 |      |

|          | decrease $(\%)$                   | 2.7  | 3.1  | 3.8  | 4.7  |      |

|          | post-homo                         | 1738 | 1838 | 2017 |      |      |

| 4        | hetero.                           | 1716 | 1805 | 1985 |      |      |

|          | decrease $(\%)$                   | 1.3  | 1.8  | 1.6  |      |      |

|          | post-homo                         | 1708 | 1799 |      | -    |      |

| <b>5</b> | hetero.                           | 1693 | 1793 |      |      |      |

|          | decrease $(\%)$                   | 0.9  | 0.3  |      |      |      |

|          | post-homo                         | 1702 |      | -    |      |      |

| 6        | hetero.                           | 1689 |      |      |      |      |

|          | decrease $(\%)$                   | 0.8  |      |      |      |      |

Table 3.3: Comparison with Post-Process of Homogeneous Mapping (r = 1)

Data values corresponding to Figure 3.8 are presented in Table 3.3. Average improvement for each combination (also for r = 1) is listed on the third row of each cell of the table. Note that this average improvement is based on the total number of supertiles of the 40 benchmark circuits used, implying that the calculation for the average has unequal weights for different circuits. Larger circuits have larger weights. Table 3.4 gives the average improvement of heterogeneous mapping over the PPH algorithm on an equal weight basis for each circuit. The average improvements in Table 3.4 are calculated by computing the improvement of each circuit and then averaging these numbers. Standard deviations of the improvements are also presented in the same table. The formula for calculating the standard deviation is shown in equation 3.2 below:

$$Std\_Dev = \sqrt{\sum_{i=1}^{40} \frac{(improve\_i - improve\_avg)^2}{40}}$$

(3.2)

|          | $\mathbf{s} \setminus \mathbf{p}$ | 7   | 6   | 5   | 4   | 3   |

|----------|-----------------------------------|-----|-----|-----|-----|-----|

| <b>2</b> | improve $(\%)$                    | 6.7 | 7.7 | 9.3 | 9.8 | 8.1 |

|          | std. dev $(\%)$                   | 5.8 | 6.3 | 7.4 | 6.2 | 5.1 |

| 3        | improve (%)                       | 2.6 | 2.4 | 2.7 | 3.8 |     |

|          | std. dev (%)                      | 5.4 | 6.5 | 5.3 | 6.0 |     |

| 4        | improve (%)                       | 1.3 | 1.6 | 0.8 |     |     |

|          | std. dev (%)                      | 4.9 | 5.0 | 3.0 |     |     |

| 5        | improve (%)                       | 0.4 | 0.2 |     |     |     |

|          | std. dev (%)                      | 1.7 | 1.2 |     |     |     |

| 6        | improve (%)                       | 0.8 |     |     |     |     |

|          | std. dev $(\%)$                   | 4.0 |     |     |     |     |

Table 3.4: Equal Weight Comparison with PPH Mapping and Standard De

viation

where  $improve\_avg = \sum_{i=1}^{40} \frac{improve\_i}{40}$  and improve\\_i is the improvement on the i-th benchmark circuit.

In general, the standard deviations have the same magnitudes as the improvement averages.

Table 3.5 gives detailed sample results for the heterogenous architecture p = 5, s = 2, and r = 1. The first column of this table gives the circuit name and the second column gives the number of supertiles using the algorithm described in this paper. The third column gives the supertile count for the post-process-homo algorithm, and the fourth column gives the percentage difference between the two. The fifth column gives the running time of the new algorithm on a Sun Sparcstation 2. The running times are usually in a few seconds and rarely more than a minute.

It should be pointed out that since the heterogeneous algorithm does not replicate logic at fanout nodes, the homogeneous mapping algorithm we use is also prevented from this replication. It is possible that this may affect these comparisons.

| Circuit              | #Supertiles   | #Supertiles      | Difference | Run Time  |  |

|----------------------|---------------|------------------|------------|-----------|--|

| Names                | (Hetero Algo) | (Post-Homo)      | (%)        | (in Sec.) |  |

| C1355                | 82            | 82               | 0.0        | 1.6       |  |

| C432                 | 55            | 59               | -6.8       | 10.0      |  |

| C880                 | 63            | 72               | -12.5      | 4.2       |  |

| alu2                 | 72            | 80               | -10.0      | 93.8      |  |

| alu4                 | 124           | 138              | -10.1      | 92.9      |  |

| apex6                | 136           | 161              | -15.5      | 19.9      |  |

| apex7                | 42            | 48               | -12.5      | 0.8       |  |

| b9                   | 24            | 24               | -0.0       | 0.4       |  |

| c8                   | 23            | 25               | -8.0       | 0.5       |  |

| $\operatorname{cht}$ | 30            | 35               | -14.3      | 0.4       |  |

| ${ m cm}150{ m a}$   | 9             | 10               | -10.0      | 0.3       |  |

| cm151a               | 5             | 5                | 0.0        | 0.1       |  |

| cm85a                | 7             | 8                | -12.5      | 0.1       |  |

| cmb                  | 10            | 12               | -16.7      | 0.1       |  |

| count                | 23            | 23               | 0.0        | 0.4       |  |

| example2             | 57            | 64               | -10.9      | 1.1       |  |

| frg1                 | 21            | 24               | -12.5      | 18.1      |  |

| frg2                 | 150           | 171              | -12.3      | 3.7       |  |

| i1                   | 10            | 10               | 0.0        | 0.1       |  |

| i6                   | 64            | 67               | -4.5       | 3.2       |  |

| i7                   | 95            | 112              | -15.2      | 9.2       |  |

| i8                   | 181           | 225              | -19.6      | 12.6      |  |

| i9                   | 106           | 123              | -13.1      | 9.8       |  |

| k2                   | 187           | 207              | -9.7       | 11.5      |  |

| my-adder             | 32            | 32               | 0.0        | 0.4       |  |

| parity               | 8             | 8                | 0.0        | 0.1       |  |

| pcler                | 16            | 16               | 0.0        | 0.2       |  |

| pm1                  | 9             | 10               | -10.0      | 0.1       |  |

| rot                  | 124           | 135              | -8.1       | 2.5       |  |

| $\operatorname{sct}$ | 14            | 15               | -6.7       | 0.1       |  |

| t481                 | 6             | xlv <sup>6</sup> | 0.0        | 0.1       |  |

| term1                | 24            | 28               | -14.3      | 1.2       |  |

| ttt2                 | 30            | 33               | -9.1       | 0.5       |  |

| unreg                | 18            | 29               | -37.9      | 0.7       |  |

| vda                  | 105           | 114              | -7.9       | 1.7       |  |

| x1                   | 57            | 63               | -9.5       | 4.5       |  |

| x2                   | 9             | 10               | -10.0      | 0.1       |  |

#### 3.6 Summary

A technology mapping algorithm designed specifically for a heterogeneous FPGA was described in this chapter. This algorithm maps a boolean network into a heterogeneous FPGA that has two kinds of logic block in a fixed ratio.

This algorithm first partitions a given DAG into a set of fanout-free trees and then maps each tree into a list of best circuits. These circuits are functionally equivalent, but have different number of p-LUTs. The number of p-LUTs used in each circuit ranges from zero (the tree is mapped all with s-LUTs) to the number where the tree is mapped all with p-LUTs. In this way, we can find out which LUT is most suitable for implementing a portion of network and make advantageous use of the LUTs.