## Ultra-Fast Automatic Placement for FPGAs

by

## Yaska Sankar

A thesis submitted in conformity with the requirements for the degree of Master of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto

© Copyright by Yaska Sankar 1999

### Abstract

#### Ultra-Fast Automatic Placement for FPGAs

Master of Applied Science, 1999 Yaska Sankar Department of Electrical and Computer Engineering University of Toronto

The demand for high-speed Field-Programmable Gate Array (FPGA) compilation tools has escalated for three reasons: first, as FPGA device capacity has grown, the computation time devoted to placement and routing of circuits has grown more dramatically than the available computer power. Second, there exists a subset of users who are willing to accept a reduction in the quality of result (using a larger FPGA or more resources on a given FPGA) in exchange for a high-speed compilation. Third, high-speed compile has been a long-standing desire of users of FPGA-based custom computing machines, since their compile time requirements are ideally closer to those of regular computers.

This thesis focuses on the placement phase of the compile process, and presents an ultrafast placement algorithm for FPGAs. The algorithm is based on a combination of multiple-level, bottom-up clustering and hierarchical simulated annealing.

It provides superior area results over a known high-quality placement tool on a set of large benchmark circuits, when both are restricted to a short run time. For example, in 10 seconds of placement time on a 300 MHz Sun UltraSPARC, the ultra-fast tool realizes an average wirelength improvement of 30% compared to the high-quality tool. It can also generate a placement for a 100,000-gate circuit in 10 seconds that is only 31% worse than a high-quality placement that takes 524 seconds using a pure simulated annealing implementation. For this circuit, the ultra-fast tool achieves this level of placement quality 5 times faster than the high-quality tool.

In addition, when operating in its fastest mode, the ultra-fast placement tool can provide an accurate estimate of the wirelength achievable with good quality placement (within 6%, on average). This can be used, in conjunction with a routing predictor, to very quickly determine the routability of a given circuit on a given FPGA device.

### Acknowledgments

I am profoundly grateful to my advisor, Jonathan Rose, for allowing me to draw upon his vast technical expertise, his infectious zeal, and his unwavering confidence in my abilities as a researcher. I am indebted to him for setting high standards for his students in both technical achievement and communication, and for going beyond the duties of a supervisor to act as a teacher, mentor, promoter, motivator, counselor, and loyal supporter. I value his technical lessons, patience, encouragement, sage advice, and above all, enthusiastic guidance during my time here.

I have also greatly benefited from the collective wisdom of the members of Professor Rose's research group: Vaughn Betz, Jordan Swartz, Mohammed Khalid, Steve Wilton, Mike Hutton, Sandy Marquardt, Rob McCready and Paul Leventis. I am particularly grateful to Vaughn not only for faithfully providing the infrastructure and support of the software used to house this work, but also for the time, advice, and guidance he offered throughout. Jordan and Vaughn merit special thanks for their helpful and insightful comments on an earlier draft of this thesis.

My time here would have been far less educational and enjoyable without the antics of my many friends and colleagues in LP392 and SF2206: the other founding members of the infamous Package Deal (Jason "Virtual Beverage Engineer" Podaima, Vaughn "Mr. Optimal" Betz, Jordan "Human Torch" Swartz), Sandy "Formatting Monkey" Marquardt, Qiang "Be A Man" Wang, Jason A., Andy, Marcus, Ali, Warren, Mazen, Vincent, Mark, Khalid, Jeff, Dave, Javad, Rob, Ken, Wai, Nirmal, Paul, Guy, Dan, Alex, Derek, Rob, Gia, Sush, Keith, Marcel, Jane, Kevin, Bob, Aris, John, Sudarsan, Duncan, and the Electric Fielders softball teams with whom I had the distinct pleasure of playing, to name a few. They are wholly responsible for provoking stimulating discussions and providing spirited diversions, and I thank them for it.

I consider myself fortunate to know a few kind souls whose friendship, support, encouragement, advice, and willingness to listen made things bearable during the difficult times and delightful the rest of the time: Steve, John, Heather, Mike VDP, and Nav.

Whatever success I have achieved here I owe to the steadfast support, encouragement, patience, faith and love of my parents and my brother.

Finally, this work would not have been possible without the financial support from the Natural Sciences and Engineering Research Council, the University of Toronto, Communications and Information Technology Ontario, Lucent Technologies Inc., Xilinx Corporation, and the Information Technology Research Centre of Ontario.

## **Table of Contents**

| Chapter 1 Introduction                                              | 1  |

|---------------------------------------------------------------------|----|

| 1.1 Motivation                                                      | 1  |

| 1.2 Goals and Scenarios                                             | 3  |

| 1.3 Research Approach                                               | 5  |

| 1.4 Thesis Organization                                             | 5  |

| Chapter 2 Background and Previous Work                              | 6  |

| 2.1 Definition of FPGA Placement Problem                            | 6  |

| 2.2 Placement Algorithms                                            | 8  |

| 2.2.1 TimberWolf                                                    | 8  |

| 2.2.2 Hierarchical Clustering and Annealing                         | 11 |

| 2.2.3 VPR - Versatile Place and Route                               | 13 |

| 2.2.4 Algorithms Based on Variations of Hierarchical Clustering and |    |

| Simulated Annealing - NRG and Simulated Quenching                   | 15 |

| 2.2.5 Choice of Starting Temperature for Simulated Annealing        | 17 |

| 2.3 Clustering Algorithms                                           | 19 |

| 2.3.1 Using Clustering to Reduce Problem Complexity                 | 19 |

| 2.3.2 Cost Functions Used to Build Clusters                         | 20 |

| 2.4 Fast Compile Algorithms                                         | 23 |

| 2.4.1 Lola                                                          | 23 |

| 2.4.2 GAMA                                                          | 24 |

| 2.4.3 Fast Placement for FPGAs via Automatic Floorplanning          | 25 |

| 2.4.4 Fast Routing and Difficulty Prediction                        | 26 |

| 2.5 Summary                                                         | 26 |

| Chapter 3 Ultra-Fast Placement Algorithm                            | 27 |

| 3.1 Overview of Approach                                            | 27 |

| 3.2 Multiple-Level Clustering                                       | 29 |

| 3.2.1 Description of Algorithm                                      | 29 |

| 3.2.2 Clustering Example                                            | 30 |

| 3.2.3 Complexity of Clustering                                      | 32 |

| 3.3 Placement of Clusters at Each Level                            | 34 |

|--------------------------------------------------------------------|----|

| 3.3.1 Constructive Placement of Clusters                           | 34 |

| 3.3.2 Simulated-Annealing-Based Iterative Improvement of Placement | 36 |

| 3.3.3 Fanout                                                       |    |

| 3.3.4 Complexity of Placement                                      | 40 |

| 3.4 Determination of the Quality-Time Envelope Parameters          | 41 |

| 3.4.1 Cluster Parameter Experiments                                | 41 |

| 3.4.2 Placement Parameter Experiments                              | 43 |

| 3.5 Summary                                                        | 46 |

| Chapter 4 Experimental Results                                     | 47 |

| 4.1 Target FPGA Architecture                                       | 47 |

| 4.2 Benchmark Circuits and CAD Flow                                | 47 |

| 4.3 Basis of Comparison                                            | 48 |

| 4.4 Comparisons Between Ultra-Fast Algorithm and VPR               | 50 |

| 4.5 Wirelength Estimation and Accuracy                             | 58 |

| 4.6 Practical Usage of Ultra-Fast Placement                        | 63 |

| 4.7 Summary                                                        | 66 |

| Chapter 5 Conclusions and Future Work                              | 67 |

| 5.1 Conclusions and Contributions                                  | 67 |

| 5.2 Future Work                                                    | 68 |

| References                                                         | 70 |

## **List of Tables**

| Table 2.1: | Automatic temperature update schedule for VPR. [Betz97]14                |    |

|------------|--------------------------------------------------------------------------|----|

| Table 3.1: | Cluster scores for candidate blocks in example of Figure 3.4             | 32 |

| Table 3.2: | Constructive versus random initial cluster placement                     | 36 |

| Table 3.3: | Effect of starting temperature calculation on annealing for              |    |

|            | MCNC circuit clma.                                                       | 38 |

| Table 4.1: | Comparison between ultra-fast placement tool and VPR for 20 benchmark    |    |

|            | circuits. One set of placement parameters was employed for each tool     |    |

|            | such that their run times were close and they were part of the           |    |

|            | quality-time envelope for their respective tools.                        | 55 |

| Table 4.2: | Comparison between ultra-fast placement tool and VPR across              |    |

|            | 20 circuits for very short run times                                     | 56 |

| Table 4.3: | Comparison between ultra-fast placement tool and VPR across              |    |

|            | 20 circuits for longer run times                                         | 57 |

| Table 4.4: | Quality of wirelength prediction capability of ultra-fast placement tool |    |

|            | using placement data from Table 4.1 (mean run time = 11.4 seconds)       | 61 |

| Table 4.5: | Quality of wirelength prediction capability of ultra-fast placement tool |    |

|            | using placement data from Table 4.2 (mean run time = 5.5 seconds)        | 62 |

## **List of Figures**

| Figure 2.1: | Simple example of FPGA placement.                                      | 7  |

|-------------|------------------------------------------------------------------------|----|

| Figure 2.2: | Pseudo-code for a basic simulated annealing-based placement            |    |

|             | algorithm. [Sech85] [Betz98]                                           | 9  |

| Figure 3.1: | High-level view of fast placement algorithm.                           | 28 |

| Figure 3.2: | 2: Abstract view of multi-level clustering and placement               |    |

| Figure 3.3: | 3: Pseudo-code for multi-level clustering algorithm                    |    |

| Figure 3.4: | 4: Clustering example                                                  |    |

| Figure 3.5: | Graph of percentage of total flat nets absorbed versus cluster size    |    |

|             | for one level of clustering on MCNC circuit frisc (3692 blocks)        | 33 |

| Figure 3.6: | Pseudo-code for constructive cluster or intra-cluster placement        | 35 |

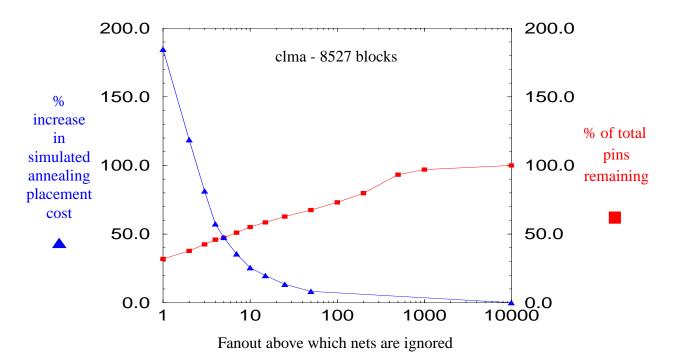

| Figure 3.7: | Graphs of placement cost degradation and percentage of total flat pins |    |

|             | remaining after nets above threshold ignored, each versus fanout       |    |

|             | threshold for MCNC circuit clma.                                       | 40 |

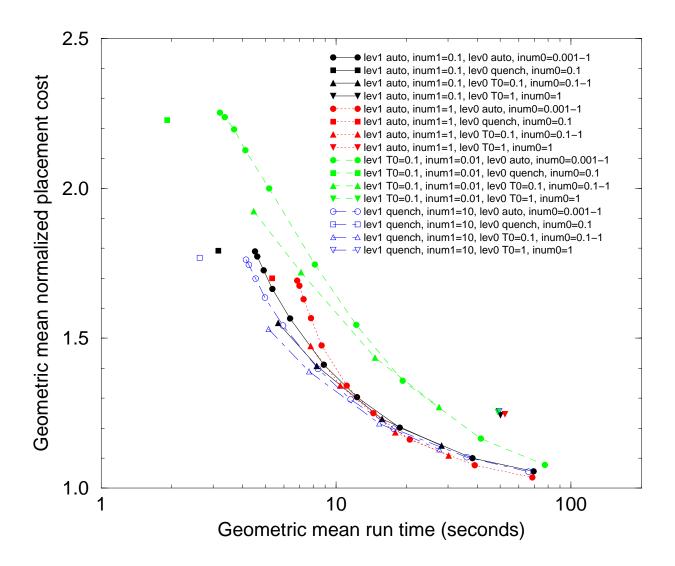

| Figure 3.8: | Placement quality-time plot (20 circuit average) for ultra-fast        |    |

|             | placement tool using different combinations of annealing schedules on  |    |

|             | 1-level, size-64 clustered circuits.                                   | 42 |

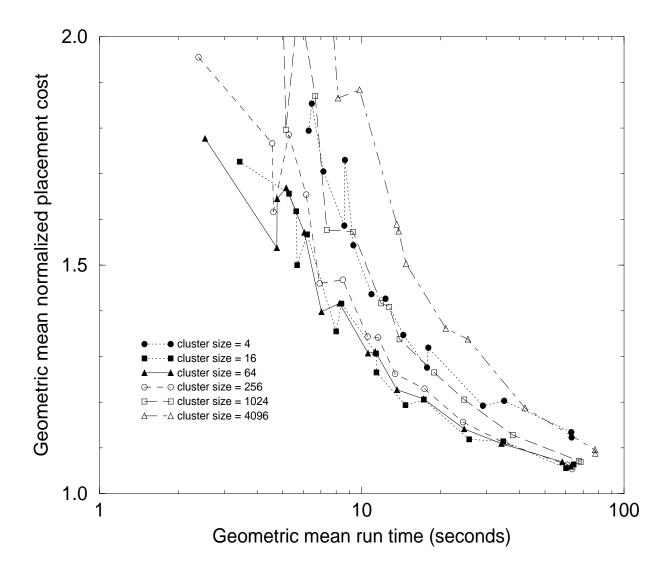

| Figure 3.9: | Placement quality-time curves (20 circuit average) for ultra-fast      |    |

|             | placement tool using a sample of annealing parameters and varying      |    |

|             | 1-level cluster sizes from 4 to 4096.                                  | 43 |

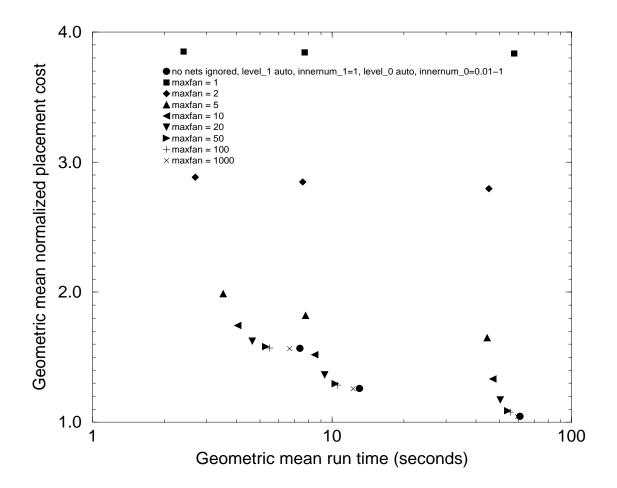

| Figure 3.10 | : Placement quality-time plot (20 circuit average) for ultra-fast      |    |

|             | placement tool using different fanout thresholds above which nets are  |    |

|             | ignored on circuits with fixed cluster and placement parameters.       | 45 |

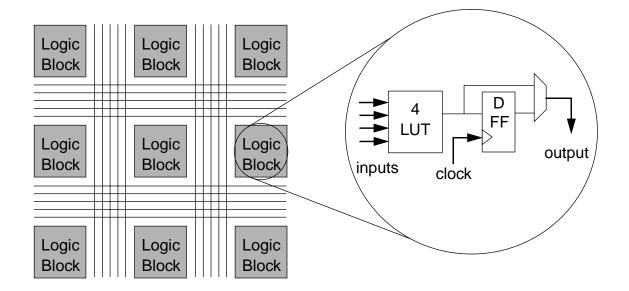

| Figure 4.1: | Island-style FPGA architecture and basic logic block contents          | 48 |

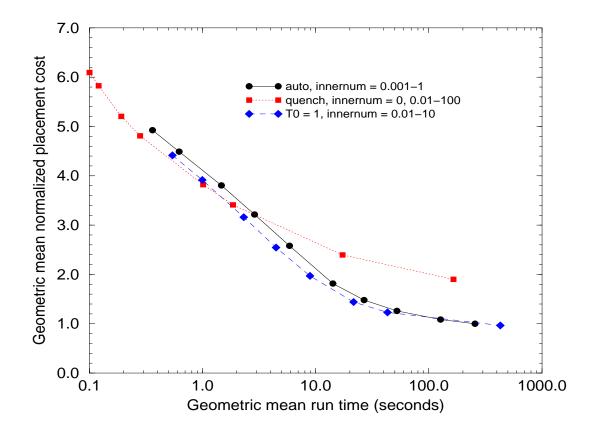

| Figure 4.2: | VPR placement quality-time trade-off (20 circuit average) using        |    |

|             | annealing schedules that form the envelope                             | 50 |

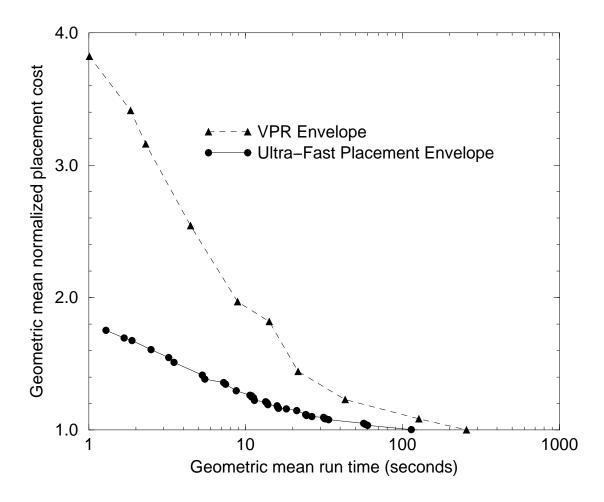

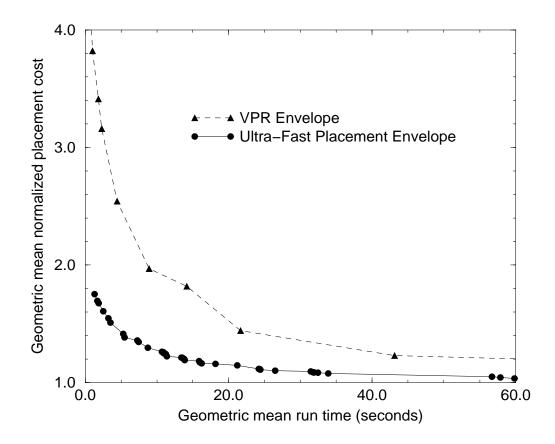

| Figure 4.3: | Placement quality-time envelope curves (20 circuit average) for VPR    |    |

|             | and new ultra-fast placement tool.                                     | 51 |

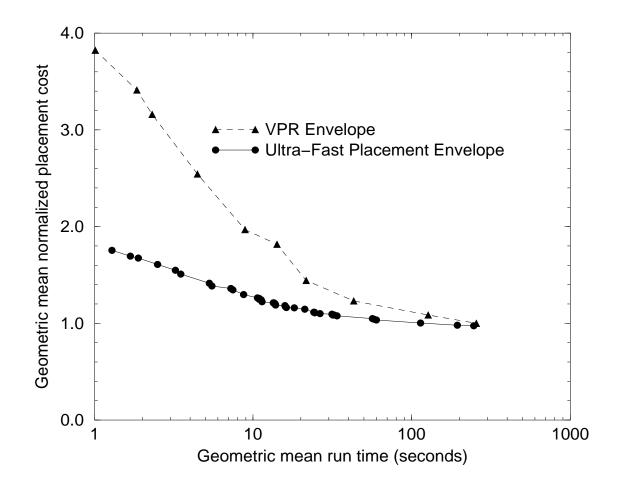

| Figure 4.4: | Placement quality-time envelope curves (20 circuit average) for VPR    |    |

|-------------|------------------------------------------------------------------------|----|

|             | and new ultra-fast placement tool, highlighting the point at which the |    |

|             | curves meet                                                            | 52 |

| Figure 4.5: | Placement quality versus time envelope curves (20 circuit average)     |    |

|             | for VPR and new ultra-fast placement tool (linear scale).              | 53 |

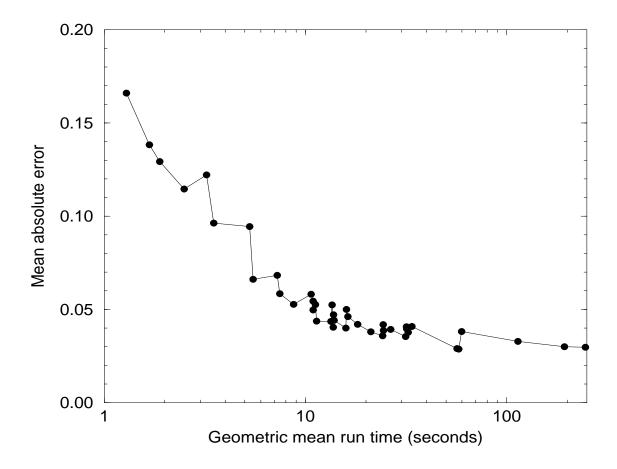

| Figure 4.6: | Mean absolute difference in wirelength (between mean wirelength        |    |

|             | and individual circuit results) versus mean run time for parameters    |    |

|             | forming ultra-fast placement tool envelope.                            | 59 |

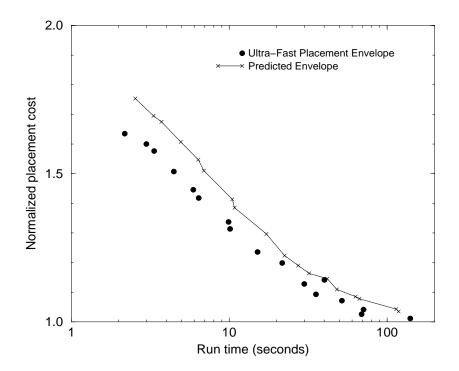

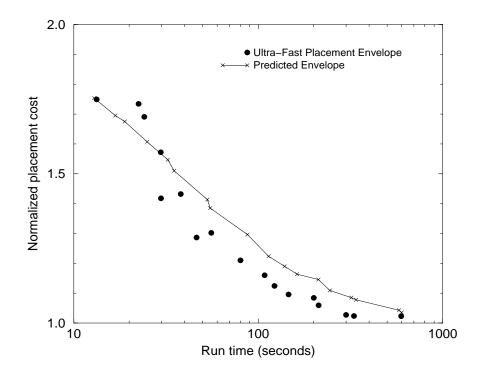

| Figure 4.7: | Comparison of predicted ultra-fast placement quality versus time       |    |

|             | envelope with actual envelope for MCNC circuit clma                    |    |

|             | (8383 logic blocks)                                                    | 64 |

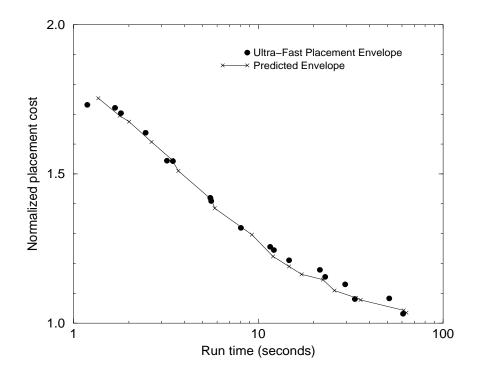

| Figure 4.8: | Comparison of predicted ultra-fast placement envelope with actual      |    |

|             | envelope for circuit marb (5535 logic blocks).                         | 64 |

| Figure 4.9: | Comparison of predicted ultra-fast placement envelope with actual      |    |

|             | envelope for synthetic circuit beast20k (19600 logic blocks)           | 65 |

## Chapter 1 Introduction

## **1.1 Motivation**

Field-programmable gate arrays (FPGAs) have been highly successful because they can realize any digital circuit simply by the specification of the millions of bits that control a sea of programmable logic and interconnect. The ability of an FPGA to be re-programmable within a system offers designers the ability to implement different circuits, fix errors in circuits, or add new features to existing circuits in a matter of seconds. This programmability gives FPGAs significant advantages over customized application-specific integrated circuits (ASICs): flexibility, quick time-to-market, zero non-recurring engineering costs, and easier debugging. All these benefits do come at a price, however, in that circuits realized on an FPGA typically occupy at least ten times the area and operate at least three times slower than their ASIC counterparts [Brow92].

A set of automated computer-aided design (CAD) tools is necessary in order to generate an FPGA programming bitstream that implements a desired circuit. These software tools first take the circuit description (where the circuit is specified in a hardware description language such as VHDL, or in schematic form) through the synthesis stage, where the circuit is represented as a netlist of technology-mapped logic blocks and connections. Following this, the CAD tools perform the placement and routing steps. During placement, the logic blocks implementing the circuit are assigned to physical locations on the FPGA such that the wiring area is minimized. In routing, the point-to-point connections are made by specifying which physical switches are acti-

vated in the programmable wiring such that full routability is achieved and circuit speed is maximized. This can be used to generate the programming bitstream. The complete set of tasks the CAD tools perform to translate a circuit description into a programming bitstream is known as FPGA compilation.

One key advantage of FPGAs over mask-programmable gate arrays and ASICs is that they provide quick turnaround times for circuit designers between the conception of the circuit and its implementation on a chip. However, this rapid prototyping advantage has been reduced as the capacities of these programmable devices grow. While current CAD algorithms provide high-quality solutions, they require a great deal of CPU time, and the compilation times for large circuits are growing more rapidly than the available computer power. This adversely impacts: hardware designers, who must wait longer to map their designs to FPGAs; logic emulation system users, who must compile hundreds of FPGAs at a time [Quic98]; and FPGA-based custom computing machine users, who desire compilation times similar to those of a microprocessor.

Place-and-route times for large FPGAs at present (those with approximately 5000 lookuptable (LUT) / flip-flop pairs and higher) can last many hours on a modern processor, and there is no guarantee of successful completion. For example, an 8383 LUT circuit (approximately 100,000 gates) requires almost 1.2 hours for placement and routing using the Xilinx M1 CAD tools (version 4.1.2) [Xili98] on a 300 MHz Sun UltraSPARC workstation [Swar98b]. For a subset of designers, these prohibitively long compile times may nullify any gains that had been realized by using FPGAs in the first place. Since the time-to-market advantage and ability to create rapid prototypes are severely compromised, some users may opt to return to the world of maskprogrammed gate arrays (MPGAs) or standard cells. With million-gate FPGAs on the horizon, it is imperative to design FPGA compilation tools that will scale well with device sizes, and provide an acceptable trade-off between quality<sup>1</sup> and compile time [Rose97]. Only then will the characteristic FPGA benefits of fast design and manufacturing cycles be maintained. We contend that there are users who are willing to sacrifice circuit quality for speed of compilation.

<sup>1.</sup> We define quality as the wirelength required by the circuit or the speed at which the circuit can operate when mapped to the FPGA. Greater wirelength will require the use of a larger FPGA or the use of more resources on a given FPGA than is otherwise necessary.

These trends provide a compelling motive to explore methods for fast compilation for FPGAs. In this thesis, we shall focus on the placement phase of the FPGA compile process and present an ultra-fast placement tool that aims to minimize area [Sank99]. Although a fast timing-driven placement tool should also seek to minimize circuit delay, we believe that area-based minimization is a prudent first step. Furthermore, while top-down partitioning, floorplanning, macro-based placement, and incremental placement methods may be cited as alternate approaches to mitigating the long compile times of the next generation of large FPGAs, we contend that there will always be a need for a fast, flat placement tool.

### **1.2 Goals and Scenarios**

There are two main objectives of our fast placement tool: 1) to provide placements very quickly with the minimum amount of degradation in circuit quality, and 2) to provide very fast predictions as feedback to the user based on the fast placements generated.

In order to precisely articulate what we mean by fast placement, we have set the following goal for our placement tool: be able to perform a full placement of a 100,000-gate circuit in 10 seconds on a modern CPU. We believe this goal is justifiable: extremely fast placement is essential if it is to be used as a guide within upstream CAD tools, or in emulation systems and reconfigurable computing applications, or to satisfy impatient hardware designers. More importantly, we wish to ensure that the running time varies linearly with the size of circuit, and has a small proportionality constant. This is crucial because as long as our algorithms are of linear complexity or close to that, the same technology advancements that permit FPGA devices to become more dense also increase processor speeds. Therefore, our algorithm will scale well.

A key element of our fast placement tool is that we offer a tunable "knob" that allows the user to smoothly trade quality for compile time. So, not only do we aim to provide more area-efficient placements in very short run times, we also aim to provide high-quality placements given longer run times. We further expect that FPGA users will benefit from being able to run a quick placement of their circuit, rather than wait for a complete high-quality placement, to ascertain what size FPGA device to purchase to implement their design.

In addition, since some placement problems may be extremely difficult (the circuit barely fits onto the device, and the CAD tools need a great deal of time to generate a usable placement) or impossible (the circuit cannot fit onto the device), we believe it is important to quickly supply the user with the predicted area versus compile time trade-off for a circuit of similar size.

3

We envision three scenarios in which fast compile would be used, once a user has designed a circuit and targeted an FPGA of a specific size:

- 1. If the user explicitly states a compile time restriction, then the fast CAD tools should estimate how much extra space -- or how much larger a device -- will be necessary for the design to be placed in the desired running time, and produce the placement.

- 2. Alternatively, if the user explicitly states that the design must fit into the desired FPGA, then the fast tools can inform the user of one of the following: that the circuit can be placed and routed quickly (and provide the placement and routing files), that the circuit will be placed and routed given more time, or that the task is impossible. The work by Swartz et al. offers a method for making the "fit/no-fit" prediction *given a placement* and its total wirelength [Swar98a].

- 3. The user is supplied with an area versus compile-time trade-off curve and selects the point appropriate to his goals. In this case, there must be sufficient free space in the FPGA. Those users willing to sacrifice circuit area for a faster compile time, via the tunable "knob", can accommodate the increased area in several ways: they can reduce the complexity of a single design by partitioning the circuit onto multiple FPGAs, or can select an FPGA with greater logic capacity. They can also eliminate part of the circuit by reducing the amount of parallelism in the hardware.

Our second goal is to leverage our fast placement tool to provide fast feedback to the user in a number of areas. We provide, for a given compile time restriction, an estimate of how much extra area the circuit will require with that much time devoted to placement. Conversely, for a given area restriction, we provide an estimate of the shortest amount of time needed to produce a placement that will fit. Furthermore, we furnish, in that short amount of time, an estimate of what the wirelength would be if we allowed the placement tool to run without a compile time restriction and try to attain maximum quality. In so doing, we can quickly supply to Swartz' prediction tool [Swar98a] a rough idea of what the final best placement will be, which can then be used to inform the user quickly and reliably of whether or not the circuit will fit onto the targeted FPGA. This fast estimation of high-quality wirelength, as well as the ultra-fast placement, may be exploited by the CAD tools that precede the placement stage to quickly gauge what the circuit will look like after placement. These are all useful features, since some FPGA users bemoan the fact that many industry FPGA CAD tools do not provide adequate predictability with respect to area and speed.

4

## **1.3 Research Approach**

Our experimental research methodology involves first examining an existing academic FPGA CAD tool, VPR [Betz97], which is known to provide high-quality placement and routing solutions over a large suite of benchmark circuits in a reasonable amount of time. Having determined how well VPR performs over a series of different run times for a set of large circuits from a variety of sources, we create a fast placement algorithm that can be incorporated into VPR's infrastructure. In this way, we can make a fair evaluation of how well our new placement tool performs with respect to both run time and area compared to an existing tool on the same platform, with the same set of large benchmark circuits and the same physical FPGA architecture. We then examine the influence of the various enhancements to the placement algorithm that make it "ultra-fast", and make some empirical observations. We also offer some insight into the fast prediction of high-quality wirelength and its accuracy, given a fast placement, and how this is valuable feedback to the user. Finally, we explore simple methods to predict the area versus compile time relationship of a circuit before it is placed, and then invoke the ultra-fast placement algorithm with appropriate automatically generated parameters to meet either a compile time or an area restriction.

## **1.4 Thesis Organization**

This thesis is organized as follows: Chapter 2 presents some of the previous work done in developing and applying VLSI placement algorithms for FPGAs, although little of this work is primarily targeted towards our stated goal of high-speed compilation. We also discuss some of the prior work conducted in the related area of clustering, as well as the recent work accomplished in algorithms and tools targeted for fast FPGA compilation. In Chapter 3, we describe the details of our ultra-fast placement algorithm. In Chapter 4, we offer a variety of results obtained from running our tool on a suite of large benchmark circuits, using a simple and general FPGA architecture. We provide a direct comparison between our tool and a known high-quality placement tool with respect to run time and area, and present results of our fast wirelength prediction scheme. Finally, Chapter 5 highlights some of the key conclusions of this work and proposes directions for future research in this area.

# Chapter 2 Background and Previous Work

In this chapter, a precise definition of the placement problem for FPGAs is provided, followed by a brief description of some of the relevant previous work in this area. This background material is divided into sections covering general VLSI placement algorithms, the use of clustering algorithms to reduce problem complexity, and algorithms specifically designed to address the issue of fast compile for FPGAs.

## 2.1 Definition of FPGA Placement Problem

In the physical layout stage of circuit synthesis, placement follows high-level design, technology-independent logic optimization, and technology mapping to a set of basic blocks, but precedes the routing stage where actual interconnections are made between blocks. The basic placement problem for FPGAs begins with a technology-mapped netlist of logic blocks<sup>1</sup>, input and output (I/O) pads, and their interconnections. The result of placement is an assignment of the blocks and pads to specific physical locations of the FPGA that minimizes a specific cost function [Brow92]. A logic block is the basic unit of an FPGA that performs a specified logic function. A netlist is a hypergraph representation of a circuit, where each vertex represents a circuit element (block), and each hyperedge, or net, represents a wire that connects a set of blocks together. A pad is an I/O block that is the physical interface between the circuit and the outside world. Placement

<sup>1.</sup> For this thesis, a logic block will be one 4-input lookup table (4-LUT) and one D flip-flop.

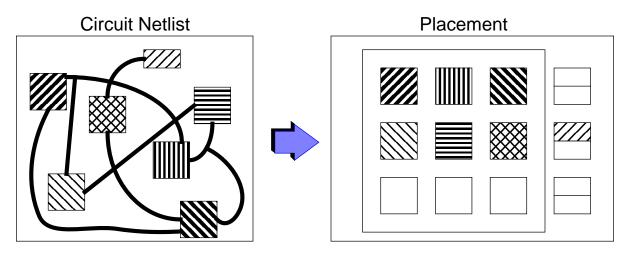

refers to the mapping of the circuit elements in the netlist onto the circuit elements in the physical architecture of the target device [Leng90]. In the specific case of FPGA placement, it is a mapping of blocks and pads in the circuit netlist to the blocks and pads arranged on the physical FPGA array, as shown in Figure 2.1.

Figure 2.1: Simple example of FPGA placement.

More formally, the FPGA placement problem can be expressed as [Leng90]:

- Given: a hypergraph G = (V, E) representing the circuit, where V is the set of vertices (blocks), and E is the set of edges (nets), with edge costs w(e) ∈ R<sub>+</sub> for each e ∈ E;

|V| = n; an FPGA grid of size r×s, where r, s ∈ N, and r ⋅ s ≥ n.

- Find: all placements -- mappings p: V → [1, r] × [1, s] of blocks to block locations on the FPGA grid.

- Minimize: a cost function *c*(*p*).

Since we have stated our ultra-fast placement goal to be to provide an area-efficient placement very quickly, we will attempt to minimize the total wirelength (length of routing wire) required to map the circuit to the FPGA. This is because the cost of the device is proportional to the amount of silicon required to implement it. We can minimize the amount of silicon required (and thus the device cost) by minimizing the area required to wire the circuit components together. Since this total wiring area is only known after the routing stage, an effective estimator is needed at the preceding placement stage, and estimated total wirelength has been shown to be

suitable [Leng90]. Other cost functions that have been used as placement quality metrics include circuit delay and wiring density. The basic placement problem is known to be NP-hard, and therefore many heuristics have been employed [Leng90]. The following section describes some of these heuristics.

## 2.2 Placement Algorithms

Surveys of VLSI placement algorithms are offered in [Shah91] and [Hana72], which describe three main varieties that are currently most popular: 1) Min-cut, or partitioning-based placement algorithms [Dunl85] [Huan97]; 2) Analytical placement algorithms that use quadratic programming [Klei91] [Sigl91] [Alpe97a] [Alpe97b], some of which incorporate iterative improvement [Doll91]; 3) Simulated-annealing-based placement algorithms [Kirk83] [Sech85] [Sech88] [Sun95] [Betz97] [Sarr97]. Previous simulated-annealing-based placement tools have achieved similar or higher quality solutions compared to the other types of placement algorithms, though in some cases, with longer execution times. Consequently, our ultra-fast placement algorithm is based on simulated annealing, and its performance is measured against another known high-quality simulated-annealing implementation. For this reason, this section focuses on simulated-annealing-based placement algorithms.

#### 2.2.1 TimberWolf

TimberWolf [Sech85] [Sech88] is an integrated set of placement and routing tools that provided the first simulated-annealing-based placement algorithms targeting standard cells, macro/ custom cells, and gate arrays. The basic simulated annealing algorithm proposed in [Kirk83] was adapted to explore a number of different placement configurations stochastically to minimize a cost function that estimates overall wiring area. Figure 2.2 shows the pseudo-code for the simulated annealing algorithm, and [Sech85] contains a detailed description of the basic algorithm and the various cost functions used for the different types of placement problems.

The central idea of the algorithm is the notion that the exploration of numerous placement configurations is guided by a parameter, T (temperature), that determines the probability of whether configurations that reduce the quality of the placement will be accepted in the process of searching through different placements. This temperature value is gradually reduced as the search space is explored. Given a random initial placement, a source module is chosen randomly (either a cell or an I/O pad). Then, a target location is chosen at random for this module such that it lies

X = Initial\_Random\_Placement();  $T = Set_Initial_Temperature(); /* T=T_0 */$  $D_{limit} = Set_Initial_Range_Limit(); /* D_{limit} = whole chip */$ while (Exit\_Criterion() == false) { /\* annealing not done yet \*/ while (Inner\_Loop\_Criterion() == false) { /\* work per temperature not done yet \*/ X<sub>new</sub> = Generate\_Move(X, D<sub>limit</sub>); /\* returns a new configuration generated incrementally from previous one \*/ /\* by random pairwise exchange or translation within range limit \*/  $\Delta C = Cost(X_{new}) - Cost(X); /* calculate change in cost */$ r = Get Random Number(0,1);/\* r = random number uniformly distributed between 0 and 1 \*/ if  $(r < e^{-\Delta C/T})$  $X = X_{new}$ ; /\* update current placement \*/ /\* always accept move (p=1) if it improves placement ( $\Delta C < 0$ ) \*/ /\* accept "bad" moves ( $\Delta C > 0$ ) with probability  $p = e^{-\Delta C/T} */$ /\* when T is large, all bad moves likely to be accepted, \*/ /\* when T is small, only bad moves with small  $\Delta C$  likely to be accepted \*/ } /\* end inner loop \*/ /\* exploration at current temperature complete \*/ T = Update\_Temperature( $\alpha$ , T); /\* T =  $\alpha$ T \*/ D<sub>limit</sub> = Update\_Range\_Limit(D<sub>limit</sub>); } /\* end outer loop \*/ /\* annealing complete, X = final placement solution \*/

Figure 2.2: Pseudo-code for a basic simulated annealing-based placement algorithm. [Sech85] [Betz98]

within the displacement range specified by a range limit mechanism, and the target can house the same type of module. If that target location is occupied, then the target module is swapped with the source module (pairwise interchange) and the cost of the resulting placement is evaluated. If the target location is originally empty, then the cost of the new placement with only the source module displaced to the target location (single block translation) is evaluated. In either case, if the new cost is less than the cost of the previous undisturbed placement, the move is accepted. If the new cost is more, then the move is only accepted with probability  $e^{-\Delta C/T}$ , where  $\Delta C$  is the change in placement cost due to the move or swap, and *T* is the current temperature. A large value of *T* is used at the beginning, meaning that almost all moves, irrespective of cost, are accepted. As the placement quality improves with the accumulation of moves, the temperature is gradually

reduced, making it less likely that moves that degrade the placement will be accepted. Eventually, the value of T is so low that only moves which improve the placement quality are accepted, making the heuristic greedy at that point. The parameter T is what permits probabilistic hill-climbing to take place and helps the placement solution avoid being caught in local minima.

The rate at which the temperature is reduced (called the temperature update factor,  $\alpha$ ), the number of configurations to explore at each temperature (known as the inner loop criterion, or *InnerNum*), the exit criterion by which the annealing algorithm terminates, and the behaviour of the range limiting mechanism are all crucial details that are specified by an *annealing schedule*. In TimberWolf, the value of  $\alpha$  starts at 0.8, is gradually increased to 0.95, and gradually decreased back to 0.8 over the course of the entire anneal. This is to ensure that for the portions of the anneal where the cost function is decreasing rapidly, the configuration space is explored more slowly and thoroughly. The number of moves generated per temperature is set to 20-100 times the number of modules in the circuit. The range limit mechanism that sets bounds on the displacement of a module during a move or swap is adjusted so that it is the entire chip at the outset, and as *T* decreases, so does the window of permissible target locations. Finally, the annealer terminates when the cost function over the last three temperatures is found to be unchanging.

The original cost function used for standard cell placement consists of three components: 1) the total estimated wirelength (*W*), which is computed as the sum over all nets of the half-perimeter of the bounding box that encompasses all the pins on each net; 2) a penalty function ( $P_O$ ) for any overlap between cells; 3) a penalty function ( $P_R$ ) for row length mismatches, which ensures that the lengths of the rows of cells do not vary considerably from each other. The cost function can be expressed as:

$$C = W + \mu P_O + \lambda P_R \tag{2.1}$$

The two penalty components (and their scaling factors,  $\mu$  and  $\lambda$ ) do not arise for FPGAs since all logic blocks are of equal size and shape, and logic blocks are only allowed to swap with other logic blocks, and I/O pads are allowed to swap only with other pads.

#### 2.2.2 Hierarchical Clustering and Annealing

An innovative hierarchical clustering and placement algorithm is proposed in [Sun95] and is incorporated into an updated version of TimberWolf (TimberWolfSC v7.0). As an improvement to the previous cost function in TimberWolf, the penalty functions are eliminated, and only the total wirelength term remains. If a move potentially violates a row length limit, it is discarded. If a move is accepted, cells in the affected rows are shifted to prevent any cell overlap. Thus, every placement generated is a feasible one. The revised wirelength-based cost function is an incremental one keeping track of the change in placement cost ( $\Delta C$ ), and has two components: 1) the change in net lengths ( $\Delta W$ ) for those nets connected to the cell or cells that were moved or swapped; 2) the change in net lengths ( $\Delta W_S$ ) for those nets connected to cells in the affected rows that need to be shifted as a result of the move or swap. The former component,  $\Delta W$ , is computed exactly, while the latter,  $\Delta W_S$ , is estimated, but in both cases the computation is fast. The revised cost function can be written as:

$$\Delta C = \Delta W + \Delta W_{\rm s} \tag{2.2}$$

The hierarchical placement methodology consists of clustering and simulated-annealing phases, and it proceeds as follows: first, the original, large, flat netlist is condensed using two levels of clustering, the details of which will be covered in Section 2.3.2. The purpose of this clustering is to reduce the complexity of the circuit so that it is easier to place. It tries to group those cells that will eventually be close to each other in the final placement, and collapses as many flat nets as possible into the clusters while keeping the size of the clusters the same.

Following this bottom-up clustering, the above simulated annealing algorithm is employed to do a top-down placement of the various levels of netlists. The two resulting clustered netlists are subjected to a 3-stage annealing schedule: in the first stage, a high temperature anneal is performed on the top-level netlist of clusters for the first 50% of the total number of moves that are attempted. After the top-level clusters are decomposed into first-level clusters, each first-level cluster is randomly placed within the boundaries laid out by the top-level cluster in which it was contained. Then, the next lower level (first level) of clusters are annealed from 50% to 70% of the total number of moves. Upon decomposing the first-level clusters and placing the original flat

cells within the first-level cluster boundaries, the final annealing stage is conducted, occupying the final 30% of all the moves. In each of the latter two stages, the cells or clusters are permitted to move across the cluster boundaries specified from the previous higher level, and the initial temperature at each stage is computed as:

$$T_0 = \frac{-\overline{\Delta W}}{\log(R_{accept})} \tag{2.3}$$

where  $\overline{\Delta W}$  is the average change in wirelength and  $R_{accept}$  is the desired ratio of accepted moves to attempted moves. Over the whole placement process, all timing requirements (restrictions on circuit delay) are satisfied as well.

The combination of hierarchical clustering and annealing serves to speed up the entire placement process, with run times that are between 3.6 and 7.5 times faster than those obtained using the previous version of the tool, TimberWolfSC v6.0. The average reduction in wirelength between TimberWolfSC v7.0 and TimberWolfSC v6.0 is 12%. When compared to the quadratic placement tool Gordian/Domino, the placements produced by TimberWolfSC v7.0 have 8% less wirelength on average, and require between 3% and 26% less run time on circuits with more than 5000 cells.

In [Roy93], hierarchical clustering and annealing are utilized to perform FPGA placement. A clustering and annealing-based, timing-driven, N-way chip partitioner is used as a global placement tool for a single-chip FPGA (N=1) with emphasis on both wirelength and execution time. A bottom-up hierarchical clustering is used to merge those modules that form "natural" clusters (dense subgraphs, in the accumulative weighted graph used to represent the circuit netlist). Then, the clusters are refined through an adaptive technique where clusters are merged so that small nets (2-pin nets, typically) are collapsed and the fanouts of large nets are reduced. This means the total number of nets in the clustered netlist is reduced and the average fanout of the remaining intercluster nets is reduced. These both assist in speeding up the annealing-based partitioning/placement.

Once the physical chip is partitioned into *N* sub-chips, the core is divided into a grid of bins, to make the wirelength calculation more accurate. The clusters of modules are already built, so the simulated-annealing-based *N*-way partitioner is invoked. The clusters are moved from bin to bin as the annealer progresses, and the location of a cluster is the center of the bin in which it cur-

rently resides. The cost function consists of total weighted wirelength, W, (where wirelength is estimated using the sum across all nets of the half-perimeter bounding box for each net), and a penalty,  $P_t$ , for timing violations (sum of all the penalties over all critical paths specified). The cost function can be written as:

$$C = W + P_t \tag{2.4}$$

For large nets, an incremental net-span updating scheme is used, and since the granularity of the grid is a single bin, and the algorithm operates on clusters of blocks, the updating is simpler and faster than with the flat netlist. Moves are generated as mentioned previously, with the added restriction that roughly the same utilization in each bin (amount of logic clusters per bin) needs to be maintained. Once the annealing-based partitioning phase is complete, the clusters within each of the *N* partitions are decomposed, and detailed placement of the constituent flat modules is performed using a low temperature flat anneal. Compared to an industrial placement tool, this technique reduced the total number of unrouted nets that remain after routing by 90%.

#### 2.2.3 VPR - Versatile Place and Route

In [Betz97] [Betz98], a dynamic adaptive annealing schedule that leads to high-quality placements for FPGA circuits in a reasonable amount of run time is described. It includes some of the features from the work done on annealing schedules by Huang et al. [Huan86], Lam and Delosme [Lam88], and Swartz and Sechen [Swar90], but it also implements a novel temperature update scheme and stopping criterion. The annealing schedule parameters are adjusted automatically depending upon the size of the circuit, and a bounding box wirelength cost function is used with correction factors for multi-terminal nets [Chen94].

The initial temperature is set to 20 times the standard deviation in cost after a set of  $N_{blocks}$  moves are made, where  $N_{blocks}$  is the total number of logic blocks and pads in the circuit. Since the initial placement is a random assignment of logic blocks and pads to the physical array, this ensures that the temperature is high enough that almost all initial moves are accepted. At each temperature,  $InnerNum \cdot N_{blocks}$ <sup>4/3</sup> moves are attempted, where the scaling factor InnerNum has a default value of 10. The temperature is reduced in such a way that if there is little change in cost either due to the acceptance rate being too low (high quality placement already) or too high (poor placement quality), the temperature is reduced by a larger fraction. So, as long as the cost is

changing significantly and a substantial number of moves, but not all, are being accepted, the temperature is reduced more gently, so that this space of placement configurations is explored more thoroughly. Table 2.1 shows how the temperature update factor,  $\alpha$ , is automatically determined according to what the acceptance rate of moves was at the last temperature stage.

| Fraction of Moves Accepted $(R_{accept})$ | Temperature Update Factor ( $\alpha$ ) |

|-------------------------------------------|----------------------------------------|

| $R_{accept} > 0.96$                       | 0.5                                    |

| $0.8 < R_{accept} \le 0.96$               | 0.9                                    |

| $0.15 < R_{accept} \le 0.8$               | 0.95                                   |

| $R_{accept} \le 0.15$                     | 0.8                                    |

Table 2.1: Automatic temperature update schedule for VPR. [Betz97]

A range limiting mechanism is used to maintain a target acceptance rate of 44%. If the acceptance rate falls below 44%, the range within which candidates for pairwise swaps are found is shrunk. Conversely, if the acceptance rate grows beyond 44%, the range is expanded. This is accomplished using the following relationship between the new range limit ( $D_{new\_limit}$ ), the previous range limit ( $D_{old\_limit}$ ), and the previous acceptance ratio,  $R_{accept}$ :

$$D_{new\_limit} = D_{old\_limit} \cdot (1 - 0.44 + R_{accept})$$

(2.5)

Note that if the acceptance ratio is exactly 44%, there is no change in the range limit, and that  $D_{new\_limit}$  is restricted to the range [1, maximum FPGA dimension]. This range limit then gradually shrinks over the course of the anneal from covering the whole chip at the beginning, when the acceptance ratio is typically very high, down to 1 (nearest neighbors) at the end of the anneal when only local refinement is tolerated.

Finally, the annealer terminates when the temperature falls below a certain fraction of the average cost per net. If there are  $N_{nets}$  nets in the circuit, and the average placement cost over all the moves at the current temperature is *Cost*, the annealer exit criterion,  $T_f$ , can then be expressed as:

$$T_f < \frac{0.005 \cdot Cost}{N_{nets}} \tag{2.6}$$

VPR placement parameters that can be specified by the user from the command line include: the initial temperature  $(T_0)$ , the exit temperature  $(T_f)$ , the temperature update factor  $(\alpha)$ , the scaling factor (*InnerNum*) for the number of moves to make at each temperature, and the initial random seed (as long as the same seed for the random number generator is used, the placement algorithm is deterministic). These allow the user to tune the placement tool to achieve different quality versus run time trade-offs for a particular circuit.

VPR also addresses the long execution time of typical simulated annealing implementations by performing fast incremental bounding box updates when evaluating the cost of a placement after a move or swap. For each net, a data structure contains not only the coordinates of the four sides of the net bounding box, it also contains the number of pins on the net that lie on each side. This information is used to determine the new net bounding box after a swap by only examining the pins that moved rather than a brute force calculation for every pin on the affected net.

VPR currently holds the world record among academic FPGA placement and routing tools with the minimum total number of tracks required to place and route a set of standard benchmark circuits [Betz97b].

### 2.2.4 Algorithms Based on Variations of Hierarchical Clustering and Simulated Annealing - NRG and Simulated Quenching

In [Sarr97], the NRG standard cell, row-based placement tool is proposed. It performs in succession a global placement, a detailed placement, and a final refinement, each of which is based on simulated annealing. The main objectives are to reduce the search space of potential placement configurations to obtain higher quality results faster, and to provide a fast prediction of the high-quality placement possible using NRG itself. The placement problem is divided into a global placement phase and a detailed placement phase. The motivation is that a good global placement can assign modules to approximate locations quickly and the detailed placement concerns itself with the exact location and timing of a module, given the constraints set by the global placement.

In the global placement phase, flat modules are assigned to a coarse grid via annealing, where each grid location ("bin") can hold multiple modules. The cost function being minimized includes total bounding box wirelength ( $P_{WIRELENGTH}$ ) and a penalty function ( $P_{GBCD}$ ) to prevent unbalanced numbers of modules in each bin on the global placement grid. So, the cost of a placement *x* is given by:

Background and Previous Work

$$f(x) = P_{WIRELENGTH} + \lambda P_{GBCD}$$

(2.7)

where  $\lambda$  is a scaling factor. The authors argue that this is different from clustering modules in the flat netlist first, even though the goal of problem simplification is the same. They reason that operating on the flat netlist (rather than a netlist of indivisible clusters) provides more flexibility, and that clustering modules takes a local view of the placement problem rather than a global one.

In the detailed placement phase, the global bin assignments from the annealed result of the global placement phase are decomposed into the flat grid. Then, a low temperature annealing schedule is used to perform the detailed placement of the modules, minimizing a cost function consisting of wirelength, overlap penalty, and row penalty. The follow-up refinement phase shifts cells to remove any remaining overlap.

The grid size for the global placement phase is arrived at using a binary search to minimize the difference in wirelength between a very fast global placement and a very fast detailed placement for that grid size. Each phase is sped up by simply reducing the number of moves attempted by the annealer at each temperature. NRG achieves wirelengths that are as good or better than those obtained by the commercial version of TimberWolf for a set of five benchmark circuits. In addition, NRG can be used to quickly obtain an estimate of the wirelength NRG itself can provide when allowed to achieve the highest quality placement. NRG's wirelength predictions are 3 - 20% more than the actual wirelengths from high-quality NRG placements. Finally, the run time of NRG can reduced by up to a factor of two, if a quality degradation of 1 - 3% can be tolerated.

In [Sato97], an iterative, partitioning-based placement algorithm known as "simulated quenching" (SQ) is proposed for linear (1-dimensional) placement problems. Many portions of the algorithm mimic ideas from simulated annealing; the algorithm operates in the following manner:

- "Moves" are generated by partitioning the linear placement of blocks into subgroups using a particular pitch (subgroup size) and a randomly chosen offset;

- A force value for each block in each subgroup is computed based only on the nets that cross subgroups; a force value represents the direction in which moving a block decreases the length of an inter-subgroup net connected to that block. These accumulated force values are then used to sort the blocks within each subgroup.

- This process is repeated multiple times with different partitionings of the netlist, each with the same pitch, but different offsets.

After a number of iterations, the pitch value (subgroup size, p) is reduced according to a predetermined "schedule", p = p - 0.03 \* (p / log<sub>2</sub>p) (this is similar to temperature reduction in simulated annealing), and the entire procedure is repeated until the pitch value falls below 2.

When this method is compared to a pure simulated annealing implementation, similar wirelength results are obtained for a set of very small MCNC benchmark circuits [Yang91], but SQ exhibits superior run time. However, for the MCNC circuit s38417, the SQ algorithm requires 8 hours to reach a stable solution when run on a 166 MHz Hypersparc workstation.

#### 2.2.5 Choice of Starting Temperature for Simulated Annealing

One crucial feature of any automatically-generated, dynamic, and adaptive annealing schedule for a variety of circuits is the choice of the starting temperature,  $T_0$ , for a given placement. The reason is that if the temperature is set too high, subsequent annealing will destroy the existing placement structure, which makes any previous work toward placing the circuit useless. Conversely, if the temperature is set too low, the annealer is unlikely to improve upon the existing placement significantly, as it will be unable to escape local minima.

In [Rose90], a method is proposed to compute a good starting temperature for simulated annealing placements. The idea is that there exists a temperature for a given simulated annealing placement where the placement is in a state of equilibrium. In this state, there is no expected net change in the cost function after a set of moves, which implies that the expected change in placement cost is zero:

$$E(\Delta C) = 0 \tag{2.8}$$

Let  $P(\Delta C)$  be the probability that a move with change in cost  $\Delta C$  is generated from the current placement state. If this distribution is known, then if *N* is the number of moves attempted on the current placement, we can express Equation (2.8) as:

$$E(\Delta C) = \int_{-\infty}^{\infty} (\Delta C \cdot P(\Delta C) \cdot P_{accept}(\Delta C)) \ d\Delta C = 0$$

(2.9)

where  $P_{accept}(\Delta C)$  is the probability that a move with cost  $\Delta C$  is accepted. From Section 2.2.1, we know  $P_{accept}(\Delta C)$  is commonly defined as:

Background and Previous Work

$$P_{accept}(\Delta C) = \begin{cases} e^{(-\Delta C)/T}, & \Delta C > 0\\ 1, & \Delta C \le 0 \end{cases}$$

(2.10)

By substituting Equation (2.10) into Equation (2.9), two separate integrals are obtained:

$$E(\Delta C) = \int_{-\infty}^{0} (\Delta C \cdot P(\Delta C)) \ d\Delta C + \int_{0}^{\infty} (\Delta C \cdot P(\Delta C) \cdot e^{(-\Delta C)/T}) \ d\Delta C = 0$$

(2.11)

So, the equilibrium temperature of a given simulated annealing placement with a known distribution  $P(\Delta C)$  is the temperature  $T = T_{eq}$  for which Equation (2.11) is satisfied.

The process of calculating this equilibrium temperature for a given placement is informally referred to as a "simulated thermometer." In order to implement this temperature measurement scheme to compute the equilibrium temperature for a given placement, a set of *N* discrete samples is used to approximate the continuous distribution of  $\Delta C$  over all moves. This means Equation (2.9) can be written as:

$$E(\Delta C) = \sum_{i=1}^{N} (\Delta C_i \cdot P(\Delta C_i) \cdot P_{accept}(\Delta C_i)) = 0$$

(2.12)

Ideally,  $P(\Delta C_i)$  is measured on a running simulated annealing process while at the equilibrium temperature,  $T_{eq}$ . However, if each move *i* is actually being generated, then the number of moves produced with a change in cost  $\Delta C_i$  will be  $N \cdot P(\Delta C_i)$ . That means moves with a particular change in cost will be generated with about the same frequency as they would appear in the continuous distribution. So, as long as *N* is sufficiently large, the set of sample moves generated will approximate the distribution of  $\Delta C$  over all possible moves, and the  $P(\Delta C_i)$  term in Equation (2.12) is inherent from the move generation and in the calculation of  $E(\Delta C)$ .

The simulated thermometer takes an initial placement of blocks, and performs a large number of moves (*N*), none of which are permitted to change the placement. The change in cost associated with each move *i* is recorded ( $\Delta C_i$ ), as well as whether the move would have been accepted or not, based on Equation (2.10). The expression for  $E(\Delta C)$  in Equation (2.12) is then evaluated, and a binary search over temperature is performed to find the temperature at which the expected value of the overall change in placement cost is zero. When the temperature value,  $T_{eq}$ , that satisfies Equation (2.12) is found, the temperature at which the given placement is in a state of equilibrium is determined, and this is a suitable initial temperature to begin annealing the placement. As the binary search for the equilibrium temperature progresses, only the probability of accepting "bad" moves is affected (moves that increase the placement cost --  $P_{accept}(\Delta C_i)$  for  $\Delta C_i > 0$ ). So, the only portions of Equation (2.12) that need to be recomputed are those for each recorded "bad" move at a particular temperature during the search. This simplifies and speeds up the calculation. It is also important to ensure that enough moves are made to obtain an accurate probability distribution for  $P(\Delta C_i)$ . Between 10,000 and 100,000 moves are recommended [Rose90].

## **2.3** Clustering Algorithms

In this section we discuss the motivation behind using netlist clustering algorithms to speed up heuristics that solve problems such as placement and partitioning, and list some of the cost functions used in the prior research to build good clusters.

#### 2.3.1 Using Clustering to Reduce Problem Complexity

Whether the problem is partitioning or placement, the virtues of using bottom-up netlist clustering are well documented in [Sun95] [Roy93] [Shin93] [Hage97] [Kary97] [Alpe97c]. The primary goal of this clustering is to reduce the problem size so that a smaller and more easily solvable problem is obtained. This assists in decreasing the time required for iterative algorithms to obtain a good solution for the overall problem.

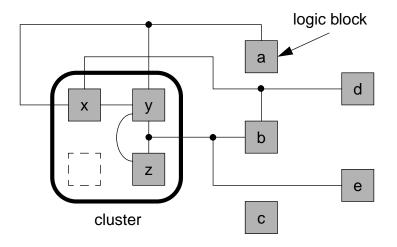

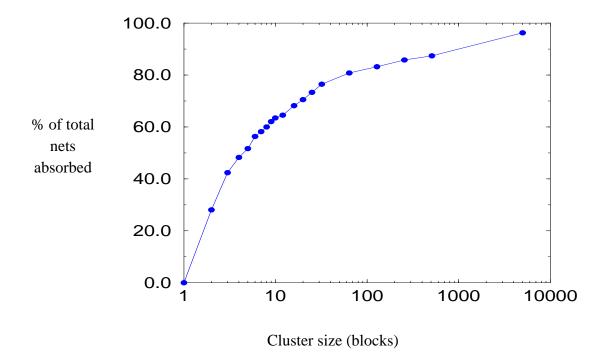

A clustering groups netlist modules into disjoint subsets, known as clusters. When the modules are packed into each cluster, the netlist that is induced is a condensed version of the original problem that may be solved more easily and quickly. This is particularly crucial for iterative algorithms whose performance tend to degrade as the problem size and complexity increase. Hagen and Kahng suggest that the advantage offered by clustering in reducing the problem size permits the algorithm operating on the condensed problem to focus on the most difficult and time-consuming portion [Hage97]. Both [Sun95] and [Roy93] state that through effective netlist clustering, the number of clusters to manipulate, the number of inter-cluster nets and pins, and the average fanout of the remaining nets are all substantially reduced. This can decrease the computation time required by an order of magnitude compared to operating on the original flat netlist. If one level of clustering is insufficient to simplify the complexity of the problem, then additional levels of clustering (hierarchical or multi-level clustering) may be performed until the problem size becomes manageable. With multi-level clustering, the compaction of the original flat netlist can proceed more gently, with progressively smaller clustered netlists being produced at each level of the hierarchy. Intuitively, the benefit of multi-level clustering is that the iterative improvement strategy has more opportunities for refinement. Furthermore, as the refinement moves from coarser to finer levels, the iterative algorithm can avoid bad local minima because of the large steps taken at the highest levels of the hierarchy. The progressively smaller and more detailed steps at the lower levels of the hierarchy enable the algorithm to find good final solutions [Alpe97c].

In the specific case of hierarchical placement, the clustering serves as a bottom-up preprocessing step. A good clustering algorithm should identify those groups of blocks that are tightly coupled in the netlist and will end up being placed in close proximity in the final placement. Even though top-down partitioning achieves the same divide-and-conquer philosophy as clustering (though starting from a global view and working its way down to a local view of the circuit), the growth in circuit size may make this problem prohibitive (this is why clustering is used to simplify large partitioning problems). It is important, however, that the clustering step be fast itself, otherwise the speedup benefits are nullified. As well, the clusters should be built with as uniform a size as possible, since algorithms that swap clusters become less effective when the sizes of the objects vary greatly [Sun95]. Placement algorithms tend to have more success in minimizing the net lengths of low fanout nets rather than high fanout nets [Roy93]. Consequently, creating a hierarchy of clusters that shrinks the problem size, so that the average fanout of a net is reduced, can be advantageous to achieving both good quality and run time.

#### **2.3.2** Cost Functions Used to Build Clusters

In [Sun95], two levels of clustering are performed prior to hierarchical simulated annealingbased placement. A single level of clusters is constructed in linear time based on connectivity, with the clusters having similar size. The cost function is designed so that nets with small fanout are absorbed into a single cluster. These nets are easier to fit in a single cluster than nets of greater fanout. Each net *i* is assigned a weight  $w_i$  that is inversely proportional to its fanout. So, if the set of pins on net *i* is  $F_i$ ,  $w_i = 1/(|F_i| - 1)$ . A tree model for multi-terminal nets is used, which means that an *n*-pin net has *n*-1 edges; if that net spans *m* clusters, then there are *m*-1 inter-cluster edges, and if there are *j* pins of that net contained in a cluster, then that cluster has *j*-1 edges. Let  $B_k$  be the set of all pins contained within cluster *k*. The weight,  $W_k$ , of cluster *k* is then defined as the sum of all the edge weights in that cluster:

$$W_{k} = \sum_{\langle \forall i | (F_{i} \cap B_{k}) \neq \emptyset \rangle} (|F_{i} \cap B_{k}| - 1) \cdot w_{i}$$

(2.13)

The first component of the product term in the summation represents the number of edges of net i that are completely contained within cluster k. Note that if the entire net was absorbed by cluster k (all pins of net i are contained within boundaries of cluster k), the total edge weight due to that net would be 1. Let N be the desired number of clusters to be constructed at a specific level. The objective of the clustering algorithm is to maximize the cost function C below, without violating the constraints on cluster capacity (a minimum and maximum size for clusters at a specific level):

$$C = \sum_{k=1}^{N} W_k \tag{2.14}$$

[Sun95] employs a simulated annealing algorithm to build the clusters while maximizing the above cost function, where blocks are swapped or moved across clusters as long as the blocks have connections in each cluster.

In [Roy93], a bottom-up hierarchical technique is also used to construct clusters for partitioning. An accumulative weighted graph is used to represent the circuit netlist, where each node represents a circuit module, and each edge indicates a net containing those two nodes. An *n*-pin net then results in n(n-1)/2 edges in the complete graph. The clustering targets those nodes in the graph that qualify to be merged with each other. As in [Sun95], each net is weighted by the inverse of its fanout, (1/(n-1)), for an *n*-pin net). All the edges between every pair of nodes in the graph are collapsed into single edges with a total weight equal to the sum of all the edge weights between the same two nodes.

In the first clustering phase, "natural" clusters are constructed from those nodes which are connected by edges that have weight greater than some threshold. This tends to cluster the most dense subgraphs from the weighted graph of the netlist, and higher levels of clustering proceed in the same way with a condensed netlist of clusters and an updated value for the threshold. The second phase of clustering uses an adaptive method to refine the clusters created in the first phase. Its goal is to further simplify the netlist while making sure the sizes of the clusters are approximately equal. Small clusters on 2-pin nets are merged together to form larger clusters, but if there are no such nets remaining, then the smallest cluster on the multi-terminal net with the largest fanout is merged with a given small cluster. In this way, both the total number of nets in the revised netlist is reduced, and the average net fanout of the remaining nets is also reduced. The clustered netlist is then transferred to the partitioning/placement tool.

In [Shin93], a single level of bottom-up clustering is utilized to simplify a partitioning problem, as well as provide a hierarchical partitioning tool with a good initial solution that can be efficiently evaluated. The intuition is that a clustering-based initial partitioning solution is superior to a random solution since the blocks that are merged into clusters should ultimately reside in the same partition.

The clustering process begins by considering each circuit block a cluster itself (cluster size = 1). Let CommonNets(C, D) represent the set of nets common to clusters C and D, Pins(C) and Pins(D) represent the set of pins contained in clusters C and D, respectively, ClusterSize(C, D) be the size of the new cluster formed by merging C and D, and AvgClusterSize be the average size of all the clusters. The "closeness" of two clusters C and D is given by [Shin93]:

$$closeness(C, D) = \frac{|CommonNets(C, D)|}{min(|Pins(C)|, |Pins(D)|)} - \left(\alpha \cdot \frac{ClusterSize(C, D)}{AvgClusterSize}\right)$$

(2.15)

The first component measures the strength of the attraction between the clusters, while the second component is the penalty for creating clusters with unbalanced sizes, whose influence is controlled by the scaling factor,  $\alpha$ . The pairs of clusters with the highest closeness scores are merged until the desired number of clusters is reached. After two clusters are merged, the closeness scores of all the other affected clusters are updated to reflect the change.

Once all the clusters are constructed, the clustered netlist is partitioned multiple times, and the best solution is passed on to the flat partitioner for further refinement. The combined clustering and 2-level partitioning methodology leads to high quality partitioning results in a reasonable execution time.

In [Alpe97c], multi-level clustering is used to simplify the partitioning problem. The various levels of clustered netlists are passed to a hierarchical partitioning tool for repeated partitioning and decomposition of the clusters while maintaining the partitions from the previous higher level of the hierarchy. The clustering at a given level merges 2 blocks (or clusters) at a time in the following manner: an unclustered block w is merged with a given block v if w has the highest connectivity to v, according to the cost function below [Alpe97c]:

$$conn(v,w) = \frac{1}{A(v) \cdot A(w)} \cdot \sum_{e \in \{e \mid (v \in e, w \in e)\}} \frac{1}{|e|}$$

(2.16)

where A(v) and A(w) are the respective areas of blocks v and w, and e represents each net common to both v and w. The (1 / |e|) component reflects that blocks connected to low fanout nets are preferred, and the  $(1 / (A(v) \cdot A(w)))$  term indicates that blocks with smaller areas are preferred for merging to maintain clusters with balanced sizes. If there is no suitable unclustered block w, then block v is assigned to its own separate cluster. Nets with fanout 10 and up are ignored for the purpose of calculating conn(v,w), and the clustering at a given level terminates when a specified fraction of all blocks have been clustered.

## 2.4 Fast Compile Algorithms

While there exists a great deal of previous work on VLSI placement algorithms that can be applied towards FPGAs, and these algorithms succeed to varying degrees in minimizing the wiring area occupied by a circuit, very few of them have as their primary goal the minimization of run time. In this section, we describe some of the recent work dealing with fast compilation for FPGAs.

#### 2.4.1 Lola

Gehring and Ludwig [Gehr98] describe a fast placement tool in the context of a set of integrated CAD tools for the Xilinx XC6200 FPGA architecture. It converts a Lola HDL specification [Wirt96] into an FPGA programming bitstream in the order of seconds. Their constructive and deterministic placement algorithm operates only on a hierarchical description of a circuit that contains regular subcircuits and is represented by parameterized templates. It takes user-specified position hints and proceeds in a bottom-up fashion to place the inner-most subcircuits, and then recursively places the larger array structures and expression trees. Simple heuristics for placing these structures are employed to place the regular bit-sliced designs that often occur in datapath circuits. The designer is permitted to manually intervene to provide hints and feedback to the automatic placer that pre-places parts of the circuit. Since the circuit hierarchy is maintained, the user can easily modify the placement manually or provide further hints to constrain future iterations of the placer. Upon reaching a placement solution, the specific placement information for each subcircuit is passed on to every instance of that template.

The placement algorithm is of linear complexity and is fast - a circuit of 11,748 configurable logic blocks (CLBs) was placed in 33.5 seconds on a 166 MHz Intel Pentium. The Xilinx XC6264 is the target device. The authors admit that their strategy does not lead to dense layouts, and that for larger circuits, manual floorplanning may be required.

#### 2.4.2 GAMA

Callahan et al. [Call98] combine fast placement with module mapping in their GAMA tool. It is used to synthesize bit-sliced datapath circuits quickly by treating the placement and mapping problems jointly as a tree covering problem. A dataflow graph representation of the circuit is split into trees, and a linear-time implementation of bottom-up dynamic programming is used to perform the simultaneous module mapping and relative module placement. While creating a tree covering for a particular module, a linear placement is formed by abutting the module with the best covers of its fanin trees. Modules within a subtree are placed contiguously, and the size of a module's fanin trees are used to estimate routing delays that form part of the cost function used to evaluate different covers and placements. Once placement within a tree is complete, a greedy heuristic is employed to perform the global placement of the trees that seeks to place trees on the critical path close to each other. After post-covering and post-placement local optimizations are made, each module is generated on demand, rather than copying it from a static library of modules with different widths, shapes, and orientations.

By opting to maintain the hierarchical datapath circuit structure, rather than flattening the design to a netlist of gates, the authors are able to exploit specialized features of their target FPGA device architectures, such as fast carry chains. They obtain good results when targeting the Xilinx XC4000 family and explore the trade-off between optimizing for area (minimum number of configurable logic blocks, CLBs, required) and for delay (minimizing critical path delay through the dataflow graph, or minimizing the number of CLBs while meeting a specific timing constraint).

24

The authors admit that only a subset of all possible linear orderings of optimized modules are evaluated, and so an optimal placement cannot be ensured. However, GAMA can be beneficial in situations where placement quality may be sacrificed for compilation time; it can provide a quick initial solution for further iterative refinement or when a fast estimate of placement cost is needed.

#### 2.4.3 Fast Placement for FPGAs via Automatic Floorplanning

In [Tess98], compile-time efficient placement for FPGAs is approached using ASIC floorplanning techniques. By considering portions of the circuit being mapped to the FPGA as preplaced and pre-routed macrocells, the compile times for large designs can be decreased from an hour to mere minutes, although there is both a severe area and circuit speed penalty. Using macros and floorplanning tends to yield a fast placement result, but following it up with some amount of annealing tends to smooth out any congestion and permits better device utilization. Furthermore, if inter-macro routing is not taken into account during the floorplanning stage, this can lead to longer routing times than those obtained by using classical flat place-and-route heuristics due to the increase in total wirelength.

For circuits with an explicit hierarchical structure, an iterative strategy using relative cell placement, cell rotation, and cell mirroring is used to achieve the goal of minimum interconnection wirelength. The method first involves finding optimized layouts for a set of macrocells that will be stored in a library database. Since each macrocell is small, this does not expend much time, and only needs to be done once. The circuit is then recursively bipartitioned using classical algorithms to create a slicing floorplan with minimum cut size, where each leaf in the binary slicing tree is a single macro. Then, floorplan sizing is performed using a bottom-up dynamic programming approach. All feasible shape combinations are evaluated in this traversal from the leaves to the root of the floorplan's slicing tree, and those which consume too much area are pruned. A top-down slicing tree traversal is then performed, and at each level of the traversal, the combination of macrocells that fits the shape constraints laid out in the previous step is chosen such that wirelength is kept at a minimum. At the end of this stage, the floorplan contains a list of macro locations, shapes, and orientations that result in a macrocell placement on the minimum-sized square FPGA that can accommodate it.

### 2.4.4 Fast Routing and Difficulty Prediction

In [Swar98a], the routing phase of the fast FPGA compile is addressed. It is the complement to this work and together they form the Fast Compile Project at the University of Toronto. Swartz et al. present a fast routability-driven FPGA router, and later propose a fast timing-aware router in [Swar98b]. Their enhancements to the basic maze router include using a more aggressive, depth-first search technique to route nets from sources to sinks, the choice of target sinks when routing multi-terminal nets, routing the nets in decreasing order of fanout, and reducing problem complexity by dividing the FPGA into uniformly-sized bins. Another key contribution of this work is the feedback provided to the user of the predicted difficulty of a given routing problem. Given a placement and a target FPGA, the tool estimates the minimum number of tracks per channel required to route the circuit on the given FPGA from the bounding-box wirelength placement cost. It then compares this figure to the actual number of available tracks per channel on the device, and informs the user that either the circuit can be routed quickly, that it can be routed given more time, or that it is unroutable given the current target FPGA.

## 2.5 Summary

In this chapter, we provided definitions for the FPGA placement problem and the ultra-fast placement problem. We then reviewed some of the prior work done in general VLSI placement algorithms, focusing on simulated annealing-based heuristics. We also discussed previous efforts that used clustering to simplify and speed up placement and partitioning problems and the various cost functions employed to build clusters from a flat netlist. Finally, we presented some of the recent work accomplished in creating fast compilation tools for FPGAs. This provides the background information necessary to understand the design details of the ultra-fast placement algorithm, which is described in the next chapter.

## Chapter 3 Ultra-Fast Placement Algorithm

In this chapter, the components of the ultra-fast placement algorithm are described, including the parameters that allow the exchange of wirelength for compile time. We then describe how we determined a stable set of these parameters that give us the best quality-time trade-off.

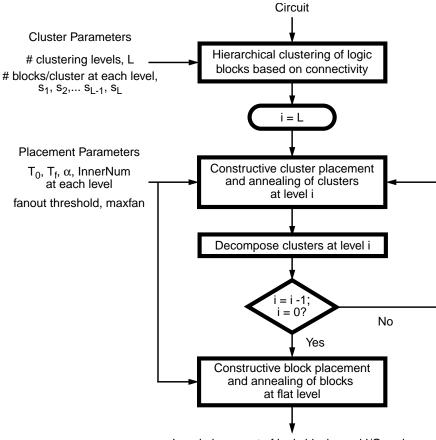

## **3.1** Overview of Approach