# Field-Programmable Gate Array Architectures and Algorithms Optimized for Implementing Datapath Circuits

Andy Gean Ye

November 2004

# Field-Programmable Gate Array Architectures and Algorithms Optimized for Implementing Datapath Circuits

by

# Andy Gean Ye

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy

November 2004

The Edward S. Rogers Sr. Department of

Electrical and Computer Engineering

University of Toronto

Toronto, Ontario, Canada

"We are pattern-seeking animals, the descendents of hominids who were especially dexterous at making causal links between events in nature. The associations were real often enough that the ability became engrained in our neural architecture. Unfortunately, the belief engine sputters occasionally, identifying false patterns as real...

The solution is science, our preeminent pattern-discriminating method and our best hope for detecting a genuine signal within the noise of nature's cacophony."

- "Codified Claptrap," Michael Shermer, Scientific American, June 2003

### **Abstract**

Field-Programmable Gate Arrays (FPGAs) are user-programmable digital devices that provide efficient, yet flexible, implementations of digital circuits. Over the years, the logic capacity of FPGAs has been dramatically increased; and currently they are being used to implement large arithmetic-intensive applications, which contain a greater portion of datapath circuits. Each circuit, constructed out of multiple identical building blocks called bit-slices, has highly regular structures. These regular structures have been routinely exploited to increase speed and area-efficiency in designing custom Application Specific Integrated Circuits (ASIC).

Previous research suggests that the implementation area of datapath circuits on FPGAs can also be significantly reduced by exploiting datapath regularity through an architectural feature called configuration memory sharing (CMS), which takes advantage of datapath regularity by sharing configuration memory bits across, normally independently controlled, reconfigurable FPGA resources. The results of these studies suggest that CMS can reduce the total area required to implement a datapath circuit on FPGA by as much as 50%. They, however, did not take into account detailed implementation issues such as transistor sizing, utilizable regularity in actual datapath circuits, and Computer-Aided Design (CAD) tool efficiencies.

This study is the first major in-depth study on CMS. The study found that when detailed implementation issues are taken into account, the actual achievable area savings can be significant less than the previous estimations — the CMS architecture investigated in this study is only about 10% more area efficient than a comparable conventional and widely studied FPGA architecture for implementing datapath circuits. Furthermore, this increase in area efficiency has a potential speed penalty of around 10%.

To conduct the study, a new area-efficient FPGA architecture is designed along with its supporting CAD tools. The architecture, called Multi-Bit FPGA (MB-FPGA), is the first completely specified FPGA architecture that employs CMS routing resources. This sharing significantly reduces the number of configuration memory bits and consequently increases its area efficiency.

The use of the CMS resources, however, imposes new demands on the traditional FPGA CAD algorithms. As a result, a complete set of CAD tools supporting FPGAs containing CMS resources are proposed and implemented. These tools are designed to extract and utilize datapath regularity for the CMS resources. It is shown that these tools yield excellent results for implementing a set of realistic datapath circuits on the MB-FPGA architecture.

# **Acknowledgements**

I would like to take this opportunity to express my sincere thanks and appreciation to my academic supervisors. Professor Jonathan S. Rose and Professor David M. Lewis have provided continual source of guidance, support, advice, and friendship through out my graduate studies. It has been my privilege to work with these two experienced academics and excellent engineers. They have made my doctoral studies a truly rewarding and unforgettable experience. I would especially like to thank Professor Jonathan S. Rose for taking the extra mile to point out the big pictures in my research and my academic career. I would also like to thank Professor David M. Lewis for all his extremely detailed and insightful technical advice.

My father and mother have always been a constant support throughout my studies and my personal life. Their courage, kindness, hard-working ethics, and constant striving for goodness, have been a great inspiration to me. I am especially inspired by their courage in overcoming almost insurmountable difficulties in immigrating and establishing themselves in Canada. This thesis is as much an achievement of theirs as it is mine.

I would like to thank my academic supervisors, the Natural Sciences and Engineering Research Council, the Ontario Government, Communications and Information Technology Ontario, and Micronet for their financial support.

Finally, I would like to thank all my friends for endless hours of play, insightful discussions, rejuvenating lunch outings, friendship, support, and encouragement. Thank you all!

# TABLE OF CONTENTS

| 1 Introduction                                                 |    |

|----------------------------------------------------------------|----|

| 1.1 Introduction to Field-Programmable Gate Arrays             | 1  |

| 1.2 Thesis Motivation                                          | 2  |

| 1.3 Research Approach                                          | 3  |

| 1.4 Thesis Contribution                                        | 4  |

| 1.4 Thesis Organization                                        | 4  |

|                                                                |    |

| 2 Background                                                   |    |

| 2.1 Introduction                                               | 7  |

| 2.2 FPGA CAD Flow                                              | 7  |

| 2.2.1 Synthesis and Technology Mapping                         | 9  |

| 2.2.1.1 Synopsys FPGA Compiler                                 | 10 |

| 2.2.1.2 Datapath-Oriented Synthesis                            | 11 |

| 2.2.2 Packing                                                  | 12 |

| 2.2.3 Placement and Routing                                    | 13 |

| 2.2.3.1 VPR Placer and Router                                  | 13 |

| The VPR Placer                                                 | 14 |

| The VPR Router                                                 | 14 |

| 2.3 FPGA Architectures                                         | 15 |

| 2.3.1 A Conventional FPGA Architecture                         | 16 |

| 2.3.1.1 Logic Clusters                                         | 16 |

| Local Routing Network                                          | 18 |

| 2.3.1.2 Routing Switches                                       | 19 |

| 2.3.1.3 Routing Channels                                       | 20 |

| 2.3.1.4 Switch Blocks                                          | 22 |

| 2.3.1.5 Input and Output Connection Blocks                     | 24 |

| 2.3.1.6 I/O Blocks                                             | 25 |

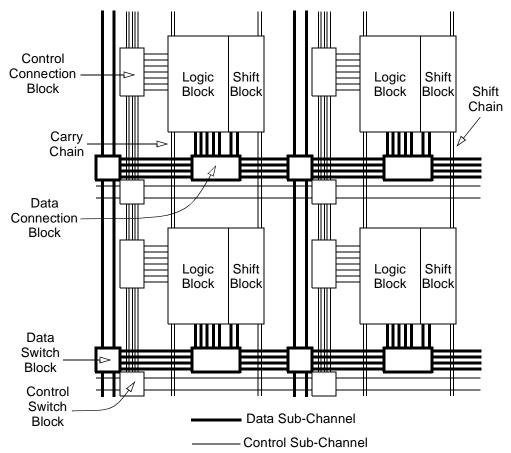

| 2.3.2 DP-FPGA — A Datapath-Oriented FPGA Architecture          | 26 |

| 2.3.2.1 Overview of the Datapath Block                         | 26 |

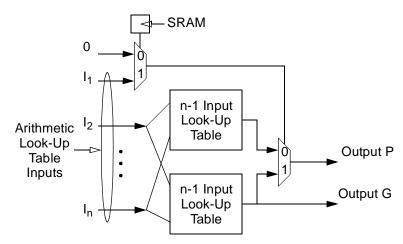

| 2.3.2.2 Arithmetic Look-Up Tables                              | 29 |

| 2.3.2.3 Logic Blocks                                           | 30 |

| Data Connection Blocks                                         | 32 |

| Shift Blocks                                                   | 33 |

| 2.3.4 Other Datapath-Oriented Field-Programmable Architectures | 34 |

| 2.3.4.1 Processor-Based Architectures                          | 35 |

| 2.3.4.2 Static ALU-Based Architectures                         | 37 |

| 2.3.4.3 Dynamic ALU-Based Architectures                        | 38 |

| 2.3.4.4 LUT-Based Architectures                                |    |

| 2.3.4.5 Datapath-Oriented Features on Commercial FPGAs         | 40 |

| 2.3.5 Delay and Area Modeling                                  |    |

| 2.4 Summary                                                    |    |

| 3 A Datapath-Oriented FPGA Architecture                                                                                                                                                                                                                                                                      |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 Introduction                                                                                                                                                                                                                                                                                             | 43  |

| 3.2 Motivation                                                                                                                                                                                                                                                                                               | 45  |

| 3.2.1 Heterogeneous Architecture                                                                                                                                                                                                                                                                             | 45  |

| 3.2.2 Logic Block Efficiency                                                                                                                                                                                                                                                                                 | 46  |

| 3.2.3 Parameterization                                                                                                                                                                                                                                                                                       | 48  |

| 3.3 Design Goals of MB-FPGA                                                                                                                                                                                                                                                                                  | 48  |

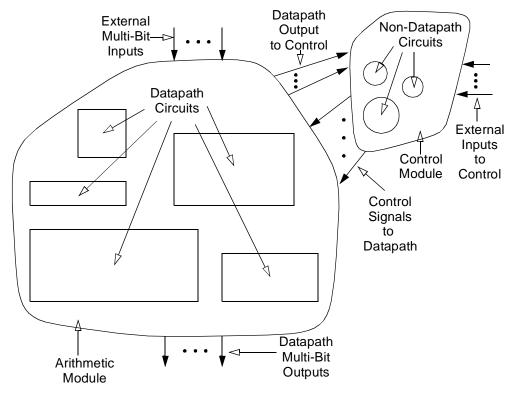

| 3.4 A Model for Arithmetic-Intensive Applications                                                                                                                                                                                                                                                            | 49  |

| 3.5 General Approach and Overall Architectural Description                                                                                                                                                                                                                                                   | 52  |

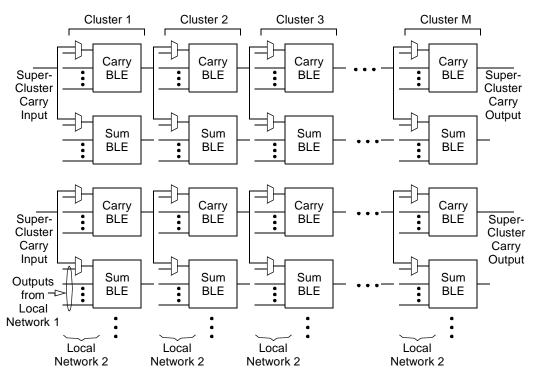

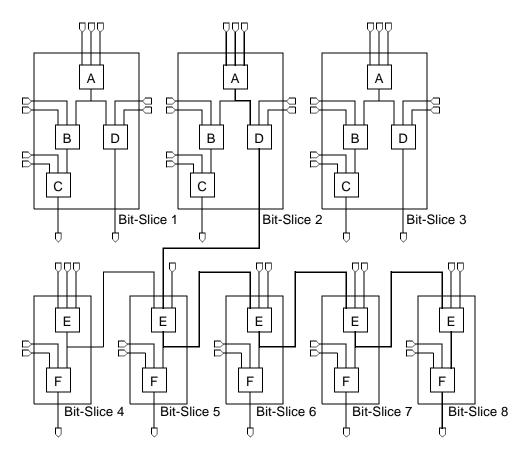

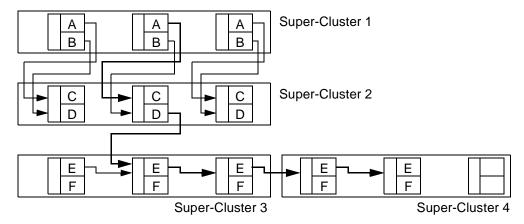

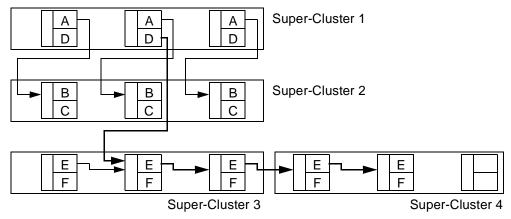

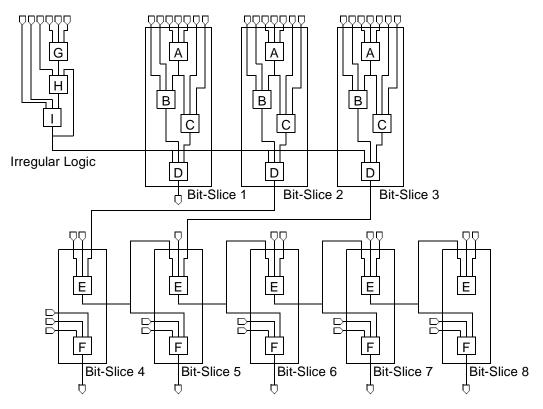

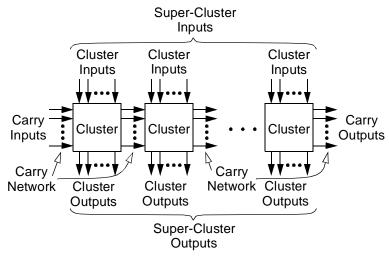

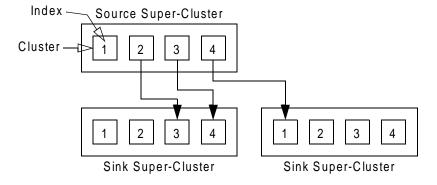

| 3.5.1 Partitioning Datapath Circuits into Super-Clusters                                                                                                                                                                                                                                                     | 52  |

| 3.5.2 Implementing Non-Datapath Circuits on MB-FPGA                                                                                                                                                                                                                                                          | 54  |

| 3.6 The MB-FPGA Architecture                                                                                                                                                                                                                                                                                 | 54  |

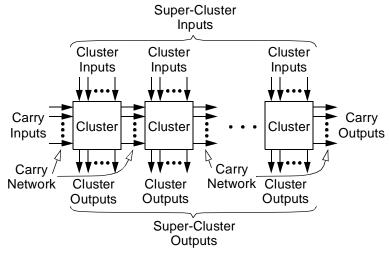

| 3.6.1 Super-Clusters                                                                                                                                                                                                                                                                                         | 55  |

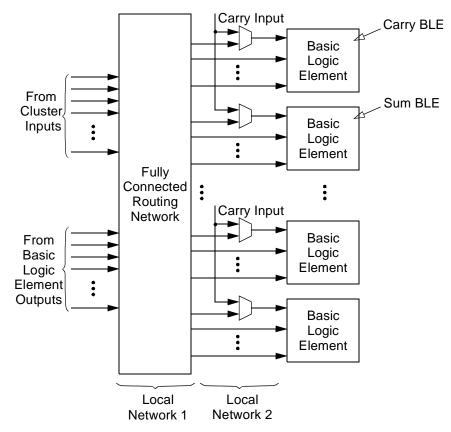

| 3.6.1.1 Clusters                                                                                                                                                                                                                                                                                             | 57  |

| Local Routing Network                                                                                                                                                                                                                                                                                        | 58  |

| Carry Network in Detail                                                                                                                                                                                                                                                                                      | 59  |

| 3.6.1.2 Configuration Memory Sharing                                                                                                                                                                                                                                                                         | 60  |

| 3.6.2 Routing Switches                                                                                                                                                                                                                                                                                       |     |

| 3.6.3 Routing Channels                                                                                                                                                                                                                                                                                       |     |

| 3.6.4 Switch Blocks                                                                                                                                                                                                                                                                                          |     |

| 3.6.5 Input and Output Connection Blocks                                                                                                                                                                                                                                                                     |     |

| 3.6.6 I/O Blocks                                                                                                                                                                                                                                                                                             |     |

| 3.7 Summary                                                                                                                                                                                                                                                                                                  |     |

| 4 An Area Efficient Synthesis Algorithm for Datapath Circuits 4.1 Introduction 4.2 Motivation and Background 4.3 Datapath Circuit Representation 4.4 The EMC Synthesis Algorithm 4.4.1 Word-Level Optimization 4.4.1.1 Common Sub-expression Extraction 4.4.1.2 Operation Reordering 4.4.2 Module Compaction |     |

| 4.4.3 Bit-Slice Netlist I/O Optimization                                                                                                                                                                                                                                                                     |     |

| 4.5 Experimental Results                                                                                                                                                                                                                                                                                     |     |

| 4.5.1 Area Inflation                                                                                                                                                                                                                                                                                         |     |

| 4.5.2 Regularity                                                                                                                                                                                                                                                                                             |     |

| 4.5.2.1 Logic Regularity                                                                                                                                                                                                                                                                                     |     |

| 4.5.2.2 Net Regularity                                                                                                                                                                                                                                                                                       |     |

| 4.6 Conclusion                                                                                                                                                                                                                                                                                               | 93  |

|                                                                                                                                                                                                                                                                                                              |     |

| 5 A Datapath-Oriented Packing Algorithm                                                                                                                                                                                                                                                                      | 2-  |

| 5.1 Introduction                                                                                                                                                                                                                                                                                             |     |

| 5.2 Motivation                                                                                                                                                                                                                                                                                               |     |

| 5.3 General Approach and Problem Definition                                                                                                                                                                                                                                                                  |     |

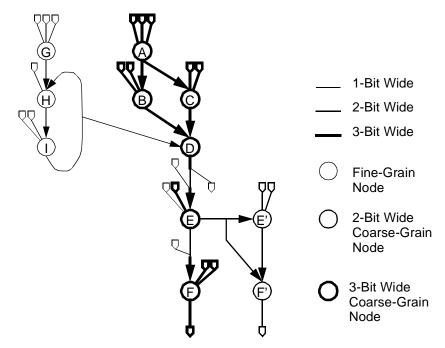

| 5.4 Datapath Circuit Representation                                                                                                                                                                                                                                                                          | 100 |

|   | 5.5 The CNG Packing Algorithm                       | 102 |

|---|-----------------------------------------------------|-----|

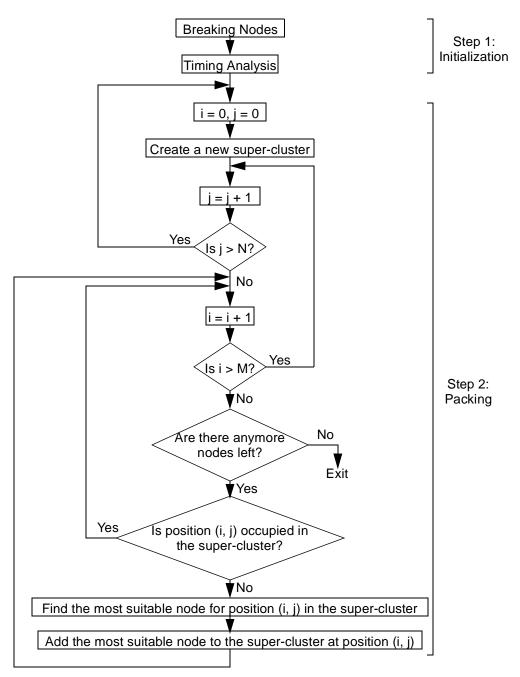

|   | 5.5.1 Step 1: Initialization                        | 102 |

|   | 5.5.1.1 Breaking Nodes                              | 102 |

|   | 5.5.1.2 Timing Analysis and Criticality Calculation | 103 |

|   | 5.5.2 Step 2: Packing                               |     |

|   | 5.5.2.1 Calculating Seed Criticality                | 106 |

|   | 5.5.2.2 Calculating Attraction Criticality          | 109 |

|   | Base Seed Criticality                               |     |

|   | Secondary Attraction Criticality                    |     |

|   | Shared I/O Count                                    |     |

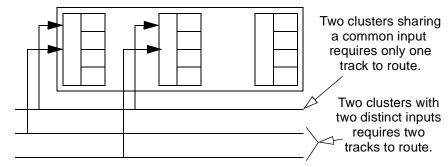

|   | Common I/O Count                                    | 111 |

|   | 5.6 Results                                         | 112 |

|   | 5.6.1 Super-Cluster Architectures                   | 113 |

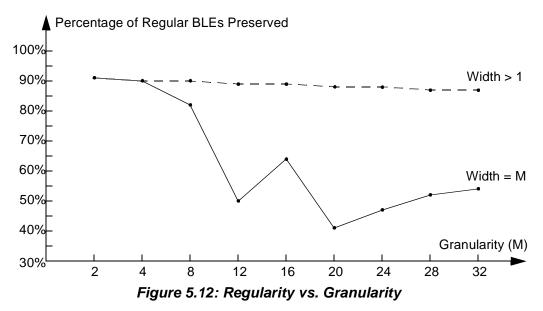

|   | 5.6.2 Regularity Results                            | 114 |

|   | 5.6.3 Area Results                                  | 114 |

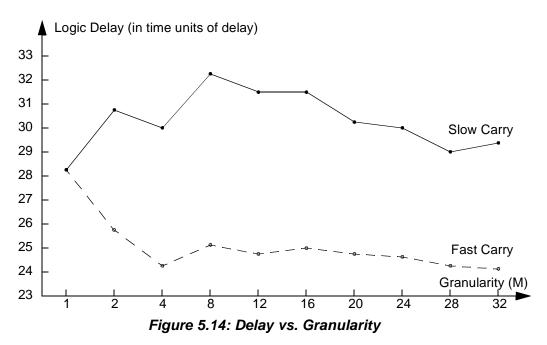

|   | 5.6.4 Performance Results                           | 116 |

|   | 5.7 Conclusions and Future Work                     | 117 |

|   |                                                     |     |

| 6 | A Datapath-Oriented Routing Algorithm               |     |

|   | 6.1 Introduction                                    | 119 |

|   | 6.2 Motivation                                      | 120 |

|   | 6.3 The MB-FPGA Placer                              | 122 |

|   | 6.4 General Approach and Problem Definition         | 123 |

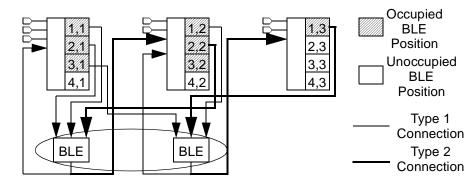

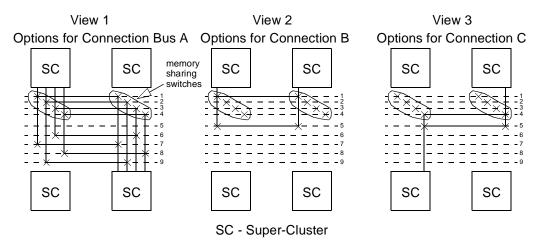

|   | 6.5 MB-FPGA Architectural Representation            | 124 |

|   | 6.6 The CGR Routing Algorithm                       | 126 |

|   | 6.6.1 Step 1: Initialization                        | 127 |

|   | 6.6.2 Step 2: Routing Nets                          | 130 |

|   | 6.6.2.1 Congestion Cost                             | 131 |

|   | 6.6.2.2 Optimizing Circuit Delay                    | 132 |

|   | 6.6.2.3 Expansion Cost                              | 133 |

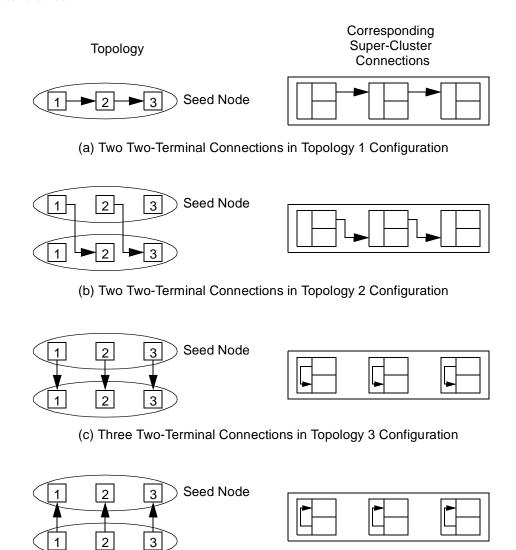

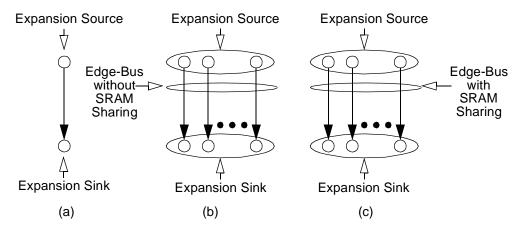

|   | Expansion Topologies                                | 133 |

|   | Expansion Cost Functions                            | 136 |

|   | 6.6.3 Step 3: Updating Metrics                      | 140 |

|   | 6.7 Results                                         | 141 |

|   | 6.7.1 MB-FPGA Architecture                          | 141 |

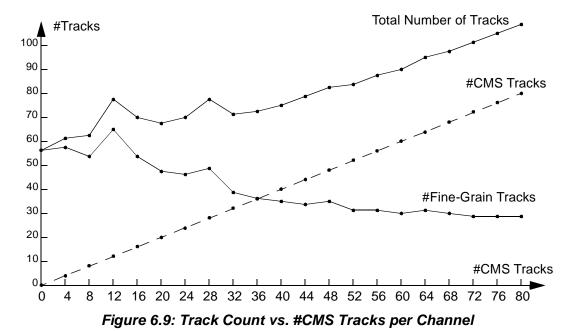

|   | 6.7.2 Track Count                                   |     |

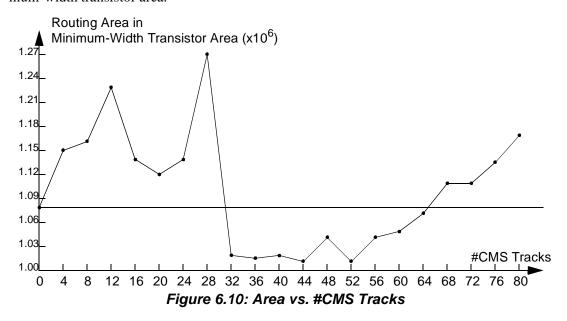

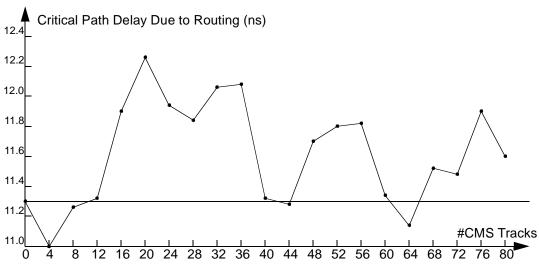

|   | 6.7.3 Routing Area Results                          |     |

|   | 6.7.4 Routing Performance Results                   |     |

|   | 6.8 Conclusions and Future Work                     | 146 |

| _ |                                                     |     |

| 7 | The Regularity of Datapath Circuits                 |     |

|   | 7.1 Introduction                                    |     |

|   | 7.2 MB-FPGA Architectural Assumptions               |     |

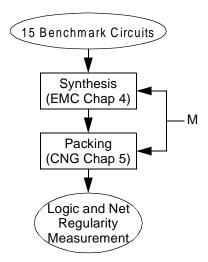

|   | 7.3 Experimental Procedure                          |     |

|   | 7.4 Experimental Results                            |     |

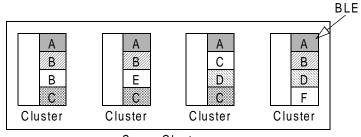

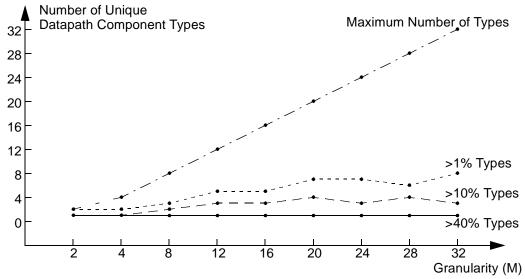

|   | 7.4.1 Effect of Granularity on Logic Regularity     | 152 |

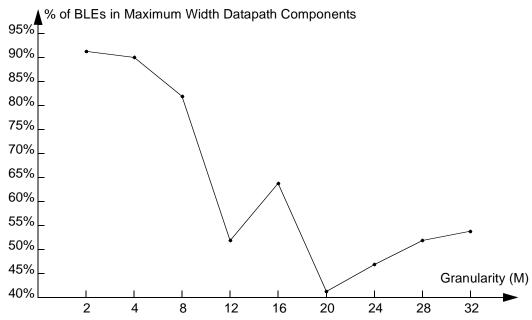

| 7.4.1.1 Diversity of Datapath Widths                           | 155 |

|----------------------------------------------------------------|-----|

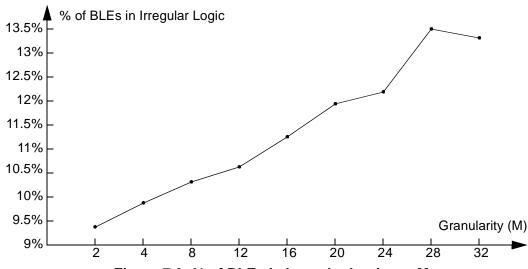

| 7.4.1.2 Maximum Width Datapath Components and Irregular Logic  |     |

| 7.4.1.3 Inherent Regularity Distribution                       | 158 |

| 7.4.1.4 Architectural Conclusions                              |     |

| 7.4.2 Effect of Granularity on Net Regularity                  |     |

| 7.4.2.1 Shift Definition                                       |     |

| 7.4.2.2 Net Regularity Results                                 | 162 |

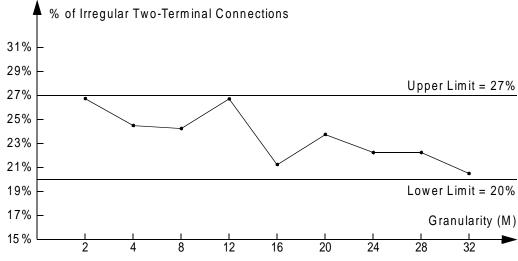

| 7.4.2.3 Effect of M on Irregular Two-Terminal Connections      |     |

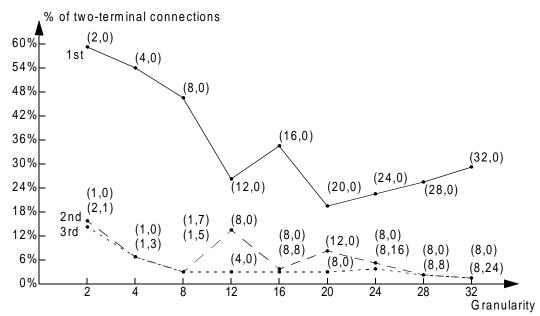

| 7.4.2.4 Effect of M on the Most Populous Bus Types             |     |

| 7.4.2.5 Architectural Conclusions                              |     |

| 7.5 Summary and Conclusions                                    | 165 |

|                                                                |     |

| 8 The Area Efficiency of MB-FPGA                               |     |

| 8.1 Introduction                                               |     |

| 8.2 MB-FPGA Architectural Assumptions                          |     |

| 8.2.1 A Summary of Architectural Parameters                    |     |

| 8.2.2 Parameter Values                                         |     |

| 8.2.2.1 Physical Placement of Super-Cluster Inputs and Outputs |     |

| 8.2.2.2 Physical Placement of Isolation Buffers                |     |

| 8.2.3 Transistor Sizing                                        |     |

| 8.3 Experimental Procedure                                     |     |

| 8.4 Limitations of this work                                   |     |

| 8.5 Experimental Results                                       |     |

| 8.5.1 Effect of Granularity on Area Efficiency                 |     |

| 8.5.1.1 MB-FPGA Architectures with No CMS Routing Tracks       |     |

| 8.5.1.2 MB-FPGA Architectures with CMS Routing Tracks          |     |

| 8.5.2 Effect of Proportion of CMS Tracks on Area Efficiency    |     |

| 8.5.3 MB-FPGA Versus Conventional FPGA                         |     |

| 8.5.3.1 Parameter Results                                      |     |

| Fc_of                                                          |     |

| Fc_if and Fc_pf                                                |     |

| Lf                                                             |     |

| 8.5.3.2 Area and Performance Results                           |     |

| 8.6 Summary and Conclusions                                    | 194 |

| O. Clare design                                                |     |

| 9 Conclusions                                                  | 105 |

| 9.1 Thesis Summary                                             |     |

|                                                                |     |

| 9.3 Suggestions for Future Research                            | 199 |

| Appendix A: Net Regularity Distribution                        |     |

| A.1 MB-FPGA Architectural Granularity = 2                      | 203 |

| A.2 MB-FPGA Architectural Granularity = 4                      |     |

| A.3 MB-FPGA Architectural Granularity = 8                      |     |

| A.4 MB-FPGA Architectural Granularity = 12                     |     |

| A 5 MR-EPGA Architectural Granularity – 16                     | 204 |

| A.6 MB-FPGA Architectural Granularity = 20 | 206 |

|--------------------------------------------|-----|

| A.7 MB-FPGA Architectural Granularity = 24 |     |

| A.8 MB-FPGA Architectural Granularity = 28 |     |

| A.9 MB-FPGA Architectural Granularity = 32 | 213 |

# LIST OF FIGURES

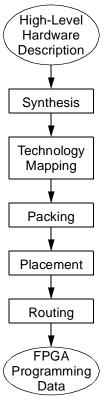

| 2.1  | FPGA CAD Flow                                                       | 8  |

|------|---------------------------------------------------------------------|----|

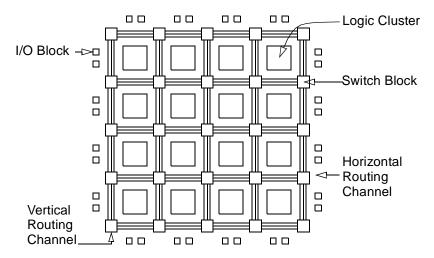

| 2.2  | Overview of FPGA Architecture Described in [Betz99a]                | 17 |

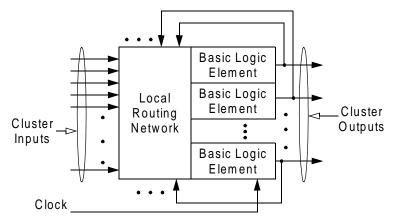

| 2.3  | Logic Cluster                                                       | 17 |

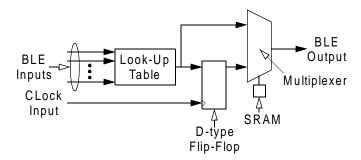

| 2.4  | Basic Logic Element                                                 | 18 |

| 2.5  | Look-Up Table                                                       | 18 |

| 2.6  | Routing Switches                                                    | 20 |

| 2.7  | Buffer Sharing                                                      | 21 |

| 2.8  | Routing Channel                                                     | 22 |

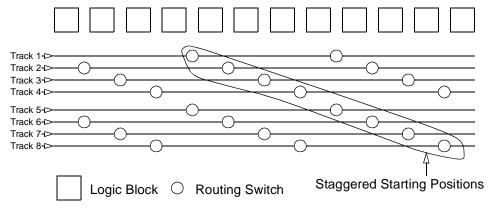

| 2.9  | Staggered Wire Segments                                             | 23 |

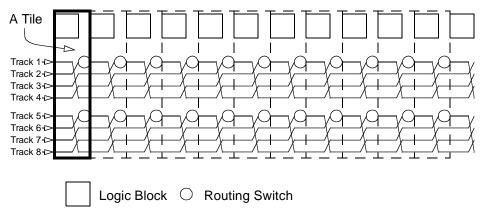

| 2.10 | Tiles                                                               | 23 |

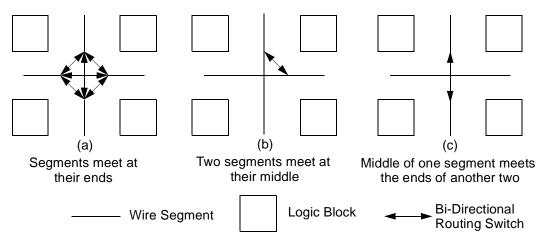

| 2.11 | Different Topologies of A Horizontal Track Meeting A Vertical Track | 24 |

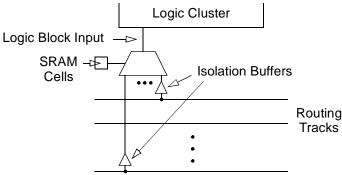

| 2.12 | Input Connection Block                                              | 25 |

| 2.13 | Output Connection Block                                             | 26 |

| 2.14 | Overview of DP-FPGA Architecture                                    | 27 |

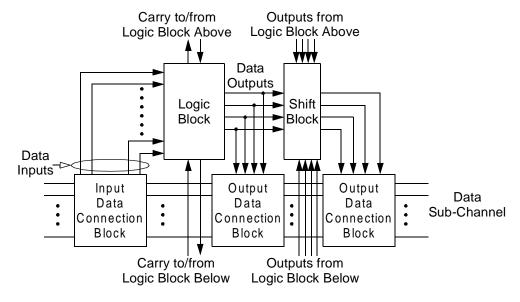

| 2.15 | Overview of Datapath Block                                          | 28 |

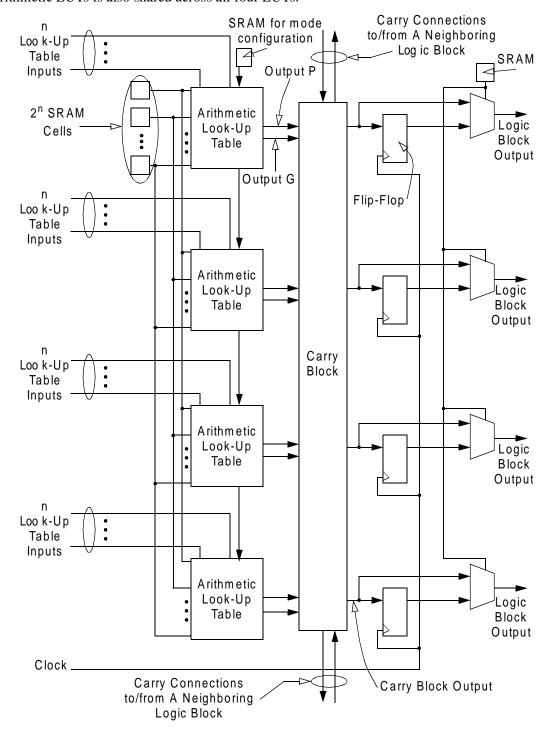

| 2.16 | Arithmetic Look-Up Table                                            | 29 |

| 2.17 | Logic Block Connectivity                                            | 30 |

| 2.18 | DP-FPGA Logic Block                                                 | 31 |

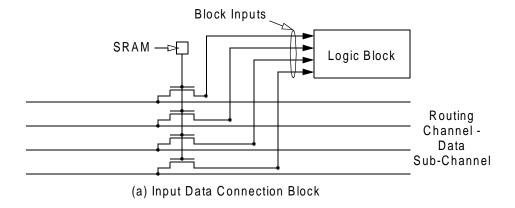

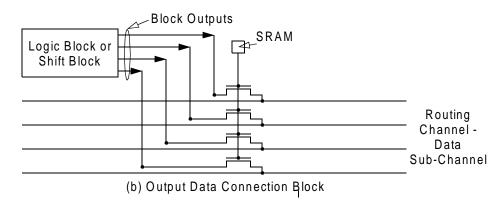

| 2.19 | Data Connection Block                                               | 33 |

| 3.1  | Arithmetic-Intensive Application                                    | 50 |

| 3.2  | Datapath Structure                                                  | 51 |

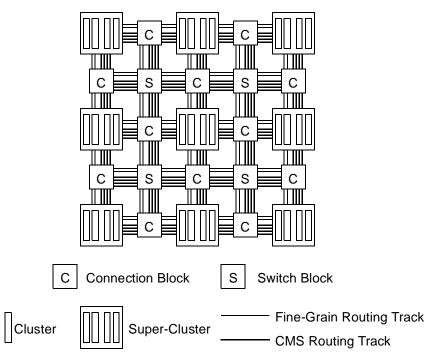

| 3.3  | Overview of MB-FPGA Architecture                                    |    |

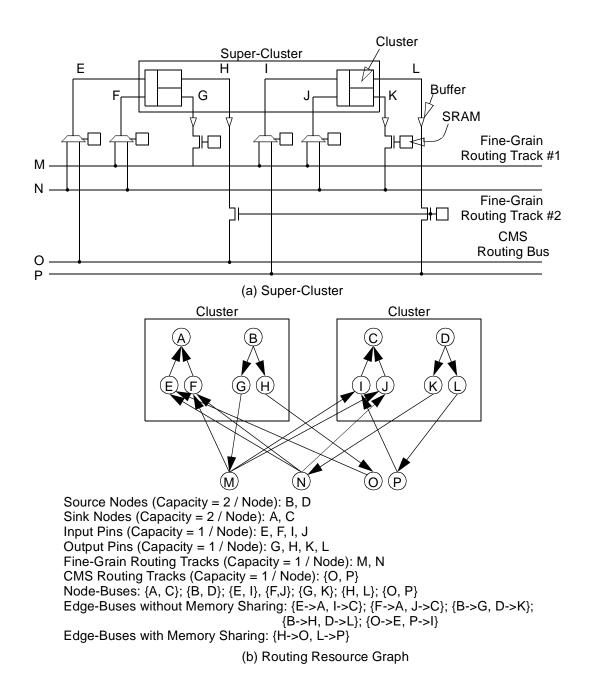

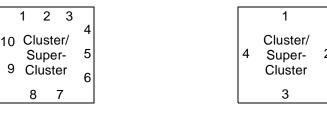

| 3.4  | Super-Cluster with M Clusters                                       | 56 |

| 3.5  | Cluster                                                             | 56 |

| 3.6  | A Modified Cluster from [Betz99a]                                   | 58 |

| 3.7  | Local Routing Network                                               | 59 |

| 3.8  | Carry Network                                                       | 60 |

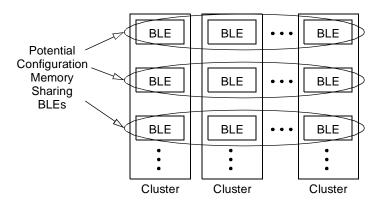

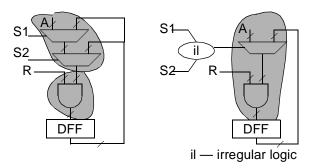

| 3.9  | BLEs and Configuration Memory Sharing                               | 61 |

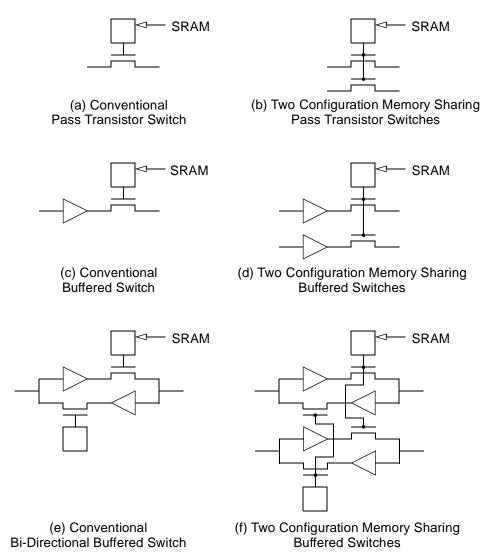

| 3.10 | Routing Switches                                                    |    |

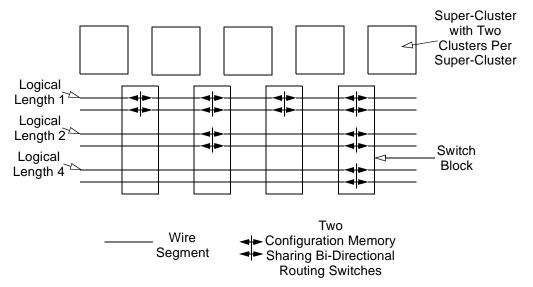

| 3.11 | CMS Routing Tracks With A Granularity Value of Two                  | 63 |

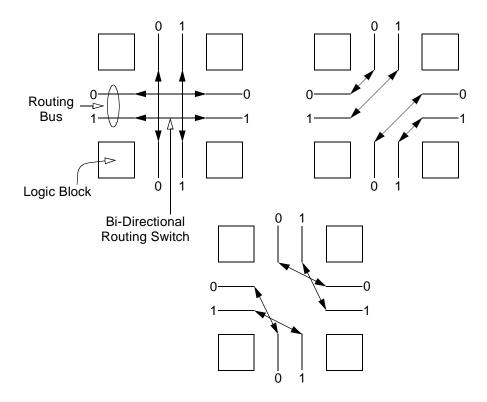

| 3.12 | Connecting Routing Buses                                            | 65 |

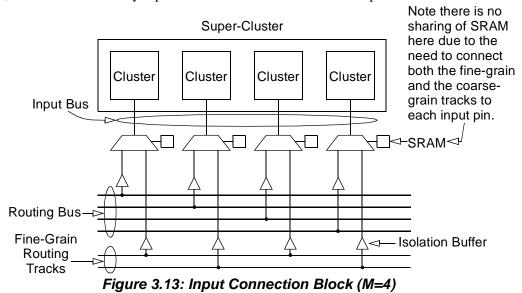

| 3.13 | Input Connection Block (M=4)                                        | 66 |

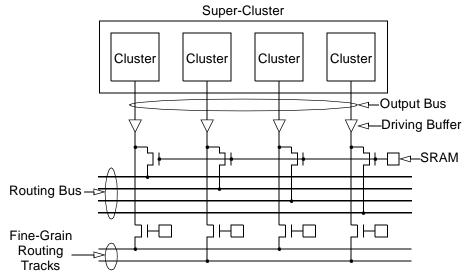

| 3.14 | Output Connection Block (M=4)                                       | 67 |

| 4.1  | Regularity and Area Efficiency                                      |    |

| 4.2  | Share Look-Up Table C                                               |    |

| 4.3  | Simplify Look-Up Table B                                            |    |

| 4.4  | 4-bit Ripple Adder Datapath Component                               |    |

| 4.5  | Overall Synthesis Flow                                              |    |

| 4.6  | Mux Tree Collapsing Example                                         | 78 |

| 4.7  | Result Selection to Operand Selection Transformation                | 80 |

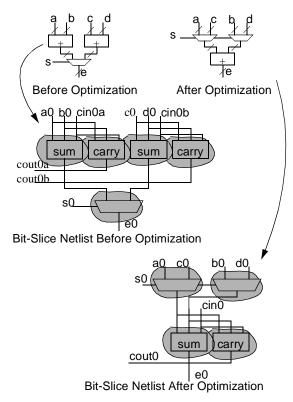

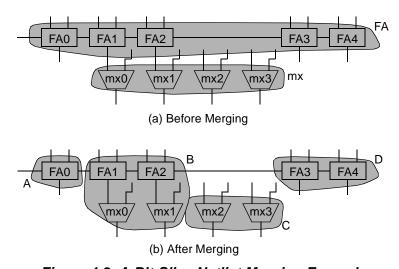

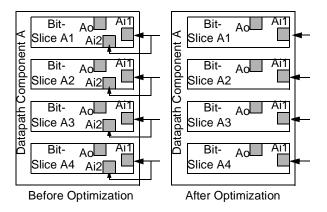

| 4.8  | A Bit-Slice Netlist Merging Example                         | 82  |

|------|-------------------------------------------------------------|-----|

| 4.9  | Feedback Absorption Example                                 | 85  |

| 4.10 | Duplicated Input Absorption                                 | 85  |

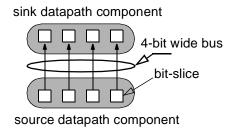

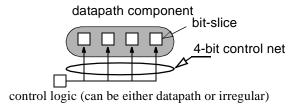

| 4.11 | 4-bit Wide Bus Topology                                     |     |

| 4.12 | 4-bit Control Net Topology                                  |     |

| 5.1  | Regularity and Performance                                  | 97  |

| 5.2  | A Naive Packing Solution                                    | 98  |

| 5.3  | A Better Packing Solution                                   |     |

| 5.4  | Coarse-Grain Node Graph                                     | 101 |

| 5.5  | Datapath Circuit Represented by the Coarse-Grain Node Graph |     |

| 5.6  | Overview of the CNG Packing Algorithm                       | 103 |

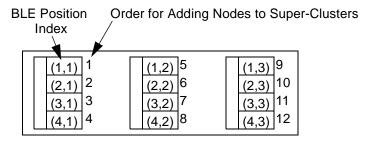

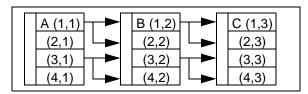

| 5.7  | Order for Filling Super-Cluster with $N = 4$ , $M = 3$      | 105 |

| 5.8  | Equivalence of BLEs in Clusters                             | 106 |

| 5.9  | Topology for Identifying Potential Local Connection         |     |

| 5.10 | Adding a Node to a Super-Cluster at Position (4,1)          | 110 |

| 5.11 | Common Inputs Between Clusters in a Super-Cluster           | 112 |

| 5.12 | Regularity vs. Granularity                                  | 115 |

| 5.13 | Area vs. Granularity                                        | 115 |

| 5.14 | Delay vs. Granularity                                       | 117 |

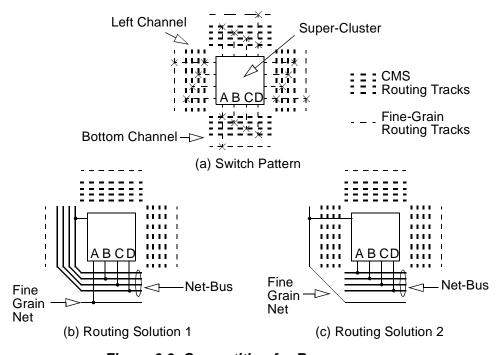

| 6.1  | Example of Contention Between CMS and Fine-Grain Nets       |     |

| 6.2  | An Example Routing Resource Graph                           | 126 |

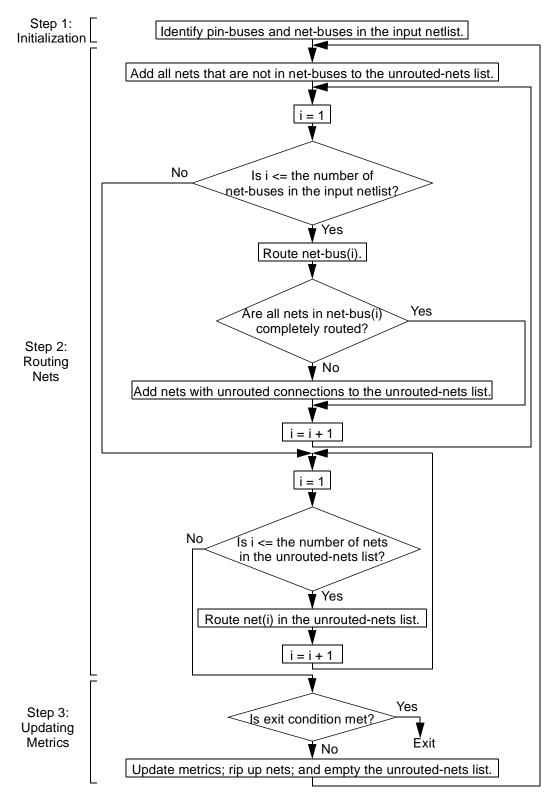

| 6.3  | Overview of the CGR Routing Algorithm                       | 128 |

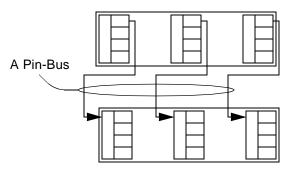

| 6.4  | A Pin-Bus                                                   |     |

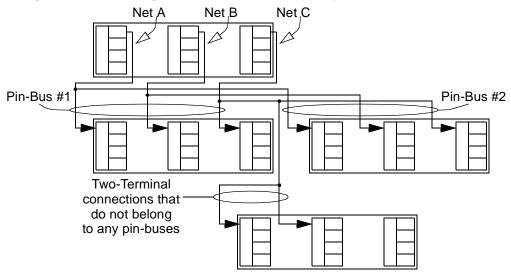

| 6.5  | A Net-Bus Containing Net A, B, and C                        |     |

| 6.6  | Competition for Resources                                   |     |

| 6.7  | Expansion Topology                                          | 139 |

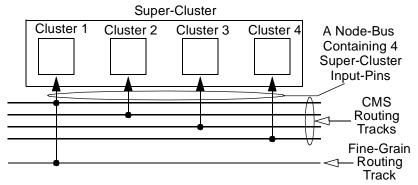

| 6.8  | Double Connection in One Bit of A Node-Bus                  | 140 |

| 6.9  | Track Count vs. #CMS Tracks per Channel                     | 144 |

| 6.10 | Area vs. #CMS Tracks                                        | 145 |

| 6.11 | Delay vs. #CMS Tracks                                       | 146 |

| 7.1  | Super-Cluster with M Clusters                               |     |

| 7.2  | CAD Flow                                                    | 152 |

| 7.3  | Dividing A Super-Cluster into Datapath Components           |     |

| 7.4  | Datapath Component Types Containing a Minimum % of BLEs     |     |

| 7.5  | % of BLEs in Maximum Width Datapath Components              |     |

| 7.6  | % of BLEs in Irregular Logic vs. M                          |     |

| 7.7  | A 2-bit wide bus with one-bit shift for $M = 4$             |     |

| 7.8  | % of Irregular Two-Terminal Connections vs. M               |     |

| 7.9  | The Most Populous Bus Types for Each Granularity            | 165 |

| 8.1  | The MB-FPGA Architecture                                    |     |

| 8.2  | Tp for FPGA Architectures with N = 4 and I = 10             | 176 |

| 8.3  | Isolation Buffer Topology for Conventional FPGA             | 177 |

| 8.4  | Equivalent MB-FPGA Architecture                      | 178 |

|------|------------------------------------------------------|-----|

| 8.5  | CAD Flows                                            | 180 |

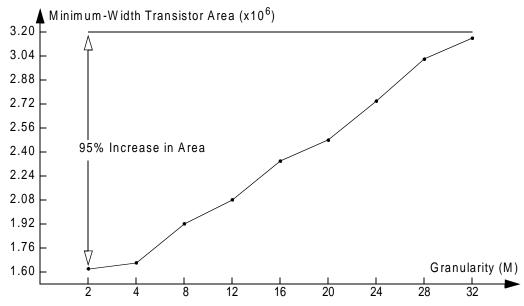

| 8.6  | Total Area vs. M with No CMS Routing Tracks          | 183 |

| 8.7  | Logic Area vs. M with No CMS Routing Tracks          | 185 |

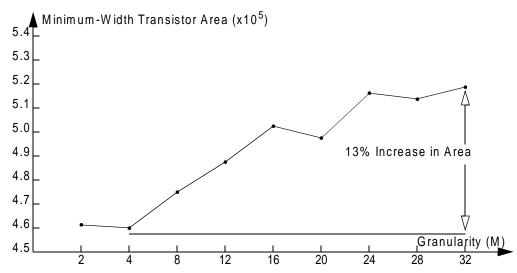

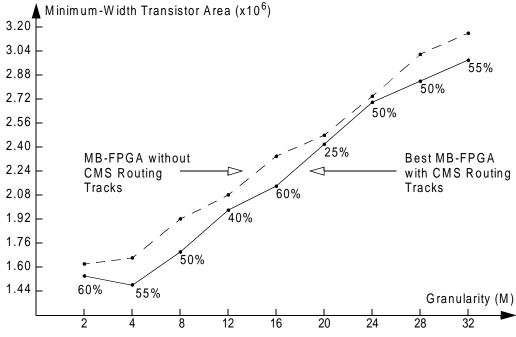

| 8.8  | Area vs. M with CMS Routing Tracks                   | 185 |

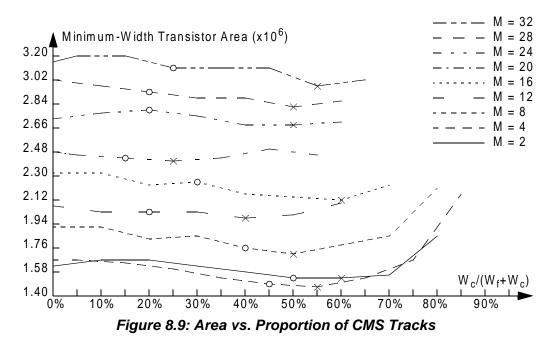

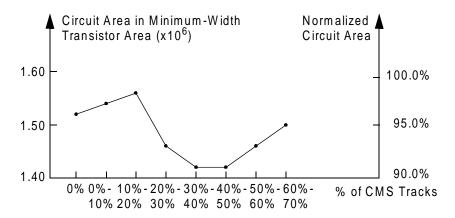

| 8.9  | Area vs. Proportion of CMS Tracks                    | 187 |

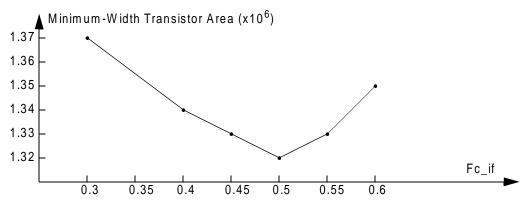

| 8.10 | Iteration 1: Routing Area vs. Fc_if for Fc_pf = 1.00 | 189 |

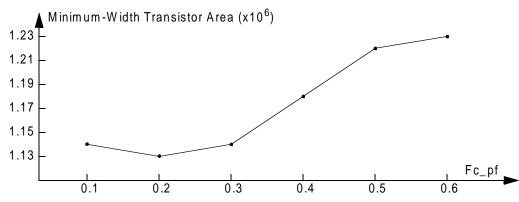

| 8.11 | Iteration 2: Routing Area vs. Fc_pf for Fc_if = 0.5  | 189 |

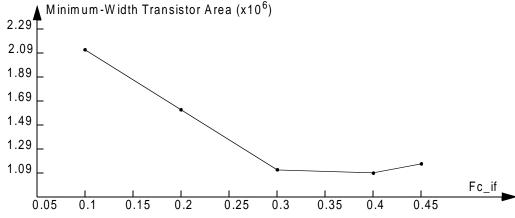

| 8.12 | Iteration 3: Routing Area vs. Fc_if for Fc_pf = 0.2  | 190 |

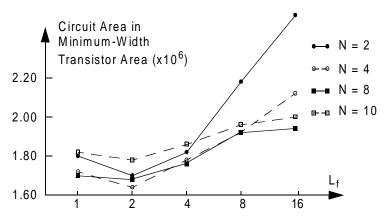

| 8.13 | Area vs. Logical Track Length                        | 191 |

| 8.14 | Area vs. Percentage of CMS Tracks                    | 192 |

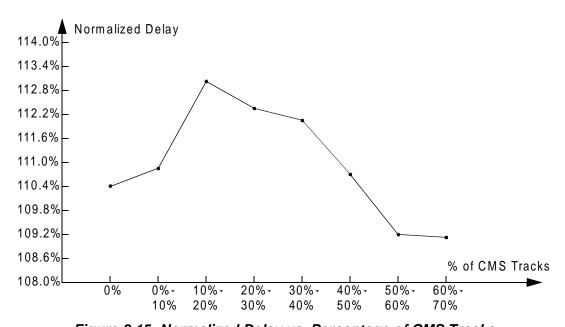

| 8.15 | Normalized Delay vs. Percentage of CMS Tracks        | 193 |

|      |                                                      |     |

# LIST OF TABLES

| 4.1  | Area Inflation for Hard-Boundary Hierarchical Synthesis        | 74  |

|------|----------------------------------------------------------------|-----|

| 4.2  | LUT & DFF Inflation for Regularity Preserving Synthesis        | 87  |

| 4.3  | LUT Count Inflation as a Function of Granularity               |     |

| 4.4  | Logic Regularity                                               | 91  |

| 4.5  | Net Regularity                                                 | 92  |

| 5.1  | Experimental Circuits                                          | 113 |

| 6.1  | b(n) Values for Each Type of Routing Resource                  |     |

| 6.2  | Expansion Cost                                                 | 137 |

| 6.3  | Experimental Circuits                                          | 142 |

| 7.1  | % of BLEs Contained in Each Width of Datapath Components       |     |

| 7.2  | Distribution of BLEs for M = 32                                | 158 |

| 7.3  | % of Inter-Super-Cluster Two-Terminal Connections Contained in |     |

|      | Each Type of Buses for $M = 12$                                | 163 |

| 8.1  | MB-FPGA Architectural Parameters                               | 170 |

| 8.2  | Values for Architectural Parameters                            | 173 |

| A.1  | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 2$                                              | 203 |

| A.2  | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 4$                                              | 203 |

| A.3  | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 8$                                              | 204 |

| A.4  | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 12$                                             | 204 |

| A.5  | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 16 - Part 1 \text{ of } 2$                      | 205 |

| A.6  | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 16 - Part 2 \text{ of } 2$                      | 205 |

| A.7  | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 20 - Part 1 \text{ of } 2$                      | 206 |

| A.8  | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 20 - Part 2$ of 2                               | 207 |

| A.9  | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 24 - Part 1$ of 2                               | 208 |

| A.10 | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 24 - Part 2$ of 2                               | 209 |

| A.11 | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 28 - Part 1$ of $3$                             | 210 |

| A.12 | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|------|----------------------------------------------------------------|-----|

|      | Buses for $M = 28 - Part 2 \text{ of } 3$                      | 211 |

| A.13 | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 28 - Part \ 3 \ of \ 3$                         | 212 |

| A.14 | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 32 - Part 1$ of $3$                             | 213 |

| A.15 | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 32 - Part 2$ of $3$                             | 214 |

| A.16 | % of Inter-Super-Cluster Connections Contained in Each Type of |     |

|      | Buses for $M = 32 - Part 3 \text{ of } 3$                      | 215 |

|      |                                                                |     |

### 1 Introduction

### 1.1 Introduction to Field-Programmable Gate Arrays

Field-Programmable Gate Arrays (FPGAs) are user programmable digital devices that provide efficient, yet flexible, implementations of digital circuits. An FPGA consists of an array of programmable logic blocks interconnected by programmable routing resources. The flexibility of FPGAs allows them to be used for a variety of digital applications from small finite state machines to large complex systems. The research reported in this thesis is focused on reducing the implementation area of large, arithmetic-intensive, systems on FPGAs through architectural innovations. We also present new and innovative Computer-Aided Design (CAD) algorithms which are designed to support the new architecture.

Since their invention in 1984 [Cart86], FPGAs have become one of the most widely used platforms for digital applications. Comparing to alternative technologies, which directly fabricate hardware on silicon, FPGAs have the advantage of instant manufacturability and infinite re-programmability. They also incur lower cost for low to medium volume production of digital devices. Unlike full fabrication of integrated circuits, which require highly specialized manufacturing facilities and cost hundreds of thousands of dollars to prototype, FPGAs can be programmed on the desks of their designers. This makes the verification of hardware designs much faster — once a mistake is found, unlike full fabrication, which has to rebuild masks, corrections on FPGAs only take the reprogramming of a few configuration memory bits. This also allows multiple design iterations to be done quickly and at a much lower cost. FPGA based applications also can be updated after they are delivered to their customers allowing incremental hardware improvements and adaptation of old designs to new protocols and spec-

ifications. Furthermore, FPGA CAD tools are much cheaper to acquire than comparable CAD tools that support full fabrication.

These advantages allow FPGAs to compete head on with full fabrication technologies, such as the Application Specific Integrated Circuit (ASIC) technology, for market share. The user-programmability of FPGAs, however, also has its shortcomings: FPGAs are more expensive in high volume production; circuits implemented on FPGAs are usually many times bigger and slower than comparable ASICs. In order for FPGAs to overtake full fabrication technologies, FPGA researchers need to find new and innovative ways of improving the performance and logic density of FPGAs.

### 1.2 Thesis Motivation

Over the years, the capacity of FPGAs has increased dramatically. Current state-of-the-art devices can contain near 100,000 logic elements (where a logic element is typically a 4-input look-up table, a flip-flop, and 1-bit worth of arithmetic carry logic) [Alte02] [Xili02] with a projected logic capacity of several million logic gates [Xili02]. In comparison, the first FPGA [Cart86] contains only 64 logic blocks with a projected capacity of between 1000 and 1600 gates. Since the logic capacity has grown significantly, the application domain of FPGAs has been greatly expanded. Modern FPGAs are often used to implement large arithmetic-intensive applications, including CPUs, digital signal processors, graphics accelerators and internet routers.

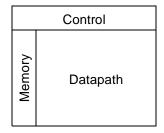

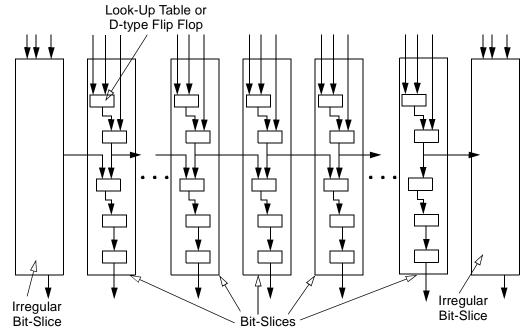

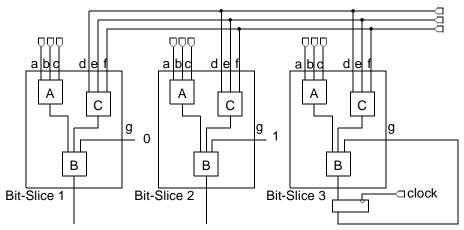

Arithmetic-intensive applications often contain significant quantities of regular structures called *datapaths*. These datapaths are constructed out of multiple identical building blocks called *bit-slices*. They are used to perform mathematical or logical operations on multiple-bits of data. It is our hypothesis that *greater area efficiency can be achieved in FPGAs by incorporating datapath specific features*. One such feature is the *configuration memory shar-*

ing (CMS) routing resources proposed by Cherepacha and Lewis in [Cher96], which takes the advantage of the regularity of datapath circuits by sharing configuration memory bits across normally independent routing resources. This reduces the number of programming bits needed to control these resources and consequently reduces FPGA area.

The primary focus of this thesis is to explore in-depth methods of increasing FPGA logic density for arithmetic circuits using multi-bit logic and CMS routing structures under a highly automated modern design environment. The goal of the study is to determine the most appropriate amount of CMS routing resources in order to achieve the best logic density improvement for real circuits using real automated CAD tools. Since routing area typically consists of a significant percentage of the total FPGA area, its reduction is particularly important to reduce the overall FPGA area. This research is a continuation of the DP-FPGA work [Cher96]. It is also closely related in methodology to several previous FPGA research projects [Betz99a].

# 1.3 Research Approach

Datapath-oriented FPGA architectures are studied in this thesis using an experimental approach. A parameterized FPGA architecture, called Multi-Bit FPGA (MB-FPGA), with busbased CMS routing resources has been proposed. A complete CAD flow for the architecture has also been implemented. The experiments consist of varying the amount of CMS routing resources and measuring the effects on the implementation area of datapath circuits. The results of the experiments provide insight to the amount of CMS routing resources that are needed to achieve area savings for real datapath applications using real CAD tools.

### 1.4 Thesis Contributions

To the best knowledge of the author, the MB-FPGA architecture is the first completely specified special-purpose FPGA architecture targeting datapaths. It is also the first FPGA architecture containing CMS routing resources supported by a complete set of CAD tools. Furthermore, the architectural study presented here represents the first in-depth empirical study on the effectiveness of CMS routing resources in translating datapath regularity into area savings. Previous studies [Cher96] [Leij03] on the subject are all analytical in nature. As a result, none of them takes the detailed transistor-sizing issues, the actual benchmark regularity, and the area efficiency of the CAD algorithms into account. As it will be shown by the results of this study, these previous studies are much less accurate and tends to overestimate the benefits of the CMS resources.

### 1.5 Thesis Organization

This thesis is organized as follows. Chapter 2 reviews the background information relevant to this work, including a review of various CAD tools available for transforming high-level descriptions of digital circuits into FPGA programming information. The review includes a brief description of representative tools from each major class of CAD tools. The chapter also describes the work of two previous architectural studies that significantly influenced the work presented in this thesis.

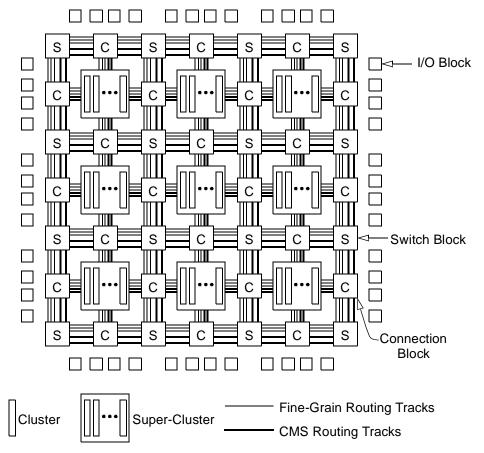

Chapter 3 presents a new, highly parameterized, datapath-oriented FPGA architecture called the Multi-Bit FPGA (MB-FPGA). The architecture is unique in that it uses a mixture of conventional routing resources and CMS routing resources. The combination allows a homogenous architecture for the efficient implementation of large datapath circuits as well as small non-datapath circuits. The architecture is the basis from which the CAD flow presented in

Chapter 4, 5, and 6 are designed and the experiments presented in Chapter 7 and 8 are conducted.

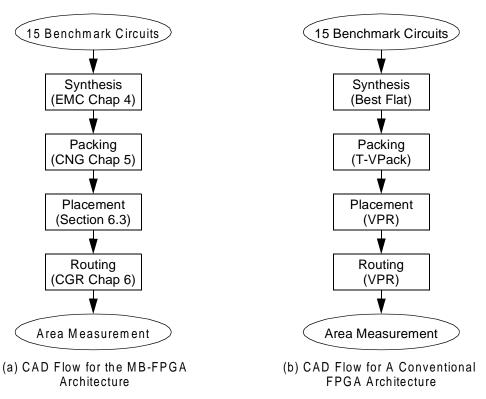

Chapter 4, 5, and 6 presents a new datapath-oriented CAD flow. The flow includes several new algorithms covering the entire process of transforming and optimizing high-level circuit descriptions into FPGA programming information. These algorithms are unique in that they effectively preserve and utilize datapath regularity on CMS routing resources. In particular, Chapter 4 discusses datapath-oriented synthesis; Chapter 5 presents a datapath-oriented packing algorithm; and Chapter 6 discusses datapath-oriented placement and routing.

Using the synthesis and packing tools presented in Chapter 4 and 5, Chapter 7 characterizes and quantifies the amount of regularity presented in a typical datapath circuit. Analytically, this regularity information is used to determine good values for several important MB-FPGA architectural parameters, including the degree of configuration memory sharing (called *granularity*) and the proportion of CMS routing resources.

The MB-FPGA is directly explored in Chapter 8 using an experimental approach. The CAD flow presented in Chapter 4, 5, and 6 is used to implement a set of datapath circuits on the MB-FPGA architecture. For each circuit the best area is evaluated by varying a range of architectural parameters. The experiments measure the effectiveness of CMS routing on improving the area efficiency of datapath circuit implementations and the effect of these routing resources on performance.

Finally, Chapter 9 provides concluding remarks and directions for future research.

# 2 Background

### 2.1 Introduction

This chapter reviews the two main fields of research, FPGA CAD tools and FPGA architectures, that are studied in this thesis. Section 2.2 provides some necessary background information on FPGA CAD that is assumed in various discussions, particularly in Chapter 4, 5, and 6, which discuss CAD design for the MB-FPGA architecture. Section 2.3 describes several previous FPGA architectures to provide a point of reference for the MB-FPGA architecture presented in Chapter 3 and the FPGA modeling methodology that is used throughout this work.

### 2.2 FPGA CAD Flow

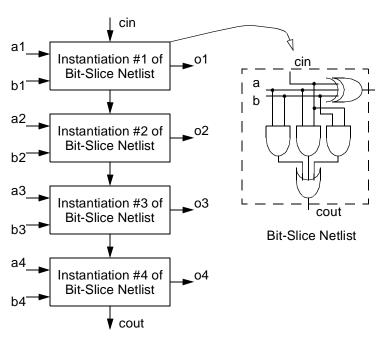

Since the focus of this thesis is the design of a datapath-oriented FPGA architecture supported by a highly automated modern design environment, this chapter begins with an overview of the modern CAD tools that are commonly used to implement circuits on FPGAs. A typical CAD flow for FPGAs consists of a series of interconnected CAD tools as illustrated in Figure 2.1. The input to the flow usually is a high-level description of the hardware, expressed in high-level hardware description languages such as Verilog or VHDL.

The description is read by a synthesis program [Call98] [Cora96] [Koch96a] [Koch96b] [Kutz00a] [Kutz00b] [Nase94] [Nase98] [Syno99] [Synp03], which maps the description language into a network of Boolean equations, flip-flops, and pre-defined modules. During the synthesis process, the Boolean equations are optimized with respect to estimated implementation area and delay. The optimizations performed at this stage are limited to those that can benefit circuit implementations on any medium, not just FPGAs. Some synthesis algorithms, including [Call98] [Cora96] [Koch96a] [Koch96b] [Kutz00a] [Kutz00b] [Nase94] [Nase98],

Figure 2.1: FPGA CAD Flow

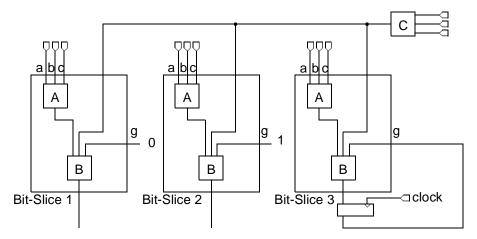

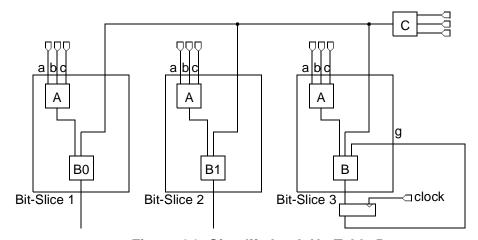

also attempt to preserve the regularity of datapath circuits by maintaining a hierarchy that clearly delineates the boundary of bit-slices. These algorithms are often called the *datapath-oriented synthesis algorithms*.

The Boolean equations are then first mapped into a circuit of FPGA Look-Up Tables (LUTs) through the technology mapping process [Syno99]. Then the packing process [Betz97a] [Betz99a] [Marq99] [Bozo01] groups LUTs and flip-flops into logic blocks, each of which usually contains several LUTs and flip-flops. During the technology mapping and the packing process, the circuit is again optimized with respect to estimated implementation area and delay. This time the optimizations are targeted towards specific implementation technologies. Area is typically optimized by minimizing the number of LUTs or logic blocks that are

required to implement the circuit; and delay is often optimized by minimizing the number of LUTs or logic blocks that are on the estimated timing-critical paths of the circuit.

The specific location of each logic block on the target FPGA is determined during the placement process [Betz99a] [Kirk83] [Marq00a] [Sech85] [Sech86] [Sech87] [Sun95] [Swar95]. A placement program assigns each logic block to an unique location to optimize delay and minimize wiring demand.

Finally, during the routing process [Betz99a] [Brow92a] [Brow92b] [Chan00] [Ebel95] [Lee61] [Swar98], a routing program is used to connect logic blocks together by determining the configuration of the programmable routing resources. The main task of all routing programs is to successfully establish all connections in a circuit using the limited amount of physical resources available on the target FPGA. The other task of the routing programs is to minimize delay by allocating fast physical connections to timing-critical paths.

Together the synthesis, technology mapping, and packing process are commonly called the front end of the FPGA CAD flow; and the placement and routing steps are commonly called the back end of the FPGA CAD flow. The remainder of this section reviews previous work on each stage of the FPGA CAD flow. In particular, several tools discussed below, including the Synopsys FPGA compiler [Syno99] for synthesis and technology mapping, the T-VPACK packer [Marq99] [Betz99a] for packing, and the VPR (Versatile Placer and Router) [Betz99a] tools for placement and routing, serve as the framework from which the CAD work described in Chapter 4, Chapter 5, and Chapter 6 is developed.

# 2.2.1 Synthesis and Technology Mapping

There are several commercially available synthesis tools for FPGAs, including the Synopsys *FPGA Compiler* [Syno99], Synplicity's *Synplify* [Synp03], and Altera *Quartus II* [Quar03]. In general, these tools perform both the task of synthesis and technology mapping;

however, none of these tools preserves the regularity of datapath circuits since they usually optimize across the boundaries of bit-slices. These cross-boundary optimizations often destroy the regularity of datapath circuits. This section first describes the various features of the Synopsys FPGA Compiler [Syno99], which is used as a part of a datapath-oriented synthesis flow built for the MB-FPGA architecture. Then previous research on datapath-oriented synthesis is reviewed in detail.

### 2.2.1.1 Synopsys FPGA Compiler

The Synopsys FPGA Compiler performs a combination of synthesis and technology mapping. The input to the compiler consists of three files including a circuit description file, an architectural description file, and a compiler script file. The circuit description file describes the behavior of the circuit that is to be synthesized. The format of the file can be in either Verilog, VHDL, or several other high-level or low-level hardware description languages.

The architectural description file describes the properties of two fundamental FPGA building blocks that the input circuit is to be mapped into, the LUTs and the flip-flops. The description includes parameters describing various delay and area properties of each building block. The LUTs are combinational circuit elements each with several inputs and one output. A LUT can be used to implement any single output Boolean function that has the same number of inputs as the LUT. The flip-flops, on the other hand, are used to implement sequential circuit elements.

The compiler script file gives specific compile-time instructions to the FPGA compiler. It can be used to set up various synthesis boundaries in the input circuit so that circuit elements will not be merged across these boundaries during the synthesis and the technology mapping

process. In this research, this feature is used to preserve datapath regularity; and it is described in more detail in Chapter 4.

The final output of the Synopsys FPGA compiler is a network of LUTs and flip-flops that implements the exact functionality of the input circuit. The compiler can output the final result in a variety of file formats including the Verilog and the VHDL formats.

### 2.2.1.2 Datapath-Oriented Synthesis

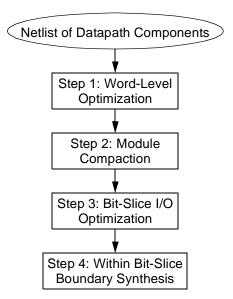

Datapath-oriented synthesis techniques can be roughly classified into four categories including hard-boundary hierarchical synthesis, template mapping [Call98] [Cora96] [Nase94] [Nase98], module compaction [Koch96a] [Koch96b], and the regularity preserving logic transformation algorithm [Kutz00a] [Kutz00b]. Note that most of these algorithms were primarily developed to speed up the development cycle (tool runtime) of their applications; and they often pay little attention to area optimization.

Hard-boundary hierarchical synthesis is the simplest form of regularity preserving synthesis. It preserves datapath regularity by performing optimizations strictly within the boundaries of user-defined bit-slices. However, as will be shown in Chapter 4, this method suffers from the problem of high area inflation when compared to conventional synthesis algorithms that do not preserve datapath regularity.

Template mapping [Call98] [Cora96] [Nase94] [Nase98] attempts to reduce the area inflation of the hard-boundary hierarchical synthesis by mapping the input datapath onto a set of predefined templates. These templates are datapath circuits that have been designed to be very area efficient. In theory, if one can define an arbitrarily large datapath template library and has an unlimited amount of time to reconstruct the input datapath circuits out of these templates, one can achieve excellent area efficiency. However, in real life, limited by a reasonably sized datapath template library and limited computing time, the template mapping algorithm

also performs poorly in terms of area efficiency and can have over 48% area inflation [Cora96].

Module compaction [Koch96a] [Koch96b] takes one step further. It merges some of the user-defined bit-slices into larger bit-slices while still preserving the regularity of datapath circuits. This algorithm is modified in Chapter 4 into an very area efficient datapath-oriented synthesis algorithm when complemented with several extra optimization steps. Without these optimization steps, however, the area efficiency of the module compaction algorithm as proposed in [Koch96a] [Koch96b] is still quite poor. For example, the algorithm discussed in [Koch96b] has an area inflation of on the order of 17%.

Finally, the regularity preserving logic transformation algorithm [Kutz00a] [Kutz00b] takes an entirely different approach to datapath-oriented synthesis. Instead of preserving user-defined regularity, it tries to extract regularity from flattened datapath logic. As a result, although it is effective in area optimization, its effectiveness, in preserving datapath regularity, is limited by the amount of regularity that can be discovered by the extraction process.

### 2.2.2 Packing

All existing packing algorithms place LUTs and flip-flops into FPGA logic blocks. Each logic block has a fixed capacity, which is determined by the number of LUTs and flip-flops that the logic block contains and the available number of unique logic block inputs and outputs. The VPACK algorithm [Betz97a] tries to maximize the number of LUTs that can be packed into a logic block by grouping highly connected LUTs together. The T-VPACK algorithm [Marq99] improves upon the VPACK algorithm by using the timing information on top of the connectivity information. Other packing algorithms, including RPACK and T-RPACK [Bozo01], further improve upon the VPACK and the T-VPACK algorithms by using routability information on top of the connectivity and timing information. Note that all four packing

algorithms assume a fully connected logic cluster architecture, which is described in detail in Section 2.3.1.1. Furthermore, during the packing process each packing algorithm considers individual LUTs or DFFs in isolation. As a result, none of these algorithms preserves the regularity of the datapath circuits during the packing process.

### 2.2.3 Placement and Routing

This section gives an overview of the VPR placement and routing tools [Betz99a], which serve as the basis for the MB-FPGA placement and routing software and algorithms described in Chapter 6. The VPR placer is based on the *simulated annealing* algorithm [Kirk83] [Sech85], while the VPR router is a *negotiation-based* router [Ebel95]. Note that simulated annealing based algorithms [Betz99a] [Kirk83] [Marq00a] [Sech85] [Sech86] [Sech87] [Sun95] [Swar95] are one of the most widely used types of placement algorithms for FPGAs, while many FPGA routing algorithms are negotiation-based routers [Betz99a] [Chan00] [Ebel95] [Lee61] [Swar98]. None of the existing placement [Betz99a] [Kirk83] [Marq00a] [Sech85] [Sech86] [Sech87] [Sun95] [Swar95] and routing algorithms [Betz99a] [Brow92a] [Brow92b] [Chan00] [Ebel95] [Lee61] [Swar98] preserves the regularity of datapath circuits. For placement, regularity is destroyed by existing placers, which only incrementally improve the placement of individual logic blocks. Routers, on the other hand, also destroy the regularity information as they only route one net at a time.

### 2.2.3.1 VPR Placer and Router

The VPR placer and the VPR router are contained in a single computer program. The input to the program consists of two files, a circuit description file and an architectural description file. The circuit description file describes a network of logic blocks that is to be implemented on an FPGA. The architectural description file specifies the detailed architecture of the

FPGA. The architectural choices in the architectural description file are limited to the variants of the logic cluster based FPGA architecture described in Section 2.3.1.

### The VPR Placer

The VPR placer performs placement using the simulated annealing algorithm [Kirk83] [Sech85]. It first places each logic block randomly onto an unoccupied location on the FPGA. It then moves two logic blocks by swapping their physical locations or moves a logic block into a location that is not occupied by any other logic blocks. After each move, the algorithm either keeps the move or discards the move by comparing the placement before the move with the placement after the move using a set of metrics. These metrics represent an estimation of how easily a particular placement can be routed and the achievable speed of the placement after routing. Usually the optimization strategy chooses a placement with a metric indicating easier routing or better speed. But occasionally, the algorithm chooses the opposite in the hope that a bad placement choice can lead to a very good one in subsequent moves.

A key metric in simulated annealing is called the *annealing temperature*. At the start of a placement process, the temperature is set at a very high value. Throughout the placement process, the temperature is gradually lowered to zero. At high temperatures, the optimization strategy will be more likely to choose a bad move; while at low temperatures, fewer bad moves are accepted by the algorithm. Finally at zero temperature, only good moves are accepted.

### The VPR Router

The VPR router takes the output of the VPR placer as its input. The input describes a network of logic blocks whose physical locations are determined. The same architectural file that the placer uses also specifies the routing architecture for the router. Recall that the fundamental goal of the routing tool is to successfully connect all the nets through the routing network and to meet the timing constraints of the most timing-critical connections.

Since each physical routing resource can only be used by a single net at a time, the best connection choices for individual nets might conflict with each other. The VPR router uses the negotiation-based approach of the Pathfinder routing algorithm [Elbe95] to resolve these routing conflicts. It connects the logic blocks together through several routing iterations. During each iteration, the router completely routes the entire circuit; and except during the final iteration, each physical routing resource are allowed to be used by several nets at a time. The over-use is called *congestion* and the over-used routing resources are called *congested resources*.

During each iteration, the router connects one net at a time using the maze routing algorithm [Lee61]. For each net, the routing process is guided by a set of metrics that are based on the delay of the net and the congestion of the routing resources from all the previous routing iterations. These metrics are updated after each routing iteration to make already congested resources more costly to use as time progresses. The nets compete for congested resources based on these metrics. When a net is more timing-critical or has no other alternatives, it is given priority for the routing resources that it prefers. When a net is not timing-critical or has other equally good alternatives, it is forced to give up the congested resource that it occupies.

### 2.3 FPGA Architectures

This section provides a detailed description of two FPGA architectures proposed in previous FPGA studies including a conventional FPGA architecture described in [Betz99a] and a datapath-oriented FPGA architecture described in [Cher96]. These two architectures have been chosen because of their influence on the MB-FPGA architecture proposed in Chapter 3. Each FPGA is described in terms of its logic block architecture, its routing architecture, and its CAD flow. Enough details are given, and in some cases specific comments are made, to show

how specific architectural features of these FPGAs relate to the research described in this dissertation. Following these detailed architectural descriptions, several existing datapath-oriented architectures are briefly described. The section is concluded by a brief review of the various techniques used for modeling FPGA delay and area throughout this work.

### 2.3.1 A Conventional FPGA Architecture

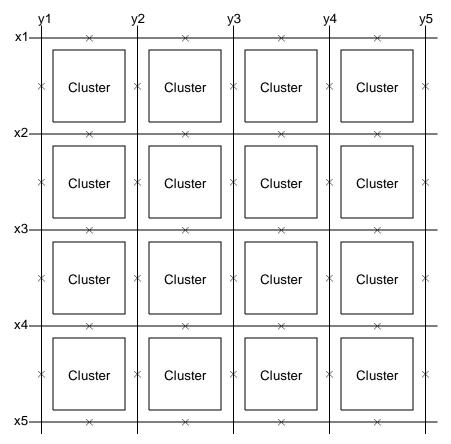

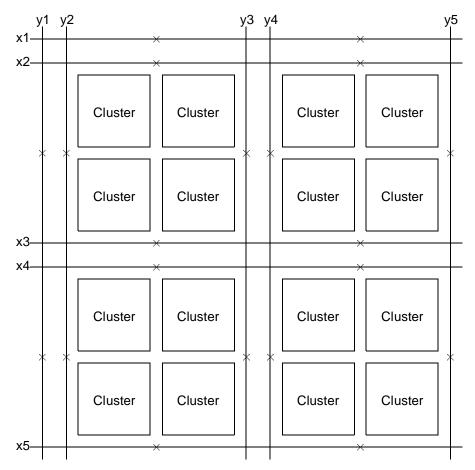

The overall structure of the conventional FPGA architecture proposed in [Betz99a] is shown in Figure 2.2. It consists of a two-dimensional array of programmable logic blocks, called *logic clusters*, with horizontal routing channels between rows of logic blocks and vertical routing channels between columns of logic blocks. At the periphery of the architecture are the I/O blocks, which bring signals from outside into the architecture and send signals generated inside the architecture to the outside. At the intersection of a horizontal routing channel and a vertical routing channel is a switch block, which provides programmable connectivity between the horizontal and vertical channels. This architecture was developed by Betz et. al. as the base architecture for the development of the T-VPACK and the VPR tools described in Section 2.2. The architecture has been used in many architectural studies including [Betz97a] [Betz97b] [Betz98] [Betz99a] [Betz99b] [Betz00] [Chen03] [Cong03] [Harr02] [Li03] [Lin03] [Marq99] [Marq00a] [Marq00b] [Sank99] [Swar98] [Tess02] [Varg99]. In this thesis, the architecture is used as a comparison architecture for the experimental results presented Chapter 5. The structure of each architectural component is described in great detail in [Betz99a], so each of these components is described in turn.

### 2.3.1.1 Logic Clusters

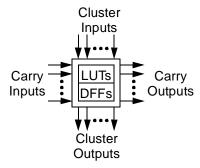

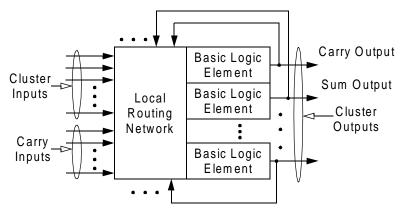

The structure of a logic cluster, illustrated in Figure 2.3, consists of a set of cluster inputs, a set of cluster outputs, and several tightly connected Basic Logic Elements (BLEs). The out-

Figure 2.2: Overview of FPGA Architecture Described in [Betz99a]

puts of the logic cluster are directly connected to the outputs of the corresponding BLEs. The network that connects all the BLEs within a cluster is called the local routing network.

Figure 2.3: Logic Cluster

The detailed structure of a BLE is shown in Figure 2.4. It consists of a LUT, a D-type Flip-Flop (DFF), and a multiplexer. The LUT output is feed into the DFF input. The multiplexer is controlled by a Static Random Access Memory (SRAM) cell and is used to choose either the LUT output or the DFF output as the output of the BLE. The input of the BLE consists of inputs to the LUT and the clock input to the DFF.

Figure 2.4: Basic Logic Element

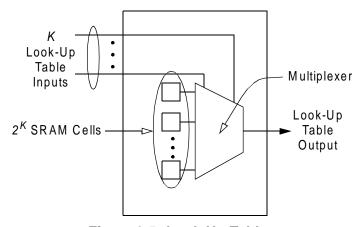

The detailed structure of a LUT is shown in Figure 2.5. The LUT has K inputs and one output where K is specified as an architectural parameter of the architecture. It can be programmed to implement any K-input logic function. The LUT is implemented as a multiplexer whose select lines are the LUT inputs. These inputs select a signal from the outputs of  $2^K$  SRAM cells to generate the LUT output.

Figure 2.5: Look-Up Table

# **Local Routing Network**

The inputs to a local routing network, as shown in Figure 2.3, consist of two types of signals. The first type is an input to the logic cluster. The second type is an output of a BLE in the cluster. Each cluster input or each BLE output connects to exactly one input of the local rout-

ing network. The outputs of the local routing network are connected to the BLE inputs; and there is exactly one network output for every BLE input.

The local routing network has a fully connected topology. Each output of the network can be connected to any input of the network. The topology is widely used in many subsequent FPGA studies including [Marq00b]. The topology also has the advantage of reducing the complexity of the packing tools [Betz99a] since any network input can be connected to any LUT input. Note that commercial devices including Virtex [Xili02], Stratix [Alte02], and Cyclone [Alte02], typically use a depopulated local routing network structure [Lemi01], which uses less area, but requires more complex packing tools.

# 2.3.1.2 Routing Switches

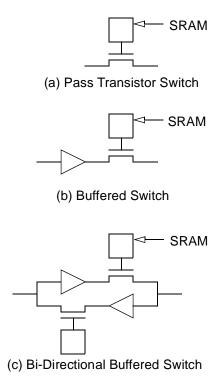

Programmable switches, called routing switches, provide reconfigurable connectivity throughout the architecture. The architecture uses two types of routing switches, the pass transistor switch and the buffered switch. As illustrated in Figure 2.6a, a pass transistor switch consists of a single pass transistor controlled by an SRAM cell. The switch is bi-directional which allows electrical current to flow from either end of the switch to another.

A buffered switch, shown in Figure 2.6b, consists of a buffer, a pass transistor, and an SRAM cell. Since buffers only allow electrical current to flow in one direction, buffered switches are uni-directional. A bi-directional switch can be built out of two buffered switches using the configuration shown in Figure 2.6c. Comparing the two types of switches, pass transistor switches are much smaller in size while buffered switches provide more driving strength and regenerate their input signals. Since pass transistor switches do not regenerate their input signals, the *RC* time constant of a signal grows quadratically as a function of the number of pass transistor switches that the signal passes and the total length of the wire [Betz99a]. As a

Figure 2.6: Routing Switches

result, the pass transistor switches are much slower than the buffered switches for connecting long signal connections.

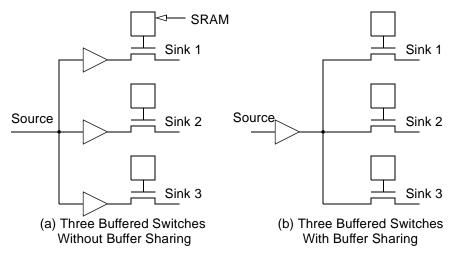

The FPGA architecture uses a technique called buffer sharing to save the implementation area of buffered switches. The technique shares a common buffer among several buffered switches that originate from a common source. An example is shown in Figure 2.7. In the figure, a source is connected to three sinks through three buffered switches. Without buffer sharing, three separate buffers are needed. With buffer sharing, only one buffer is used.

# 2.3.1.3 Routing Channels

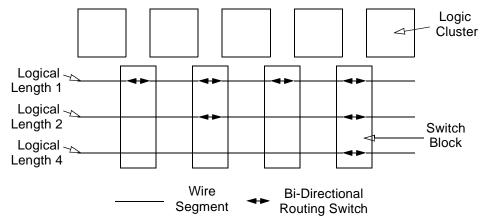

As illustrated in Figure 2.8, each routing channel of the architecture consists of wire segments and routing switches. Note that for clarity only one horizontal routing channel is shown in the figure. The vertical channels that intersect the horizontal channel are not illustrated. The

Figure 2.7: Buffer Sharing

number and types of wire segments and routing switches in each channel are specified as architectural parameters of the architecture. A wire segment starts at one switch block, spans several logic blocks, and ends at another switch block. The number of logic blocks that the segment spans is called the logical length of the segment. Routing switches are located in the switch blocks. They connect wire segments together to form one continuous track, called a routing track, that spans the entire length of the routing channel. In Figure 2.8, three routing tracks are illustrated. The top track contains wire segments of logical length one. The middle track contains wire segments of logical length four.

The choice of wire segment lengths is important to the overall performance of the architecture. Long wire segments are valuable for implementing signals that connect two far away logic blocks. By using long wire segments, a router can reduce the number of routing switches used to implement these long connections, and consequently reduce the delay of these connections. Appropriate combination of segment lengths also can be used to increase the logic density of the FPGA architecture. By evenly matched the segment lengths with net lengths, the

Figure 2.8: Routing Channel

total number of routing switches in any particular implementation of the architecture can be effectively reduced; and consequently the logic density of the architecture can be increased.

As shown in Figure 2.9, the starting positions of the wire segments with the same length are staggered in order to ease the physical layout of the architecture. With staggered starting positions, routing tracks in Figure 2.9 can be rearranged into the topology shown in Figure 2.10 to create identical tiles, each containing one logic block and its neighboring routing resources. With a tile based architecture, the physical layout of FPGAs can be greatly simplified. Instead of designing the layout of an entire FPGA chip, only the layout of one single tile has to be designed. The tile then can be duplicated along a two-dimensional array to create a complete FPGA layout. Note that for clarity only one horizontal routing channel is illustrated in Figure 2.9 and Figure 2.10; nevertheless, the same design principle applies for architectures with both horizontal and vertical routing channels.

#### 2.3.1.4 Switch Blocks

A switch block consists of all the programmable switches located at the intersection of a horizontal routing channel and a vertical routing channel. The FPGA architecture described in [Betz99a] is designed with two types of switch blocks. One type is based on the disjoint topol-

Figure 2.9: Staggered Wire Segments

Figure 2.10: Tiles

ogy [Hsei90] and the other is based on the Wilton topology [Wilt97]. The disjoint topology is more popular and is described here. Note that other newer switch block topologies such as the Imran topology [Masu99] can also be used with the architecture; although they are not further discussed in this work.

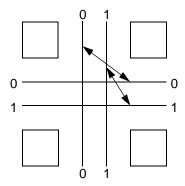

The disjoint topology assumes that all routing channels contain the same number of routing tracks. For two intersecting channels, every track in the horizontal channel is connected to the same track number in the vertical channel by routing switches. The architecture described in [Betz99a] further assumes that the two connecting tracks must have the same segment length.

There are two configurations for two tracks that are connected at a switch block to intersect. In the first configuration shown in Figure 2.11a, both the horizontal segments and the vertical segments end at the switch block. This configuration uses six bi-directional switches to connect the segments together. Two of the six switches are part of the horizontal routing track or the vertical routing track. The remaining four switches are used to connect the horizontal track to the vertical track. In the second configuration, shown in Figure 2.11b, neither the horizontal segment nor the vertical segment ends at the switch block. For this configuration, only one bi-directional switch is needed to connect the horizontal and vertical tracks together. The wire segments are distributed in such a way so that the two connecting tracks can never intersect in the configuration shown in Figure 2.11c, where segments on one track end at the switch block, while the segment on the other track does not.

Figure 2.11: Different Topologies of A Horizontal Track

Meeting A Vertical Track

## 2.3.1.5 Input and Output Connection Blocks

Logic clusters are connected to its neighboring routing channels through connection blocks. A collection of switches that connect all the inputs of a logic cluster to a routing chan-

nel is called an input connection block, while a collection of switches that connect all the outputs of a logic cluster to a routing channel is called an output connection block.

A portion of an input connection block that connect a logic cluster input to a neighboring routing channel is shown in Figure 2.12. It is implemented using a multiplexer. The output of the multiplexer is connected to the input of the logic cluster. The inputs of the multiplexer are connected to a set of routing tracks. Isolation buffers are used to electrically isolate the multiplexer inputs from the routing tracks [Betz99a], shielding the capacitance of the tracks from the input multiplexers.

Figure 2.12: Input Connection Block

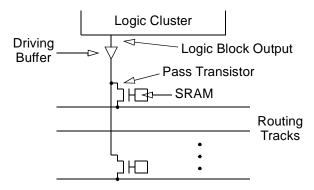

A portion of an output connection block that connects a logic cluster output to a neighboring routing channel is shown in Figure 2.13. It is implemented by connecting the logic cluster output through a shared driving buffer and dedicated pass transistors to a set of routing tracks. The configuration of both the input connection blocks and the output connection blocks are controlled by SRAM cells.

### 2.3.1.6 I/O Blocks

In the FPGA architecture described in [Betz99a], each I/O block contains an input pin for bringing signals into the FPGA and an output pin for sending internal signals to the outside of the FPGA. Both the input pin and the output pin are connected to the routing channels through

Figure 2.13: Output Connection Block

the same output connection block and the same input connection block that are discussed in Section 2.3.1.5, respectively.

## 2.3.2 DP-FPGA — A Datapath-Oriented FPGA Architecture