### FPGA-BASED SOFT VECTOR PROCESSORS

by

Peter Yiannacouras

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy Graduate Department of Electrical and Computer Engineering University of Toronto

Copyright © 2009 by Peter Yiannacouras

#### Abstract

#### FPGA-Based Soft Vector Processors

Peter Yiannacouras

Doctor of Philosophy

Graduate Department of Electrical and Computer Engineering

University of Toronto

2009

FPGAs are increasingly used to implement embedded digital systems because of their low time-to-market and low costs compared to integrated circuit design, as well as their superior performance and area over a general purpose microprocessor. However, the hardware design necessary to achieve this superior performance and area is very difficult to perform causing long design times and preventing wide-spread adoption of FPGA technology. The amount of hardware design can be reduced by employing a microprocessor for less-critical computation in the system. Often this microprocessor is implemented using the FPGA reprogrammable fabric as a soft processor which can preserve the benefits of a single-chip FPGA solution without specializing the device with dedicated hard processors. Current soft processors have simple architectures that provide performance adequate for only the least-critical computations.

Our goal is to improve soft processors by scaling their performance and expanding their suitability to more critical computation. To this end we focus on the data parallelism found in many embedded applications and propose that soft processors be augmented with vector extensions to exploit this parallelism. We support this proposal through experimentation with a parameterized soft vector processor called VESPA (Vector Extended Soft Processor Architecture) which is designed, implemented, and evaluated on real FPGA hardware.

The scalability of VESPA combined with several other architectural parameters can be used to finely span a large design space and derive a custom architecture for exactly matching the needs of an application. Such customization is a key advantage for soft processors since their architectures can be easily reconfigured by the end-user. Specifically, customizations can be made to the pipeline, functional units, and memory system within VESPA. In addition, general purpose overheads can be automatically eliminated from VESPA.

Comparing VESPA to manual hardware design, we observe a 13x speed advantage for hardware over our fastest VESPA, though this is significantly less than the 500x speed advantage over scalar soft processors. The performance-per-area of VESPA is also observed to be significantly higher than a scalar soft processor suggesting that the addition of vector extensions makes more efficient use of silicon area for data parallel workloads.

### Acknowledgements

I would like to thank my advisors Professor Greg Steffan and Professor Jonathan Rose for all their guidance throughout the years. Our weekly meetings were key in directing and executing this research. Also countless writing edits and many dry runs helped improve my written and oral communication. Thank you for all of that, your advice and insights along the way, and also thank you for the opportunity to teach some classes.

My committee including Professor Moshovos and Professor Abdelrahman, as well as Professor Enright Jerger provided useful suggestions and commentary for filling out this work.

Many thanks to Professor Christos Kozyrakis for corresponding with me and sending me the hand-vectorized benchmarks used throughout this work. I would also like to acknowledge the useful input received from Vaughn Betz, David Lewis, and James Ball which helped guide our research direction.

Throughout my six years in LP392 and in the PaCRaT group, it was certainly a pleasure interacting with all my colleagues, thanks for technical breadth, good fun, and stimulating discussions.

Thank you to my parents and brothers for raising me, taking care of me, and looking out for me throughout my life.

To my wife Melinda, thank your for all your love and support, I'm glad to have had you by my side for every step of the way.

# Contents

| Li | List of Tables xi    |             |                                  |    |  |  |  |  |

|----|----------------------|-------------|----------------------------------|----|--|--|--|--|

| Li | List of Figures xiii |             |                                  |    |  |  |  |  |

| 1  | Intr                 | roduction 1 |                                  |    |  |  |  |  |

|    | 1.1                  | Resear      | ch Goals                         | 4  |  |  |  |  |

|    | 1.2                  | Organ       | ization                          | 5  |  |  |  |  |

| 2  | Bac                  | kgrour      | nd                               | 6  |  |  |  |  |

|    | 2.1                  | Microp      | processor Background             | 6  |  |  |  |  |

|    | 2.2                  | Vector      | Processors                       | 7  |  |  |  |  |

|    |                      | 2.2.1       | Vector Instructions              | 8  |  |  |  |  |

|    |                      | 2.2.2       | Vector Architecture              | 9  |  |  |  |  |

|    |                      | 2.2.3       | Vector Lanes                     | 10 |  |  |  |  |

|    |                      | 2.2.4       | Vector Chaining                  | 11 |  |  |  |  |

|    |                      | 2.2.5       | The T0 Vector Processor          | 12 |  |  |  |  |

|    |                      | 2.2.6       | The VIRAM Vector Processor       | 12 |  |  |  |  |

|    |                      | 2.2.7       | SIMD Extensions                  | 15 |  |  |  |  |

|    | 2.3                  | Field-l     | Programmable Gate Arrays (FPGAs) | 15 |  |  |  |  |

|    |                      | 2.3.1       | Block RAMs                       | 16 |  |  |  |  |

|    |                      | 2.3.2       | Multiply-Accumulate blocks       | 16 |  |  |  |  |

|    |                      | 2.3.3       | Microprocessor Cores             | 17 |  |  |  |  |

|    | 2.4                  | FPGA        | Design                           | 17 |  |  |  |  |

|   | <i>1</i> 1 | Integrating Scalar Soft Processors with Off Chin Memory | 30     |

|---|------------|---------------------------------------------------------|--------|

| 4 | Per        | formance Bottlenecks of Scalar Soft Processors          | 39     |

|   | 3.9        | Summary                                                 | <br>38 |

|   | 3.8        | Advantages of Hardware Execution                        | <br>37 |

|   |            | 3.7.3 In-Hardware Debugging                             | <br>37 |

|   |            | 3.7.2 Register Transfer Level (RTL) Simulation          | <br>36 |

|   |            | 3.7.1 Instruction Set Simulation                        | <br>35 |

|   | 3.7        | Verification                                            | <br>35 |

|   | 3.6        | Measurement Error                                       | <br>34 |

|   |            | 3.5.3 Measuring Wall Clock Time                         | <br>33 |

|   |            | 3.5.2 Terasic DE3                                       | <br>33 |

|   |            | 3.5.1 Transmogrifier-4                                  | <br>32 |

|   | 3.5        | Hardware Platforms                                      | <br>32 |

|   |            | 3.4.2 Measuring Clock Frequency                         | <br>31 |

|   |            | 3.4.1 Measuring Area                                    | <br>31 |

|   | 3.4        | FPGA CAD Software                                       | <br>30 |

|   | 3.3        | Software Compilation Framework                          | <br>30 |

|   | 3.2        | Benchmarks                                              | <br>28 |

|   | 3.1        | Overview                                                | <br>27 |

| 3 | Exp        | erimental Framework                                     | 27     |

|   |            | 2.5.5 Soft Vector Processors                            | <br>25 |

|   |            | 2.5.4 Soft Multiprocessors                              |        |

|   |            | 2.5.3 Soft Multi-Threaded Pipelines                     |        |

|   |            | 2.5.2 Soft Multi-Issue Pipelines                        |        |

|   |            | 2.5.1 Soft Single-Issue In-Order Pipelines              |        |

|   | 2.5        | Soft Processors and Related Work                        |        |

|   |            | 2.4.2 Extensible Processors                             |        |

|   |            | 2.4.1 Behavioural Synthesis                             |        |

|   |            | 2.4.1 Rehavioural Synthesis                             | 18     |

|   |                             | 4.1.1    | Scalar Soft Processor Area Breakdown     | 41 |

|---|-----------------------------|----------|------------------------------------------|----|

|   |                             | 4.1.2    | Scalar Soft Processor Memory Latency     | 42 |

|   | 4.2                         | Scalin   | g Soft Processor Caches                  | 44 |

|   | 4.3                         | Soft v   | s Hard Processor Comparison              | 46 |

|   | 4.4                         | Summ     | nary                                     | 49 |

| 5 | $\operatorname{Th}\epsilon$ | vesi     | PA Soft Vector Processor                 | 50 |

|   | 5.1                         | Motiva   | ating Soft Vector Processors             | 50 |

|   | 5.2                         | VESP     | A Design Goals                           | 51 |

|   | 5.3                         | VESP     | A                                        | 53 |

|   |                             | 5.3.1    | MIPS-Based Scalar Processor              | 54 |

|   |                             | 5.3.2    | VIRAM-Based Vector Instruction Set       | 55 |

|   |                             | 5.3.3    | Vector Memory Architecture               | 57 |

|   |                             | 5.3.4    | VESPA Pipelines                          | 59 |

|   | 5.4                         | Meetin   | ng the Design Goals                      | 60 |

|   |                             | 5.4.1    | VESPA Flexibility                        | 60 |

|   |                             | 5.4.2    | VESPA Portability                        | 62 |

|   | 5.5                         | FPGA     | Influences on VESPA Architecture         | 63 |

|   | 5.6                         | Selecti  | ing a Maximum Vector Length (MVL)        | 64 |

|   | 5.7                         | Summ     | nary                                     | 68 |

| 6 | Sca                         | lability | y of the VESPA Soft Vector Processor     | 69 |

|   | 6.1                         | Initial  | Scalability (L)                          | 69 |

|   |                             | 6.1.1    | Analyzing the Initial Design             | 71 |

|   | 6.2                         | Impro    | ving the Memory System                   | 72 |

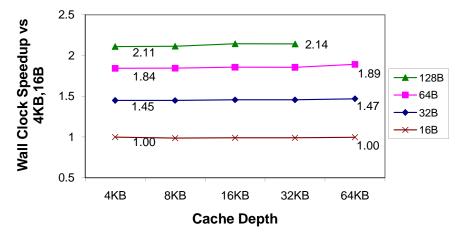

|   |                             | 6.2.1    | Cache Design Trade-Offs (DD and DW)      | 72 |

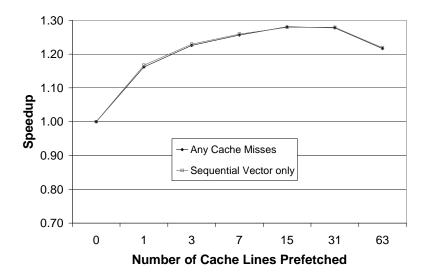

|   |                             | 6.2.2    | Impact of Data Prefetching (DPK and DPV) | 77 |

|   |                             | 6.2.3    | Reduced Memory Bottleneck                | 83 |

|   |                             | 6.2.4    | Impact of Instruction Cache (IW and ID)  | 84 |

|   | 6.3                         | Decou    | pling Vector and Control Pipelines       | 85 |

|   | 6.4  | Impro   | ved VESPA Scalability                                                      | 87  |

|---|------|---------|----------------------------------------------------------------------------|-----|

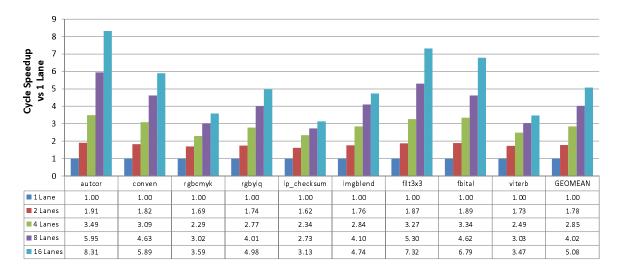

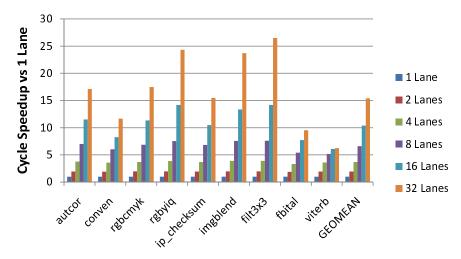

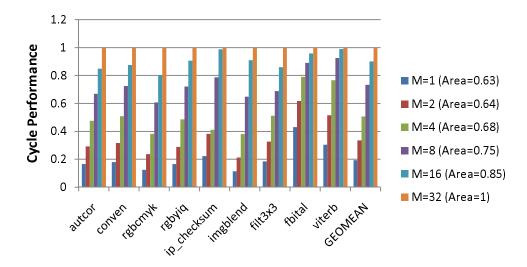

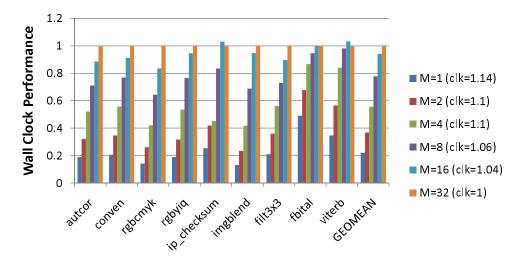

|   |      | 6.4.1   | Cycle Performance                                                          | 87  |

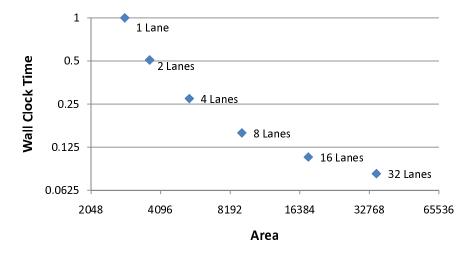

|   |      | 6.4.2   | Clock Frequency                                                            | 89  |

|   |      | 6.4.3   | Area                                                                       | 90  |

|   | 6.5  | Summ    | ary                                                                        | 91  |

| 7 | Exp  | anding  | g and Exploring the VESPA Design Space                                     | 92  |

|   | 7.1  | Hetero  | ogeneous Lanes                                                             | 93  |

|   |      | 7.1.1   | Supporting Heterogeneous Lanes                                             | 93  |

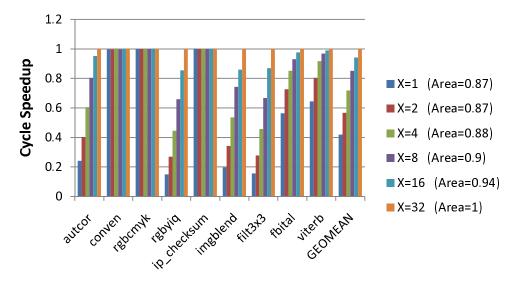

|   |      | 7.1.2   | Impact of Multiplier Lanes (X) $\dots$                                     | 94  |

|   |      | 7.1.3   | Impact of Memory Crossbar (M)                                              | 95  |

|   | 7.2  | Vector  | Chaining in VESPA                                                          | 98  |

|   |      | 7.2.1   | Supporting Vector Chaining                                                 | 99  |

|   |      | 7.2.2   | Impact of Vector Chaining                                                  | 101 |

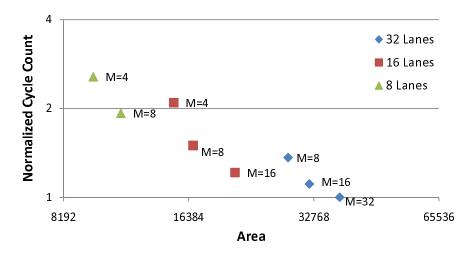

|   |      | 7.2.3   | Vector Lanes and Powers of Two                                             | 105 |

|   | 7.3  | Explo   | ring the VESPA Design Space                                                | 105 |

|   |      | 7.3.1   | Selecting and Pruning the Design Space                                     | 105 |

|   |      | 7.3.2   | Exploring the Pruned Design Space                                          | 108 |

|   |      | 7.3.3   | Per-Application Analysis                                                   | 112 |

|   | 7.4  | Elimin  | nating Functionality                                                       | 116 |

|   |      | 7.4.1   | Hardware Elimination Opportunities                                         | 116 |

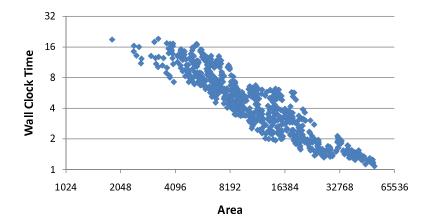

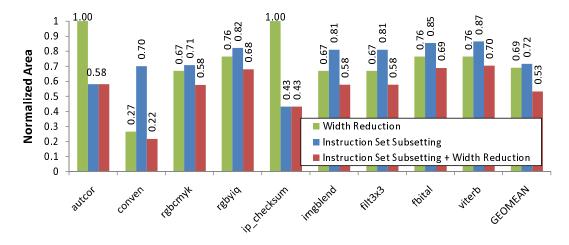

|   |      | 7.4.2   | Impact of Vector Datapath Width Reduction (W) $\ \ldots \ \ldots \ \ldots$ | 118 |

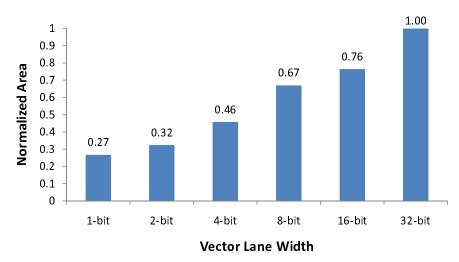

|   |      | 7.4.3   | Impact of Instruction Set Subsetting                                       | 120 |

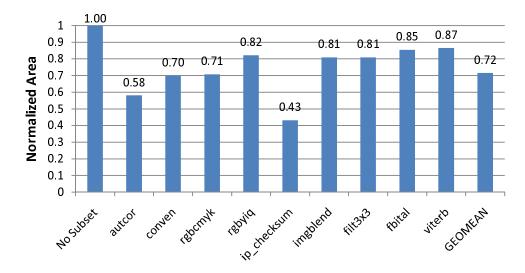

|   |      | 7.4.4   | Impact of Combining Width Reduction and Instruction Set Subsetting         | 121 |

|   | 7.5  | Summ    | ary                                                                        | 123 |

| 3 | Soft | t Vecto | or Processors vs Manual FPGA Hardware Design                               | 125 |

|   | 8.1  | Design  | ning Custom Hardware Circuits                                              | 126 |

|   |      | 8.1.1   | System-Level Design Constraints                                            | 126 |

|   |      | 8.1.2   | Simplifying Hardware Design Optimistically                                 | 127 |

|              | 8.2   | Evalua | ating Hardware Circuits                | 130 |

|--------------|-------|--------|----------------------------------------|-----|

|              |       | 8.2.1  | Area Measurement                       | 131 |

|              |       | 8.2.2  | Clock Frequency Measurement            | 131 |

|              |       | 8.2.3  | Cycle Count Measurement                | 131 |

|              |       | 8.2.4  | Area-Delay Product                     | 132 |

|              | 8.3   | Imple  | menting Hardware Circuits              | 132 |

|              | 8.4   | Comp   | aring to Hardware                      | 133 |

|              |       | 8.4.1  | Software vs Hardware: Area             | 133 |

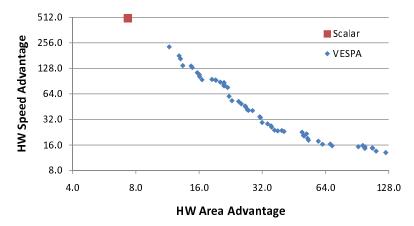

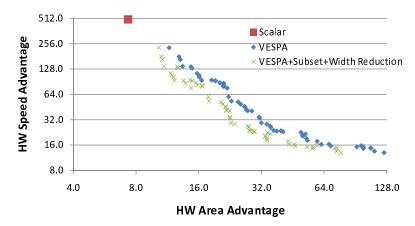

|              |       | 8.4.2  | Software vs Hardware: Wall Clock Speed | 137 |

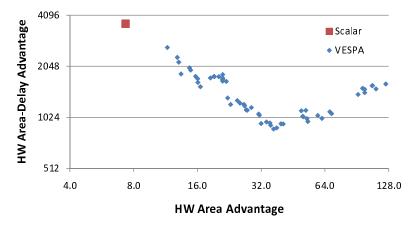

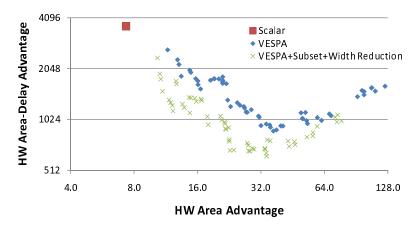

|              |       | 8.4.3  | Software vs Hardware: Area-Delay       | 142 |

|              | 8.5   | Effect | of Subsetting and Width Reduction      | 143 |

|              | 8.6   | Summ   | ary                                    | 145 |

| 9            | Con   | clusio | ns                                     | 146 |

|              | 9.1   | Contri | ibutions                               | 147 |

|              | 9.2   | Future | e Work                                 | 150 |

| A            | Mea   | asured | Model Parameters                       | 152 |

| В            | Raw   | v VES  | PA Data on DE3 Platform                | 155 |

| $\mathbf{C}$ | Inst  | ructio | n Disabling Using Verilog              | 168 |

| Bi           | bliog | raphy  |                                        | 171 |

# List of Tables

| 3.1 | Vectorized benchmark applications                                             |

|-----|-------------------------------------------------------------------------------|

| 3.2 | Benchmark execution speeds                                                    |

| 4.1 | Memory latencies on soft and hard processor systems                           |

| 5.1 | VIRAM instructions supported                                                  |

| 5.2 | Configurable parameters for VESPA                                             |

| 6.1 | Clock frequency of different cache line sizes for a 16-lane VESPA             |

| 6.2 | Performance of VESPA varying lanes from 1 to 32                               |

| 7.1 | Explored parameters in VESPA                                                  |

| 7.2 | Pareto optimal VESPA configurations                                           |

| 7.3 | Configurations with best wall clock performance for each benchmark            |

| 7.4 | Configurations with best performance-per-area for each benchmark              |

| 7.5 | Hardware elimination opportunites across all benchmarks                       |

| 7.6 | Area after width reduction across benchmarks normalized to 32-bit width $119$ |

| 8.1 | Hardware circuit area and performance                                         |

| 8.2 | Area advantage for hardware over various processors                           |

| 8.3 | Speed advantage for hardware over various processors                          |

| 8.4 | Hardware advantages over fastest VESPA                                        |

| A.1 | Load frequency and miss rates across cache size for EEMBC benchmarks 153      |

| A 2 | Store frequency and miss rates across cache size for EEMBC benchmarks 154     |

| В.1  | Area of VESPA system without the vector coprocessor         |

|------|-------------------------------------------------------------|

| B.2  | Area of VESPA system without the vector coprocessor         |

| В.3  | System area of pareto optimal VESPA configurations          |

| B.4  | Performance of pareto optimal VESPA configurations          |

| B.5  | Performance of pareto optimal VESPA configurations (cont'd) |

| B.6  | System area after customizing to AUTCOR                     |

| B.7  | System area after customizing to CONVEN                     |

| B.8  | System area after customizing to RGBCMYK                    |

| B.9  | System area after customizing to RGBYIQ                     |

| B.10 | System area after customizing to IP_CHECKSUM                |

| B.11 | System area after customizing to IMGBLEND                   |

| B.12 | System area after customizing to FILT3x3                    |

| B.13 | System area after customizing to FBITAL                     |

| B.14 | System area after customizing to VITERB                     |

# List of Figures

| 2.1 | Vector processing and vector chaining in space/time                         | 10 |

|-----|-----------------------------------------------------------------------------|----|

| 2.2 | VIRAM processor state                                                       | 1  |

| 3.1 | Overview of measurement infrastructure                                      | 28 |

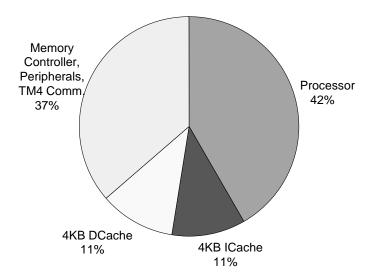

| 4.1 | Area breakdown of scalar SPREE processor with off-chip memory system        | 4  |

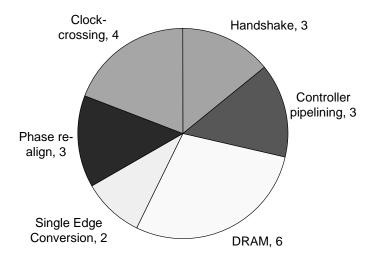

| 4.2 | Memory latency breakdown on TM4                                             | 42 |

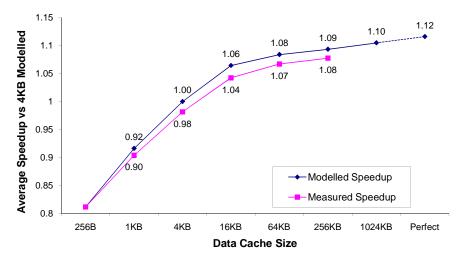

| 4.3 | Average speedup of various direct-mapped data cache sizes                   | 4  |

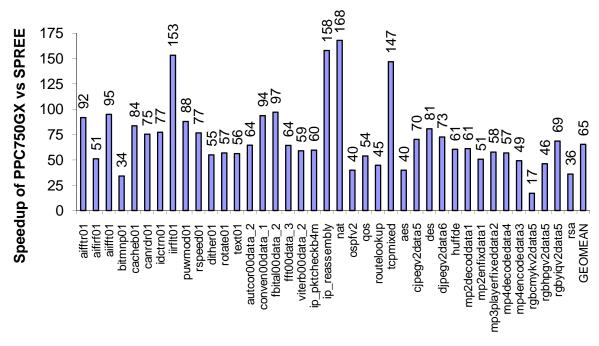

| 4.4 | Performance of IBM PPC 750GX versus SPREE                                   | 47 |

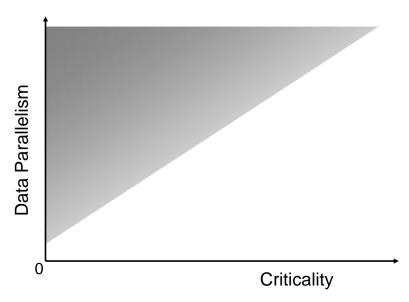

| 5.1 | Application space targeted by VESPA                                         | 52 |

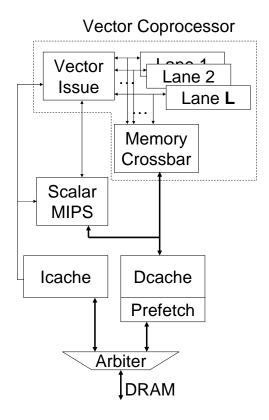

| 5.2 | VESPA processor system block diagram                                        | 53 |

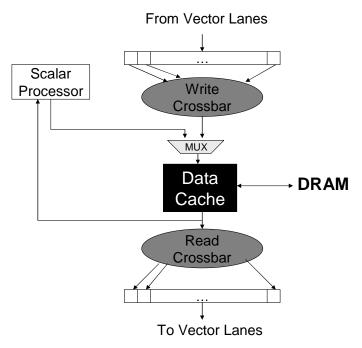

| 5.3 | VESPA memory system diagram                                                 | 56 |

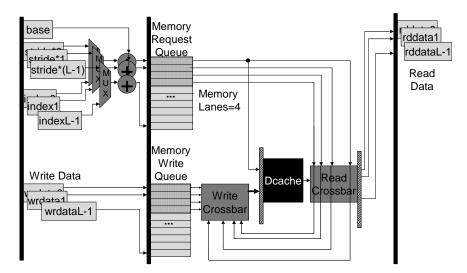

| 5.4 | The VESPA memory unit                                                       | 5  |

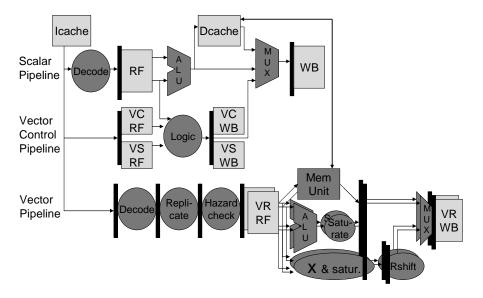

| 5.5 | The VESPA pipelines                                                         | 59 |

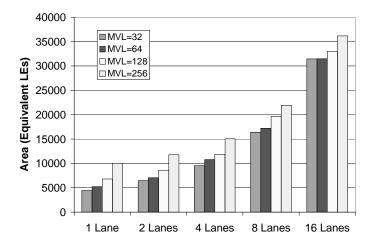

| 5.6 | Area of the vector coprocessor across different MVL and lane configurations | 66 |

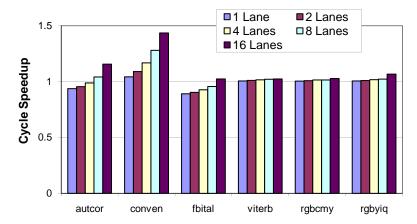

| 5.7 | Cycle speedup measured when MVL is increased from 32 to 256                 | 67 |

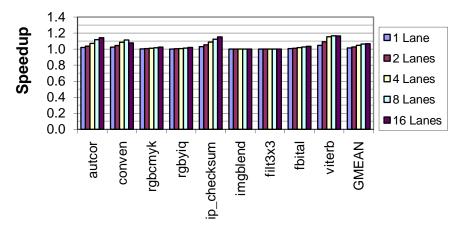

| 6.1 | Performance scalability of inital VESPA design                              | 70 |

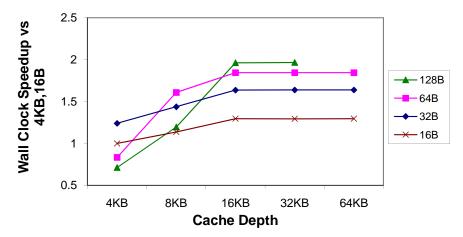

| 6.2 | Average wall clock speedup of various cache configurations                  | 73 |

| 6.3 | Wall clock speedup of various cache configurations for VITERB               | 74 |

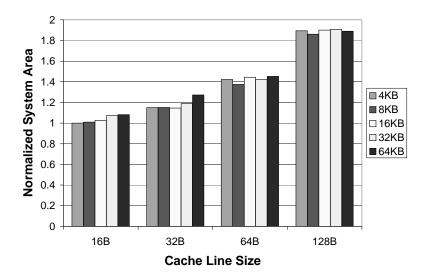

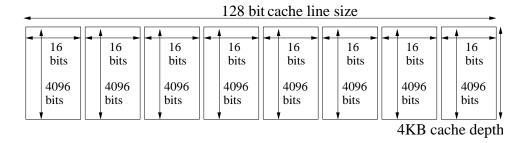

| 6.4 | System area of different cache configurations                               | 75 |

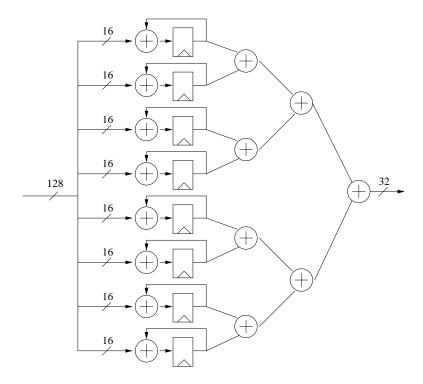

| 6.5 | A wide cache assembled from multiple narrow block RAMs.                     | 76 |

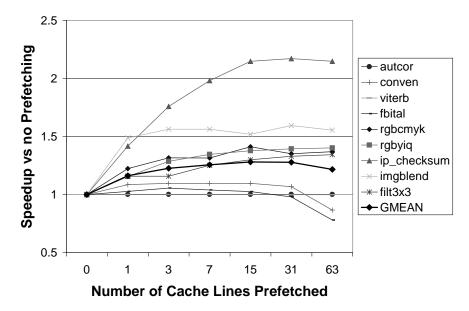

| 6.6  | Average speedup for different prefetching triggers                               |

|------|----------------------------------------------------------------------------------|

| 6.7  | Speedup of prefetching fixed number of cache lines                               |

| 6.8  | Speedup of vector length prefetcher                                              |

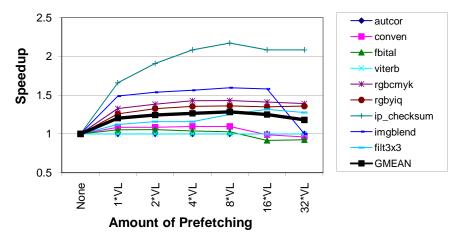

| 6.9  | Analysis of memory and miss cycles before/after cache and prefetcher 83 $$       |

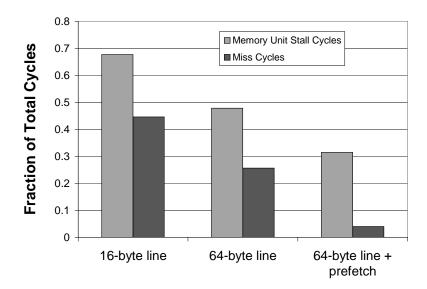

| 6.10 | Average cycle performance across various icache configurations                   |

| 6.11 | Performance improvement after decoupling the vector control pipeline 86 $$       |

| 6.12 | Performance scalability of improved VESPA                                        |

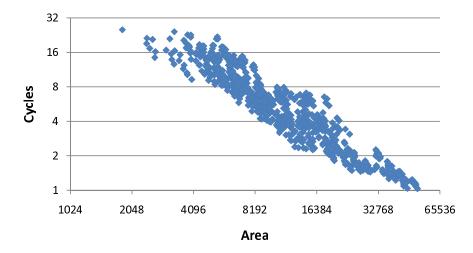

| 6.13 | Performance/area design space of 1-32 lane VESPA                                 |

| 7.1  | Performance impact of varying X                                                  |

| 7.2  | Cycle performance of various memory crossbar configurations                      |

| 7.3  | Cycle performance versus area for various memory crossbar configurations 97 $$   |

| 7.4  | Wall clock performance of various memory crossbar configurations                 |

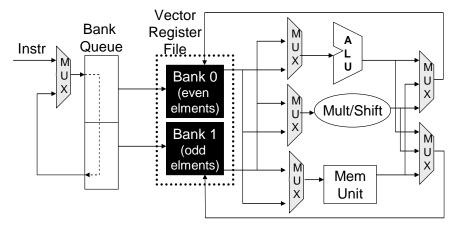

| 7.5  | Element-partitioned vector register file banks shown for 2 banks 100             |

| 7.6  | Vector chaining support for a 1-lane VESPA processor with 2 banks 100            |

| 7.7  | Cycle performance of different banking configurations                            |

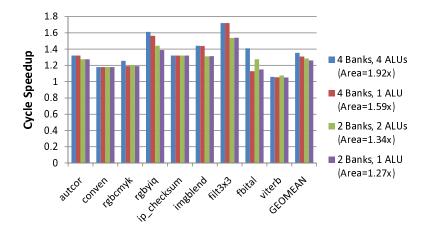

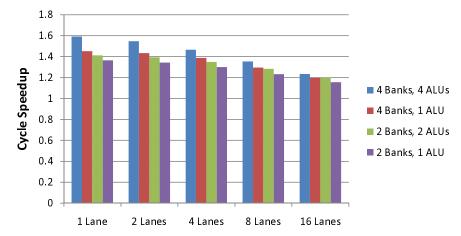

| 7.8  | Average cycle performance for different chaining configurations                  |

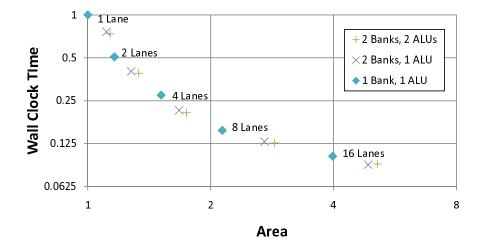

| 7.9  | Performance/area space of varying chaining and lane configurations $104$         |

| 7.10 | Average normalized wall clock time and area VESPA design space 107               |

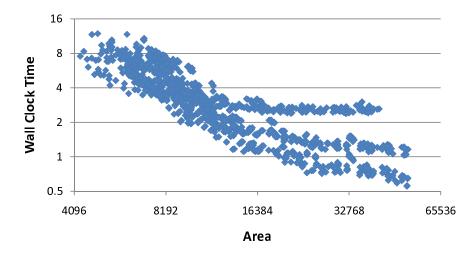

| 7.11 | Average normalized cycle count and area VESPA design space after pruning. $$ 109 |

| 7.12 | Average wall clock time and area of pruned VESPA design space                    |

| 7.13 | Area of width-reduced VESPA processors                                           |

| 7.14 | Area of the vector coprocessor after instruction set subsetting                  |

| 7.15 | Area of the vector coprocessor after subsetting and width reduction 121          |

| 7.16 | Normalized clock frequency of VESPA after subsetting and width reduction $122$   |

| 8.1  | Hardware circuit implemented for IP_CHECKSUM                                     |

| 8.2  | Area-performance design space of scalar and pareto-optimal VESPAs 138            |

| 8.3  | Area-delay product of VESPA versus hardware                                      |

| 8.4  | Area-performance design space after subsetting and width reduction               |

8.5 Area-delay product versus hardware after subsetting and width reduction. . . . . 144

# Chapter 1

## Introduction

Field-Programmable Gate Arrays (FPGAs) are commonly used to implement embedded systems because of their low cost and fast time-to-market relative to the creation of fully-fabricated VLSI chips. FPGAs also provide superior speed/area/power compared to a microprocessor, although the hardware design necessary to achieve this is cumbersome and requires specialized knowledge making it difficult for average programmers to adopt FPGAs. Specifically, the detailed cycle-to-cycle description necessary for design in a hardware description language (HDL) requires programmers to comprehend both their application and hardware substrate with very low-level detail. In addition, hardware design is accompanied with very limited-scope debugging and complexities such as circuit timing and clock domains. To enable rapid and easy access to this better-performing FPGA technology, we are motivated to simplify the design of FPGA-based systems by leveraging the high-level programming languages and single-step debugging features of software design.

Most FPGA-based systems include a microprocessor at the heart of the system, and approximately 25% contain a processor implemented using the FPGA reprogrammable fabric itself [3], such as the Altera Nios II [5] or Xilinx Microblaze [67]. These soft processors are inefficient compared to their hard counterparts but have some key advantages. Compared to using both an FPGA and a separate microprocessor chip, soft processors

preserve a single-chip solution and avoid the increased board real estate, latency, cost, and power of using a second chip. An alternative approach to addressing these issues is to embed hard microprocessors and FPGA fabric on a single device such as the Xilinx Virtex II Pro [68]. But this specializes the device resulting in multiple device families for meeting the needs of designers who may want varying numbers of processors or even specific architectural features. Maintaining these device families as well as the design and/or licensing of the processor core itself contribute to increasing the cost of FPGA devices. A soft processor avoids these increased costs while maintaining the benefits of a single-chip solution.

The software design environment provided by soft processors can be used for quickly implementing system components which do not require highly-optimized hardware implementations, and can instead be implemented with less effort in software executing on a soft processor. In this thesis, we leverage the inherent configurability of a soft processor to adapt its architecture and match the properties found in the application to achieve better performance and area. These improved soft processors can better compete with the efficiencies gained through hardware design and be used to implement non-critical computations in software rather than through laborious hardware design. As more computations within a digital system are implemented in software on a soft processor, the overall time required to implement the digital system is reduced hence achieving our goal of making FPGAs more easily programmable.

Simplifying hardware design is a goal analogous to that of behavioural synthesis which aims to automatically compile applications described in a high-level programming language to a custom hardware circuit. However pursuing this goal within a processor framework provides several advantages. First it provides a more fluid design methodology allowing designers to manually optimize the algorithm, code, compiler, assembly output, and architecture. Behavioural synthesis tools combine these into one black box tool which outputs a single result with few options for navigating the immense design space along each of these axes. Second, the intractable complexities in behavioural synthesis

thesis can result in poor results that may be improved from the knowledge gained by customizing within a processor framework. Third, processors provide single-step debugging infrastructure making it far easier to diagnose problems within the system. Fourth, processors provide compiled libraries for easily sharing software and maintaining optimization effort. In contrast, the output from behavioural synthesis depends heavily on surrounding components making a given synthesized task questionably portable. Finally, a processor provides full support for ANSI C while behavioural synthesis typically do not. Overall, processors provide a fluid and portable framework that can be immediately leveraged by soft processors to simplify FPGA design.

The architecture of current commercial soft processors are based on simple single-issue pipelines with few variations, limiting their use to predominantly system control tasks. To support more compute-intensive tasks on soft processors, they must be able to scale up performance by using increased FPGA resources. While this problem has been thoroughly studied in traditional hard processors [28], an FPGA substrate leads to different trade-offs and conclusions. In addition, traditional processor architecture research favoured features that benefit a large application domain, while in a soft processor we can appreciate features which benefit only a few applications since each soft processor can be configured to exactly match the application it is executing. These key differences motivate new research into scaling the performance of existing soft processors while considering the configurability and internal architecture of FPGAs.

Recent research has considered several options for increasing soft processor performance. One option is to modify the amount and organization of the pipelining in existing single-issue soft processors [70, 71] which provide limited performance gains. A second option is to pursue VLIW [31] or superscalar [12] pipelines which are limited due to the few ports in FPGA block RAMs and the available instruction-level parallelism within an application. A third option is multi-threaded pipelines [16, 21, 38] and multiprocessors [55, 62] which exploit thread-level parallelism but require complicated parallelization of the software. In this thesis we propose and explore vector extensions for soft proces-

sors which can be relatively easily programmed to allow a single vector instruction to command multiple datapaths. An FPGA designer can then scale the number of these datapaths, referred to as *vector lanes*, in their design to convert the data parallelism in an application to increased performance.

#### 1.1 Research Goals

The goal of this research is to simplify FPGA design by making soft processors more competitive with manual hardware design. This thesis proposes that soft vector processors are an effective means of doing so for data parallel workloads, which we aim to prove by setting the following goals:

- 1. To efficiently implement a soft vector processor on an FPGA.

- To evaluate the performance gains achievable on real embedded applications. FP-GAs are frequently used in the embedded domain so this application-class is well-suited for our purposes.

- To provide a broad area/performance design space with fine-grain resolution allowing an FPGA designer to select a soft vector processor architecture that meets their needs.

- 4. To support automatic customization of soft vector processors to a specific application, by enabling the removal of general purpose area overheads.

- 5. To quantify the area and speed advantages of manual hardware design versus a soft vector processor and a scalar soft processor.

To satisfy the first goal we implement a full soft vector processor called *VESPA* (*Vector Extended Soft Processor Architecture*) and demonstrate its scalability in real hardware. For the second goal we execute industry-standard benchmarks on several VESPA configurations. For the third goal we extend VESPA with parameterizable architectural options

that can be used to further match an application's data-level parallelism, memory access pattern, and instruction mix. For the fourth we enhance VESPA with the capability to remove hardware for unused instructions and datapath bit-widths. Finally for the last goal, we compare VESPA to manually designed hardware and show it can significantly reduce the performance gap over scalar soft processors, hence luring more designers into using soft processors and avoiding laborious hardware design.

### 1.2 Organization

This thesis is organized as follows: Chapter 2 provides necessary background and summarizes related work. Chapter 3 describes the infrastructure components used in this thesis. Chapter 4 analyzes bottlenecks in current scalar soft processor architectures and motivates the need for additional computational power. Chapter 5 describes the VESPA processor. Chapter 6 shows that with accompanying architectural improvements, VESPA can scale within a large performance/area design space. Chapter 7 explores the VESPA design space by implementing heterogeneous lanes, vector chaining, and automatic removal of unused hardware. Chapter 8 compares VESPA to a scalar soft processor and to manual hardware design, quantifying the area and performance gaps and demonstrating how significant strides are made towards the performance of manual hardware design over scalar soft processors. Finally, Chapter 9 concludes and suggests future avenues for research.

# Chapter 2

# Background

This chapter provides necessary background on microprocessors, vector processors, and FPGAs. It also describes soft processors and summarizes research related to this thesis.

## 2.1 Microprocessor Background

Microprocessors have radically changed the world we live in and are integral parts of the semiconductor industry. Compared to chip design, they provide a low cost path to silicon by serving multiple applications with a single general purpose device which can be easily programmed using a simple sequential programming model. Microprocessor improvements have been achieved by primarily two methods: (i) shrinking the minimum width of manufacturable transistors which increases the processor clock rate and reduces its size; and (ii) improving the architecture of microprocessors by adding structures for supporting faster execution. In this thesis we focus only on the latter approach.

Many architectural variants and enhancements have been thoroughly studied [28] in conventional microprocessors. Architectural improvements such as branch predictors alleviate pipeline inefficiencies, but scalable performance gains are achievable only by executing operations spatially rather than temporally over the processor datapath. The parallelism necessary for spatial computation comes in three forms:

• Instruction Level Parallelism (ILP): When an instruction produces a result not

used by a later instruction in the same instruction stream, those two instructions exhibit instruction level parallelism which allows them to be executed concurrently.

- Data Level Parallelism (DLP): When the same operation is performed over multiple data elements allowing all operations to be performed concurrently.

- Thread Level Parallelism (TLP): When multiple instruction streams exist they can be executed concurrently except for memory operations which may access data shared between both instruction streams.

ILP has been heavily leveraged in creating aggressive out-of-order superscalar microprocessors, until three factors combined to prevent further improvements using this approach: the complexity involved in exploiting this ILP, the growing performance gap between processors and memory (known as the memory wall) [66], and most recently, the limited power density that can be dissipated by semiconductor chips (known as the power wall) [20]. Since then the microprocessor industry has turned to solving the parallel programming problem in hopes of simplifying the extraction of TLP. With multiple threads an architect can build a more efficient multithreaded processor which time-multiplexes the different threads onto a single datapath. Additionally multiple processors, or multiprocessors, can be used to scale performance by simultaneously executing threads on dedicated processor cores. Presently all mainstream processors now provide 4 or 8 cores such as the Intel Core i7 family [29]. Exploiting either ILP and TLP can be used to scale performance in soft processors; later in this chapter we discuss related work in that area as well as its suitability to FPGA architectures. This thesis focuses primarily on exploiting the DLP found in many of the embedded applications in which FPGAs are employed.

#### 2.2 Vector Processors

DLP has been historically exploited through a vector processor which is designed for efficient execution of DLP workloads [28]. Vector processors have existed in supercomputers

Listing 2.1: C code of array sum.

```

int a[16], b[16], c[16];

...

for (int i=0; i<16; i++)

c[i]=a[i]+b[i];</pre>

```

since the 1960s and were the highest-performing processors for decades. The fundamental concept behind vector processors is to accept and process *vector instructions* which communicate some variable number of homogeneous operations to be performed. This concept and its advantages are discussed below in the context of an example.

#### 2.2.1 Vector Instructions

Vector processors provide direct instruction set support for operations on whole vectors—i.e., on multiple data elements rather than on a single scalar value. These instructions can be used to exploit the DLP in an application to essentially execute multiple loop iterations simultaneously. Listing 2.1 shows an example of a data parallel loop that sums two 16 element arrays. The assembly instructions necessary to execute this loop on a scalar processor is shown in Listing 2.2. Tracing through this code shows that a total of 148 machine instructions need to be executed, with 80 of them responsible for managing the loop and advancing pointers to the next element.

With support for vector instructions, a vector processor can execute the same loop with just the 8 instructions shown in Listing 2.3. After initializing the pointers, the current vector length is set to 16 since the loop operates on 16-element arrays. Following this, the vector instructions for loading, adding, and storing the resulting 16-element array back to memory are executed. Note that due to finite hardware resources, a vector processor exposes its internal maximum vector length MVL in a special readable register. In this code we assume MVL is greater than or equal to 16, otherwise the loop must be strip-mined into multiple iterations of MVL sized vectors. Nonetheless, the savings in executed instructions is dramatic due to: (i) the multiple operations encapsulated in a

Listing 2.2: Pseudo-MIPS assembly of array sum. Destination registers are on the left.

```

move

r1, a

r2, b

move

r3, c

move

move

r7,0

loop_add:

load.w

r4,(r1)

load.w

r5, (r2)

add

r6, r4, r5

r6,(r3)

stor.w

add

r7, r7, 1

# Loop overhead

add

r1, r1, r7

# Advance pointer

add

# Advance pointer

r2, r2, r7

add

r3, r3, r7

# Advance pointer

r7,16,loop_add

blt

# Loop overhead

```

Listing 2.3: Vectorized assembly of array sum. For simplicity it is assumed the maximum vector length is greater than or equal to 16.

```

move vbase1, a

move vbase2, b

move vbase3, c

move vl,16  #Set vector length to 16

vload.w vr4,(vbase1)

vload.w vr5,(vbase2)

vadd vr6,vr4,vr5

vstor.w vr6,(vbase3)

```

single vector instruction; and (ii) the savings in loop overheads and pointer advancing.

Listing 2.3 shows the use of one possible vector instruction set. Many different vector instruction sets have been extensively researched, including in modern processors [24]. Simultaneous research into the architectures that supports these vector instructions was also thoroughly performed and is described next.

#### 2.2.2 Vector Architecture

The vector architecture is responsible for accepting a stream of variable-lengthed vector instructions and completing their associated operations as quickly as possible. We now describe several architectural modifications that can be used to achieve this; a more comprehensive summary can be found in [28].

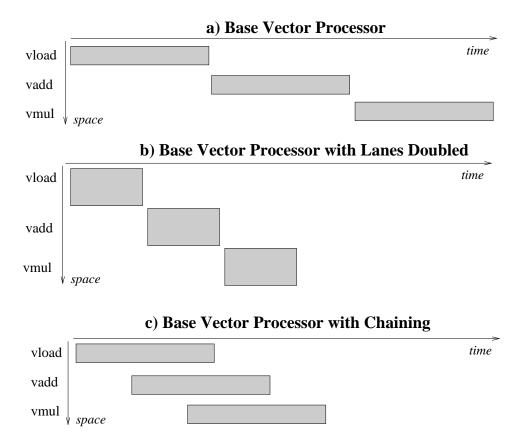

Figure 2.1: Comparing vector execution of doubling lanes (b) and chaining (c) against a base vector processor (a). The area of the boxes represents the amount of work for each instruction. The base vector processor in (a) waits for each vector instruction to complete before executing the next. In (b), doubling the number of lanes allows more of the work to be computed spatially on the additional lanes, this makes the instructions twice as tall in space and half as long in time. Chaining allows the work to be overlapped with the work of other instructions as seen in (c). The execution is staggered so that at any point in time each instruction is executing on different element groups.

#### 2.2.3 Vector Lanes

The most important architectural feature of a vector processor is the number of vector datapaths or vector lanes. A single lane can operate on a single element of the vector at a time in a pipelined fashion; with more vector lanes a vector processor can perform more of the element operations in parallel hence increasing performance. For example, the vadd instruction in Listing 2.3 encodes 16 additions to be performed across 16 elements. A vector processor with 8 lanes can then execute 8 element operations at a time—we refer to this group of elements as an element group. After the first element group with

indices 0-7 is processed, the next element group with indices 8-15 is processed and the vadd instruction completes in two cycles.

Figure 2.1 shows a visual depiction of the effect of doubling lanes on vector instruction execution. Compared to (a), doubling the number of lanes in (b) results in twice as much spatial execution of the vector instructions, resulting in half as much execution time. The number of lanes is a powerful parameter for trading silicon area (used for spatial execution on the vector lanes) and performance (the time needed to complete the vector instruction). Note that the number of lanes is always a power of two, otherwise accessing an arbitrary element requires division and modulo operations to be performed.

#### 2.2.4 Vector Chaining

Vector chaining provides another axis of scaling performance in addition to increasing the number of lanes. Chaining allows multiple vector instructions to be executed simultaneously; the concept was first presented in the Cray-1 [56]. Using Listing 2.3 as an example, the first element group of the vadd instruction does not need to wait for the vload instruction preceding it to complete in its entirety. Rather, after the vload has loaded the first element group into vr5, the vadd can execute its first element group since its data is ready. Similarly the first element group for the stor can be stored as soon as the vadd completes that element group. With this concept the throughput of the vector processor can scale beyond the available number of lanes.

Figure 2.1 c) shows the effect of chaining compared to part a) of the same figure. After an initial set of element groups have been processed, the next instruction can execute alongside the previous. A continuous supply of vector instructions can lead to a steady-state of multiple vector instructions in flight. However successful vector chaining requires (i) available functional units, (ii) read/write access to multiple vector element groups, and (iii) vector lengths long enough to access multiple element groups. The first is achieved by replicating functional units, specifically the arithmetic and logic unit (ALU). The second can be achieved by implementing many read/write ports to the vector

register file or many register banks each with their own read/write ports. Historically vector supercomputers used the latter approach, while research in more modern single-chip implementations of vector architectures have resorted to the former [6] as discussed below. Finally the third requires applications with enough DLP to use vector lengths longer than the number of lanes.

#### 2.2.5 The T0 Vector Processor

While traditional vector supercomputers spanned multiple processor and memory chips, Asanovic et. al. proposed harnessing advances in CMOS technologies to implement vector processors on a single chip with the aim of including them as add-ons to existing scalar microprocessors [6, 7]. The 8-lane T0 vector processor was implemented with up to 3-way chaining for a peak of 24 operations per cycle while issuing only one vector instruction per cycle. A key contribution was in the reduction of the large delays historically associated with starting and completing a vector instruction. These delays require a high-degree of data parallelism to be amortized, but with the shorter electrical delays of a single-chip design, the delays were greatly reduced enabling new application classes to exploit vector architectures. The T0 also first realized the area efficiency gains of using a many-ported vector register file to support chaining rather than a many-banked register file. Finally, while caches were not typically used in traditional vector supercomputers, they are further motivated in the T0 which connects to DRAM instead of SRAM.

#### 2.2.6 The VIRAM Vector Processor

The IRAM project [1] investigated placing memory and microprocessors on the same chip, which lead to the design of a processor architecture that can best utilize the resulting high-bandwidth low-latency access to memory. The group selected a vector processor based on the T0, but optimized it for this memory system and for the embedded application domain creating VIRAM [32, 33, 34, 35, 60]. The VIRAM vector processor was shown to provide faster performance across several EEMBC industry-standard benchmarks compared to

superscalar and out-of-order processors while consuming less energy. The vector unit is attached as a coprocessor to a scalar MIPS processor with both connected to the on-chip DRAM. The complete system is manufactured in a 180nm CMOS process. The VIRAM vector processor has 4 lanes each 64-bits wide but can be reconfigured into as many as 16 16-bit vector lanes. The architecture is massively pipelined with 15 stages in each vector lane to tolerate the worst case on-chip memory latency. With this pipelining and the low-latency on-chip DRAM, no cache is used in VIRAM. The soft vector processor implemented in this thesis is based on the VIRAM instruction set which is described in more detail below.

#### 2.2.6.1 VIRAM Instruction Set

VIRAM supports a full range of integer and floating-point vector operations including absolute value, and min/max instructions. Fixed-point operations are directly supported by the instruction set as well, providing automatic scaling and saturation hardware. VIRAM also supports predication, meaning each element operation in a vector instruction has a corresponding flag indicating whether the operation is to be performed or not. This allows loops with if/else constructs to be vectorized. Finally VIRAM has memory instructions for describing consecutive, strided, and indexed memory access patterns. The latter can be used to perform scatter/gather operations albeit with significantly less performance than consecutive accesses.

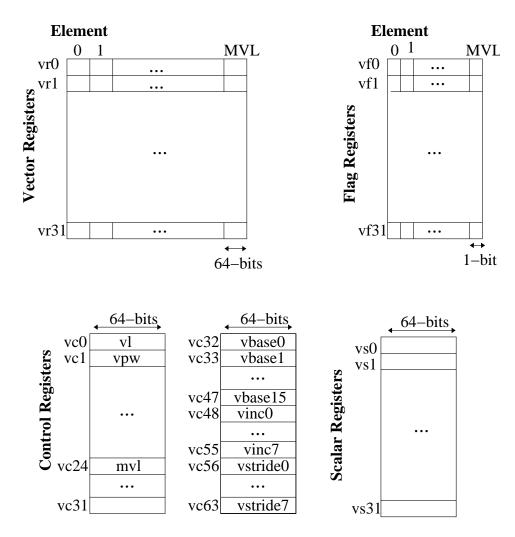

Figure 2.2 shows the vector state in VIRAM consisting of the 32 vector vr registers, the 32 flag vf registers, the 64 control vc registers, and the 32 vs scalar registers. The vector registers are used to store the vectors being operated on, while the flag registers store the masks used for predication. The control registers are each used for dedicated purposes throughout various parts of the vector pipeline. For example vc0, also referred to as v1, holds the vector length of the current vector instruction, while vc24 or mv1 is used to specify the maximum vector length of the processor (and hence this register is read-only). The vc1 or vpw register stores the width of each element used to determine

Figure 2.2: Processor state of VIRAM vector coprocessor consisting of vector registers, flag registers, control registers, and scalar registers. Our VESPA soft vector processor uses this same state though with widths of 32 bits instead of 64 bits.

the datapath width of the vector lanes. As seen in the figure, this is normally 64-bits, but can be modified to create narrower elements down to 16-bits which is automatically accompanied by a corresponding 4x increase to mvl.

The control registers also include dedicated registers for memory operations. The vbase0-15 registers can store any base address which can be auto-incremented by the value stored in the vinc0-7 registers. The vstride0-7 registers can store different constant strides for specifying strided memory accesses. For example, if v1 was 16 and the instruction vld.w vr0, vbase1, vstride2, vinc5 was executed, the vector processor would load the 16 elements starting at vbase1 each separated by vstride2 words, store

them in vr0, and finally update vbase1 by adding vinc5 to it. More detailed information can be found in the VIRAM instruction set manual [60]. Note the implementation of VIRAM used in VESPA uses exactly the same vector state as in Figure 2.2 except that it is 32-bits instead of 64-bits, and without supporting the width reconfiguration using vpw.

#### 2.2.7 SIMD Extensions

Modern microprocessors exploit data-level parallelism via SIMD (single-instruction, multiple-data) support, including IBM's Altivec, AMD's 3DNow!, MIPS's MDMX, and Intel's MMX/SSE/AVX. SIMD support is very similar to vector support except that it is typically limited to a fixed and small number of elements which is exposed to the application programmer. In contrast, true vector processing abstracts from the software the actual number of hardware vector lanes, instead providing a machine-readable MVL parameter (discussed below) for limiting vector lengths. This is partly due to the longer vector lengths typically used in vector processing which are permitted to exceed the amount of hardware resources so that future vector architectures could add hardware resources to exploit the DLP without software modification. In addition, vector processors are typically equipped with a wider range of vector memory instructions that can explicitly describe different memory access patterns. These features make vector processing appealing for current microprocessors instead of the SIMD extensions used to date [24].

## 2.3 Field-Programmable Gate Arrays (FPGAs)

Field-Programmable Gate Arrays are prefabricated programmable logic devices often composed of lookup table based programmable logic blocks connected by a programmable routing network. Using these elements an FPGA can implement any digital logic circuit making them (originally) useful for implementing miscellaneous glue logic. As FPGAs have grown in capacity they have become capable of implementing complete embedded

systems. To augment their area efficiency and speed for certain operations, FPGA vendors have included dedicated circuits for better implementing certain operations that are typical in an embedded system. These dedicated circuits presently include flip flops, random access memory (RAM), multiply-accumulate logic, and microprocessor cores [36]. We describe these in more detail below since they are used extensively in soft processors, or in the case of the microprocessor cores, as an alternative to soft processors.

#### 2.3.1 Block RAMs

The block RAMs in FPGAs provide efficient large storage structures which would otherwise require large amounts of lookup tables and flip flops to implement. While the capacity of a given block RAM is fixed, multiple block RAMs can be connected to form larger capacity RAM storage. Additional flexibility is available in the width and depth of the block RAMs allowing them to be configured as deep and narrow 1-bit memories, or shallow and wide 32-bit memories. A key limitation of block RAMs is they have only two access ports allowing just two simultaneous reads or writes to occur. This limitation inhibits soft processor architectures which require many-ported register files to sustain multiple instructions in flight. As a result most soft processor research has been on single-issue pipelines or multiprocessors.

#### 2.3.2 Multiply-Accumulate blocks

The multiply-accumulate blocks, referred to also as *DSP blocks*, have dedicated circuitry for performing multiply and accumulate operations. The smallest such blocks are 9 or 18 bits wide and can be combined to perform multiply-accumulate for larger inputs. In this work we use the multiply-accumulate blocks to efficiently implement the multiplier functional units in a processor, which we also use to perform shift operations since barrel shifters are inefficient when built out of lookup tables.

#### 2.3.3 Microprocessor Cores

Some FPGAs include one or two microprocessor cores implemented directly in silicon with the FPGA programmable fabric surrounding it [4, 68]. These hard processors provide superior performance relative to a soft processor but also have many disadvantages: (i) the number of hard processors on an FPGA may be insufficient or too many resulting in wasted silicon; (ii) the architecture is fixed making it difficult to satisfy all application domains; (iii) the cost of the FPGA is increased since vendors must design, build, and/or license a processor core; and (iv) the FPGA is specialized often producing multiple families of devices with/without processor cores which further increases design and inventory costs. As a result soft processors have seen significant uptake by both vendors and FPGA users, motivating research into improving soft processors.

### 2.4 FPGA Design

The typical FPGA design flow begins with an HDL language such as Verilog or VHDL which describes the desired circuit. FPGA vendors provide computer-aided design (CAD) tools for parsing this description and efficiently mapping the circuit onto the FPGA fabric. This design process is far more difficult than the software-based flows of microprocessors. An FPGA designer must specify the cycle-to-cycle behaviour of each component of the system, and the interaction between these components creates many opportunities for errors. Unlike the single-stepping debug infrastructure in a microprocessor, debugging a hardware design is very difficult. A logic analyzer can be used to capture a snapshot of a few signals at some event, but finding the erroneous event among its many symptoms can involve weeks of effort. In addition, an FPGA designer must respect the timing constraints of the system. Doing so requires pipelining, retiming, and other optimizations which can create more state and hence increased opportunities for errors. Overall, the biggest bottleneck of the FPGA design process is the design and verification of the desired system. Unlike an ASIC, fabrication is performed in minutes to days depending on the

circuit size and the compilation time of the FPGA CAD tools.

#### 2.4.1 Behavioural Synthesis

Many efforts have been made to simplify the FPGA design flow. One option adopted by the FPGA vendors is to use processors (soft or hard) to implement less critical components and system control tasks—where errors can be very difficult to find if implemented in a hardware finite state machine (FSM). But another option which has been extensively researched in both FPGAs and ASICs is to automatically derive hardware implementations from a C-like sequential program. This is referred to as behavioural synthesis and its goal is aligned with our own goal of simplifying FPGA-design by using sequential programming for soft processors instead. Some examples of behavioural synthesis tools and languages include Handel-C [59], Catapult-C [43], Impulse C [52], and SystemC [51]. Altera has their own behavioural synthesis tool called C2H [40] which can convert C functions into hardware accelerators attached to a Nios II soft processor. Previous work has shown that soft vector processors can scale significantly better than C2H-generated accelerators even when manual code-restructuring is performed to aid C2H [75]. The state-of-the-art behavioural synthesis results in overheads due to the intractable nature of the problem including the pointer aliasing problem. These complexities have limited the quality of results available from behavioural synthesis tools.

We believe that customized processors will continue to be useful until and even after high-quality behavioural synthesis tools exist because of the following advantages.

1. Fluid Design Methodology – Processors have well-defined intermediate steps throughout the design flow. Each of these steps are taught to engineers at the undergraduate level providing them with the knowledge to manually optimize the algorithm, compiler, assembler output, and processor architecture. Behavioural synthesis tools aim to reap the efficiency gains from not having a fixed architecture structure or instruction set. As a result it is difficult for designers to manually navigate the vastly different hardware implementations possible.

- 2. Libraries For a processor, compiled output can be packaged and shared very easily between software designers. This same idea has failed to gain traction in hardware design because of differing speed/area constraints and non-standardized interfaces. In contrast, software is decoupled from the hardware implementation allowing it to be designed primarily for speed. Moreover, libraries can preserve manual optimization of the compiled software.

- 3. **Debug Support** Processors provide single-step debug capability. While this can be emulated to some degree by hardware simulators, the parallel nature of hardware can make it confusing. In addition, hardware simulators can not precisely model the behaviour of the hardware itself because of external stimuli and hardware imperfections. Inevitably this means some bugs will manifest only in the hardware implementation where they are difficult to find and fix.

- 4. Intractable Complexities The complexities in deriving a high-quality hardware implementation of a system has made it a holy grail for many decades. Until high-quality behavioural synthesis exists, designers can instead utilize the customization opportunities in microprocessor systems. The knowledge gained through this research can also be used for improving behavioural synthesis tools.

- 5. **ANSI C Support** Overcoming the complexities in behavioural synthesis most often leads to limited support for the full ANSI C standard or radically different programming models. Some examples of these are summarized below, however the willingness of FPGA designers to adopt new C variants or programming models casts doubt on the future adoption of behavioural synthesis. In contrast a processor can easily support full ANSI C which provides a familiar programming interface.

One of the largest hurdles to supporting full ANSI C in behavioural synthesis is the global memory model used in high-level programming languages. While arithmetic operations can be literally converted to hardware circuits, a literal conversion of this memory model would result in many processing elements being sequenced to preserve memory

consistency but at the same time competing over the single memory. The CHiMPS [54] project aims to support traditional memory models by providing caches for many processing elements. Compiler analysis determines regions of memory safe for caching by analyzing dependencies in scientific computing applications which rarely have complex memory aliasing. Additionally, traditional memory models can be preserved with multi-threaded and/or multi-processor systems but programming these systems requires facing the difficult parallel programming problem. The implementation of these systems onto FPGAs leads to soft processor research which is summarized in Section 2.5.3 and Section 2.5.4.

Most behavioural synthesis compilers modify or restrict the memory model to facilitate better quality hardware implementations. The SA-C [17] compiler prohibits the use of pointers and recursion and forces all variables to be single-assignment. While these restrictions impose difficulties on the programmer, the resulting application code can be more easily converted to hardware. The streaming programming paradigm has also been researched as a means of programming FPGAs. For example the Streams-C [25] language allows a programmer to express their computation in a consume-compute-produce model. Data and task level parallelism can be extracted and used to build parallel hardware for faster execution. Similar work was done using the Brook stream language [53] and also using regular C file I/O streams for the PACT behavioural synthesis tool [48] [30].

#### 2.4.2 Extensible Processors

Behavioural synthesis aims to convert whole programs into hardware, but other approaches are premised on the common characteristic that a small computation is largely responsible for overall performance. The Warp [42] processing project derives on-the-fly hardware accelerators for a simplified FPGA fabric. This allows an application to be programmed in C and executed on a generic microprocessor which will automatically accelerate critical computations. The eMIPS [44] project converts blocks of binary MIPS instructions to hardware that can be dynamically configured onto an FPGA. The

instructions are then replaced with an invocation of the hardware accelerator. These dynamically extensible processors can be used to accelerate software and avoid custom hardware design similar to our own goals. However they are accompanied with significant overhead in synthesizing and configuring hardware accelerators and are hence critically dependent on correctly identifying computation to accelerate. This decision depends on how amenable the computation is to hardware acceleration and also depends on its overall contribution to system performance. As the system is improved and computation is more balanced across different kernels, it becomes increasingly difficult to select a computation which can amortize the dynamic configuration overheads.

#### 2.5 Soft Processors and Related Work

Soft processors are processors designed for a reprogrammable fabric such as an FPGA. The two key attributes of soft processors are (i) the ease with which they can be customized and subsequently implemented in hardware, and (ii) that they are designed to target the fixed resources available on a reprogrammable fabric. This distinguishes soft processors from hard processors which are extremely difficult to customize due to the high cost and long design and fabrication times of full-custom VLSI design. Also, soft processors are distinct from parameterized processor cores which are pre-designed synthesizable RTL implementations not necessarily targeting efficient FPGA implementation.

The Actel Cortex-M1 [2], Altera Nios II [5], Lattice Micro32 [39], and Xilinx Microb-laze [67] are widely used soft processors with scalar in-order single-issue architectures that are either unpipelined or have between 3 and 5 pipeline stages. While this is sufficient for system coordination tasks and least-critical computations, significant performance improvements are necessary for soft processors to replace the hardware designs of more important system components. Research in this direction is recent and ongoing, and summarized below.

#### 2.5.1 Soft Single-Issue In-Order Pipelines

The SPREE (Soft Processor Rapid Exploration Environment) system was developed to explore the architectural space of current soft processors in our previous research [69, 70, 71]. SPREE can automatically generate a Verilog hardware implementation of a processor from a higher-level description of the datapath and instruction set. The tool was used to explore the implementation and latencies of functional units as well as the depth and organization of pipeline stages creating a thorough space of soft processor design points that were competitive with the slower and mid-range Altera Nios II commercial soft processors. We found diminishing returns with deeper pipelining which required more advanced architectural features to avoid pipeline stalls. While this work succeeded in exploring the space and finding processor configurations superior to a mid-speed commercial soft processor, it failed to extend the space, specifically with faster soft processors. In this thesis, we continue to use SPREE by choosing the best overall generated design and manually adding vector extensions to the architecture and compiler infrastructure.

Numerous other works created parameterized scalar soft processors aimed at customization. The LEON [23] is a parameterized VHDL description of a SPARC processor targetted for both FPGAs and ASICS with several customization options including cache configuration and functional unit support. LEON is heavily focussed on system-level features fully supporting exceptions, virtual memory, and multiprocessors. No scalable performance options exist other than multiprocessing which requires parallelized code. Similarly the XiRisc [41] is a parameterized core written in VHDL supporting 2-way VLIW, 16/32-bit datapaths, and optional shifter, multiplier, divider, and multiply-accumulate units. While these options provide some performance improvements it cannot scale to compete with manual hardware design. Other VLIW processors are discussed below.

#### 2.5.2 Soft Multi-Issue Pipelines

The idea of using VLIW (Very Long Instruction Word) processors in which batches of independent instructions are submitted to the processor pipeline has been explored as

a way of increasing soft processor performance without the complexities of hardware scheduling. Saghir et. al. implemented a soft VLIW processor using a register file with 2 banks replicated 4 times to achieve the 4 read ports and 2 write ports necessary to sustain two instructions per cycle [57]. For an fir benchmark this configuration achieved up to 2.55x speedup with 3 data write ports and 2 address write ports over 1 data write port and 1 address write port. Bank conflicts and limits to instruction level parallelism limit the performance scaling possible on soft VLIW processors, moreover the increasing register file replication necessary would quickly become overwhelming. Jones et. al. implemented a 4-way VLIW processor by implementing the register file in logic instead of block RAMs [31]. This 4-way parallelism averaged only 29% speedup over single-issue, suggesting that the technique cannot easily scale performance.

A superscalar processor can issue multiple instructions concurrently, but unlike VLIW processors, a superscalar automatically identifies and schedules independent instructions in hardware. While this approach is popular in hard processors, there is presently no soft superscalar architectures in existence likely due to their complexity. Also, the large associative circuit structures and many-ported register file required to build a superscalar are not efficiently implementable in FPGAs. Carli designed an out-of-order single-issue soft MIPS processor that implements Tomasulo's algorithm and discusses the infeasibility of superscalar issue with respect to his architecture [12]. The soft MIPS was found to be up to twice as big as a Xilinx Microblaze and between 3x and 12x slower.

## 2.5.3 Soft Multi-Threaded Pipelines

A potentially promising method of scaling soft processor performance is to leverage multiple threads. Research into exploiting multiple threads in soft processors will only become more fruitful as advancements in parallel programming are made in the microprocessor industry. Nonetheless, auto-vectorization is a significantly simpler problem which exploits predominantly fine-grain data parallelism and is hence supported in many compilers including GCC.

The advanced architectural features needed to keep a pipeline fully utilized can be avoided by instead having multiple independent instruction streams (threads), which can also be used to hide system latencies. Fort et. al. showed that a multithreaded soft processor can save significant area while hiding memory latencies and performing as fast as a multiprocessor system when both use an uncached latent memory system [21]. Labrecque et. al. showed that multithreading can save logic by eliminating branch handling and data dependency hardware [37]. They also showed that with an off-chip DRAM memory system the amount of hardware threads, cache configuration, cache topology, and number of cores can be varied to achieve maximum throughput from the memory system [38]. Moussali [47] built a multi-threaded version of the Xilinx Microblaze and showed that 1.1x to 5x performance can be gained by hiding the latency caused by custom instructions and custom computation blocks.

The CUSTARD [15, 16] customizable threaded soft processor is an FPGA implementation of a parameterizable core supporting the following options: different number of hardware threads and types, custom instructions, branch delay slot, load delay slot, forwarding, and register file size. The primary purpose of the design was to be used with a tool for automatic custom instruction generation. However its uses as a parameterized soft processor is more applicable to our own work. While the available architectural axes are interesting the results show some overheads in the processor design: clock speed varied only between 30 and 50 MHz on the XC2V2000 FPGA (on which the Microblaze soft processor is clocked at 100 MHz), and overall performance is 6-61% worse than Microblaze. Also the single-threaded base processor consumed 1800 slices while the commercial Microblaze typically consumes less than 1000 slices on the same device. Nonetheless 4-way multi-threading can be added for only 28% more area but was shown to gain only 10% in performance.

#### 2.5.4 Soft Multiprocessors

Unnikrishnan et. al. created a tool for automating the parallelization of streaming code and making application-specific customizations to the targetted soft multiprocessor system [62]. The individual cores could be customized to their software eliminating unused hardware using our SPREE framework and achieving significant area savings. With 16 processors up to 5x increased performance can be achieved using this tool. Similarly, Plavec et. al. [53] developed a tool to generate a streaming architecture comprised of multiple processor cores from a streaming program. The Altera C2H behavioural synthesis tool is leveraged to convert processor nodes to custom hardware achieving further speed improvements. The generated and optimized streaming architecture can perform up to 8.9x faster than execution on a single soft processor, as well as 4.3x faster than using C2H on the entire benchmark kernel. Similar to our own work, these stream-based design flows can provide scalable soft processor performance if streaming languages are adopted by embedded system designers. An auto-vectorizing compiler or vectorized library could provide this scalability with minimal disruption to current design flows.

Ravindran et. al. built a soft multiprocessor system dedicated to IPv4 packet forwarding [55]. The 14-processor system was able to achieve a throughput of 1.8Gbps, which when normalized to area is 2.6x slower than the Intel IXP-2800 network processor. This case study show the potential of FPGA-based multiprocessors to compete with highly optimized and specialized commercial hard multiprocessors. Rigorous manual parallelization was required and the multiprocessor topology was customized, but customizing each individual core was not performed as the authors used standard Xilinx Microblaze cores. More aggressive customization would require extensive software and hardware labour, but can perhaps be automated in the future.

#### 2.5.5 Soft Vector Processors

Yu et. al. [75] first demonstrated the potential for vector processing as a simple-to-use and scalable accelerator for soft processors. In particular, through performance mod-

elling the authors show that (i) a vector processor can potentially accelerate data parallel benchmarks with performance scaling better than Altera's C2H behavioural synthesis tool (even after manual code restructuring to aid C2H), and (ii) how FPGA architectural features can be exploited to provide efficient support for some vector operations. For example, the multiply-accumulate blocks internally sum multiple partial products from narrow multiplier circuits to implement wider multiplication operations. This same accumulator circuitry is used by Yu to efficiently perform vector reductions which sum all vector elements and produce a single scalar value. Also the block RAMs can be used as small lane-local memories for efficiently implementing table lookups and scatter/gather operations.

The work of Yu et. al. was done in parallel with our own development of VESPA and its infrastructure, but it left many avenues unexplored. Its memory system consisted of only the fast on-chip block RAMs—latent memory systems were never explored. Without this and without real execution of benchmarks, the scalability of soft vector processors remains unproven. Also few customization opportunities in soft vector processors were examined beyond the number of lanes and the maximum vector length: the width of the lanes, multiplier, and memory were parameterized and were individually set for each benchmark. Finally more sophisticated vector pipelines features such as vector chaining were never considered. Beyond the work of Yu, in this thesis, we offer a full and verified hardware implementation of a soft vector processor called VESPA, connected to off-chip memory, with GNU assembler vector support, and evaluation on vectorized industry-standard benchmarks. This thesis more thoroughly explores the scalability, customizability, and architecture of soft vector processors. In addition, we explore the design space of VESPA configurations and show how competitive it can be versus manual hardware design in Chapter 8.

# Chapter 3

# Experimental Framework

Our goal of improving soft processors to be more competitive with hardware requires a measurement infrastructure for accurately and thoroughly evaluating enhancements to soft processors. In this chapter we describe the infrastructure used for executing, verifying, and evaluating soft processors. Specifically, we describe the benchmarks, compiler, CAD software, hardware platforms, measurement methodology, measurement error, and verification process.

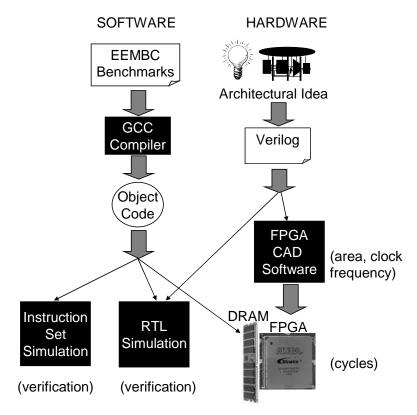

#### 3.1 Overview

We employ a real and complete measurement infrastructure which implements soft processors in hardware executing benchmarks on real FPGA devices. An overview of the infrastructure is illustrated in Figure 3.1. Benchmark software programs are compiled with standard compilers and simulated at the instruction-level to verify their correctness. Architectural ideas are augmented into a complete Verilog design of a soft processor and simulated at the register transfer level (RTL) using an RTL simulator. Once the correctness of the architecture is verified, the design is synthesized using FPGA computer-aided design (CAD) software which emit hardware characteristics such as the area and clock frequency of the design. The soft processor is then configured onto a real FPGA and executes each benchmark from off-chip DRAM—at the end of each execution the to-

Figure 3.1: Overview of measurement infrastructure.

tal number of cycles are reported. The individual components of the infrastructure are discussed in detail in the remainder of this chapter.

#### 3.2 Benchmarks

The benchmarks used in this study are predominantly from the industry-standard EEMBC (Embedded Microprocessor Benchmark Consortium) benchmark collection [18]. This EEMBC consortium is a non-profit corporation aiming to standardize embedded benchmarks and aid designers in selecting an appropriate embedded processor. The benchmarks are widely used in the embedded systems domain and since FPGAs are also used in the embedded domain, the EEMBC benchmarks are appropriate for evaluating soft processors. The benchmarks used in this study are selected from the Automotive 1.1, Office Automation 1.1, Telecom 1.1, Networking 2.0, and Digital Entertainment 1.0 suites. Our infrastructure is capable of compiling and executing all EEMBC benchmarks un-

EEMBC Input Output Num Benchmark Description Suite (Dataset) Source size (B) size (B) Loops EEMBC/VIRAM AUTCOR auto correlation Telecom (2) 1024 64 1 EEMBC/VIRAM CONVEN convolution encoder Telecom (1) 5221024 1 EEMBC/VIRAM Digital Ent. (5) 1628973 2171964 RGBCMYK rgb filter 1 RGBYIQ rgb filter EEMBC/VIRAM Digital Ent. (6) 11568001156800 1 EEMBC/VIRAM FBITAL bit allocation Telecom (2) 1536 512 2 VITERB viterbi encoder EEMBC/VIRAM Telecom (2) 688 44 5 IP\_CHECKSUM checksum EEMBC (kernel) Net (handmade 40960 40 1 IMGBLEND combine two images VIRAM (handmade) 153600 76800 1 FILT3X3 image filter VIRAM (handmade) 7680076800

Table 3.1: Vectorized benchmark applications

compromised and with the complete test harness allowing us to report official EEMBC scores.