#### **ECE1371 Advanced Analog Circuits**

#### **EXAMPLE DESIGN**

Trevor Caldwell trevor.caldwell@analog.com

# Highlights (i.e. What you will learn today)

- 1 MOD2 implementation

- 2 Switched-capacitor integrator Switched-C summer & DAC too

- 3 Dynamic-range scaling

- 4 kT/C noise

- 5 Verification strategy

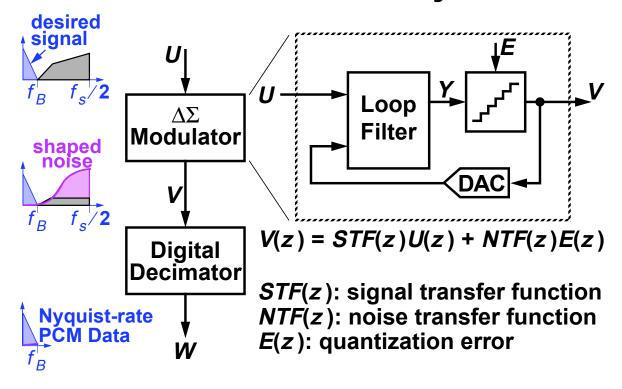

### Review: A $\Delta\Sigma$ ADC System

ECE1371 3

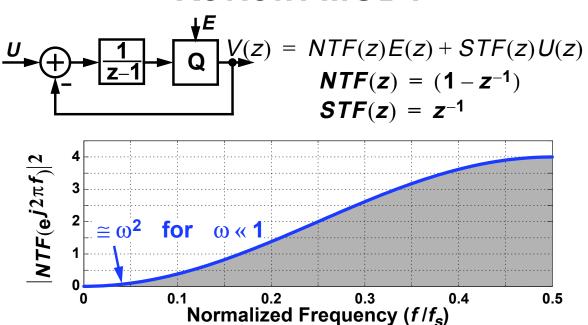

#### **Review: MOD1**

Poubling OSR improves SQNR by 9 dB Peak SQNR  $\approx$  dbp(9 · OSR<sup>3</sup>/(2 $\pi$ <sup>2</sup>)); dbp(x)  $\equiv$  10log<sub>10</sub>(x)

ECE1371

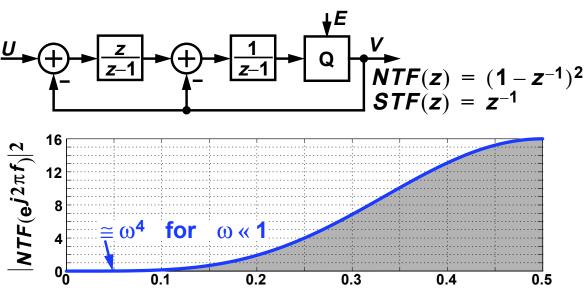

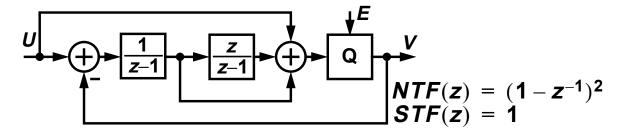

#### **Review: MOD2**

Normalized Frequency  $(f/f_s)$

Doubling OSR improves SQNR by 15 dB Peak SQNR ≈ dbp((15 · OSR<sup>5</sup>)/(4π<sup>4</sup>))

ECE1371 5

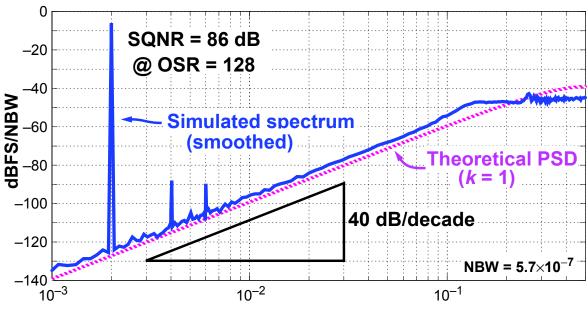

# Review: Simulated MOD2 PSD Input at 50% of FullScale

Normalized Frequency  $(f/f_s)$

#### **Review: Advantages of** $\Delta\Sigma$

ADC: Simplified Anti-Alias Filte

Since the input is oversampled, only very high frequencies alias to the passband.

A simple RC section often suffices

If a continuous-time loop filter is used, the anti-alia filter can often be eliminated alto ether.

- DAC: Simplified Reconstruction Filte

The nearby images present in Nyquist-rate reconstruction can be removed digitally.

- + Inherent Linearity

Simple structures can yield very high SNR.

- + Robust Implementation

$\Delta\Sigma$  tolerates sizable component errors.

ECE1371 7

### Let's Try Making One!

Clock at f<sub>s</sub> = 1 MHz.

Assume BW = 1 kHz.

$$\Rightarrow OSR = f_s/(\mathbf{2} \cdot \mathbf{BW}) = \mathbf{500} \approx \mathbf{29}$$

- MOD1: SQNR ≈ 9 dB/octave 9 octaves = 81 dB

- MOD2: SQNR ≈ 15 dB/octave 9 octaves =135 dB Actually more like 120 dB.

- SQNR of MOD1 is not bad, but SQNR of MOD2 is awesome!

In addition to MOD2's SQNR advantage, MOD2 is usually preferred over MOD1 because MOD2's quantization noise is more well-behaved.

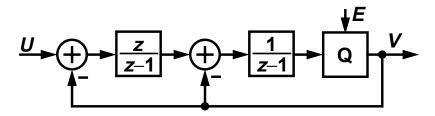

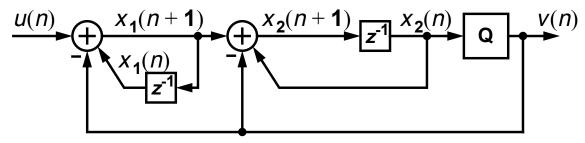

#### What Do We Need?

- 1 Summation blocks

- 2 Delaying and non-delaying discrete-time integrators

- 3 Quantizer (1-bit)

- 4 Feedback DACs (1-bit)

- 5 Decimation filter (not shown)

Digital and therefore "easy."

ECE1371 9

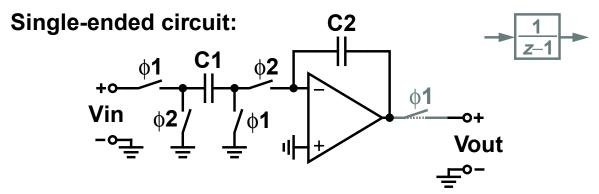

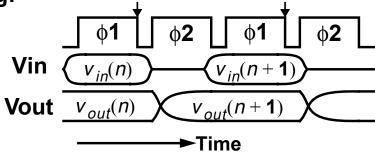

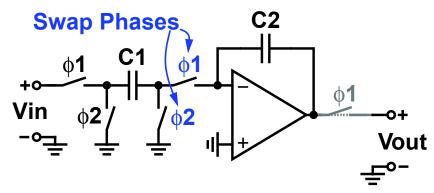

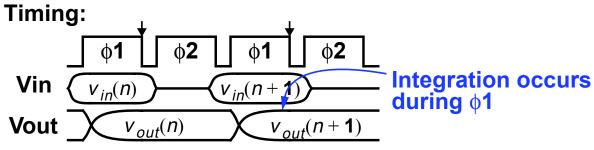

## **Switched-Capacitor Integrator**

**Timing:**

ECE1371 11

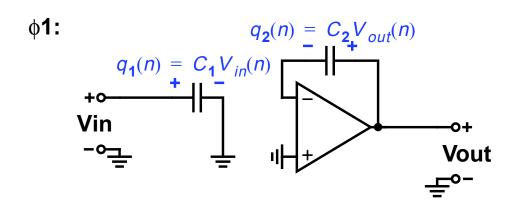

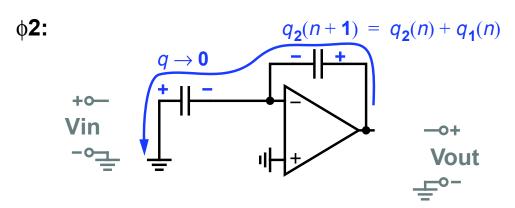

$$q_2(n+1) = q_2(n) + q_1(n)$$

$$zQ_2(z) = Q_2(z) + Q_1(z)$$

$$Q_2(z) = \frac{Q_1(z)}{z-1}$$

This circuit integrates charge

• Since

$$Q_1 = C_1 V_{in}$$

and  $Q_2 = C_2 V_{out}$

$$\frac{V_{out}(z)}{V_{in}(z)} = \frac{C_1 / C_2}{z - 1}$$

Note that the voltage gain is controlled by a ratio of capacitors

With careful layout, 0.1% accuracy is possible.

12

ECE1371

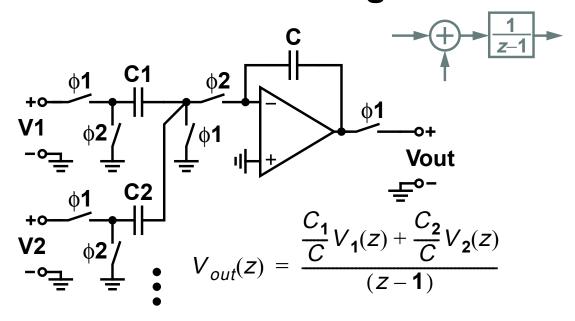

#### **Summation + Integration**

⇒ Adding an extra input branch accomplishes addition, with weighting

ECE1371 13

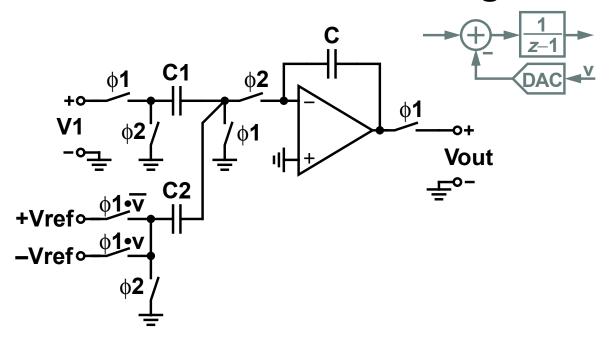

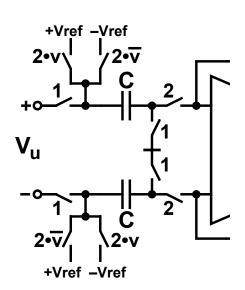

## 1b DAC + Summation + Integration

#### **Differential Integrator**

ECE1371 15

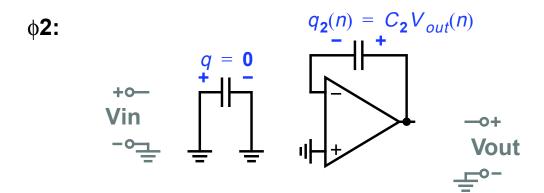

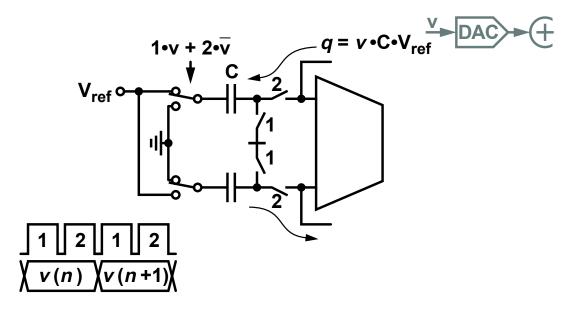

#### **Non-Delaying Integrator**

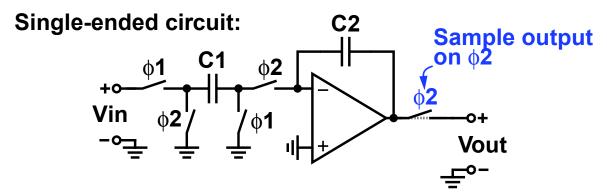

#### Single-ended circuit:

ECE1371 17

$$q_{2}(n+1) = q_{2}(n) - q_{1}(n+1)$$

$$zQ_{2}(z) = Q_{2}(z) - zQ_{1}(z)$$

$$\frac{Q_{2}(z)}{Q_{1}(z)} = -\frac{z}{z-1}$$

$$\frac{V_{out}(z)}{V_{in}(z)} = -\left(\frac{C_{1}}{C_{2}}\right)\frac{z}{z-1}$$

Delay-free integrator (inverting)

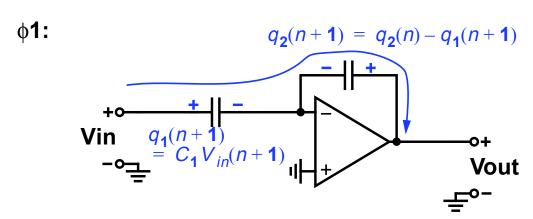

### "Half-Delay" Integrator

**Timing:**

ECE1371 19

### **Half-Delay Integrator**

- Output is sampled on a different phase than the input

- Some use the notation  $H(z) = \frac{z^{-1/2}}{z-1}$  to denote the shift in sampling time

I consider this an abuse of notation.

- An alternative method is to declare that the border between time n and n+1 occurs at the end of a specific phase, say \$\phi2\$

- $\Rightarrow$  A circuit which samples on  $\phi$ 1 and updates on  $\phi$ 2 is non-delaying, i.e. H(z) = z/(z-1), whereas a circuit which samples on  $\phi$ 2 and updates on  $\phi$ 1 is delaying, i.e. H(z) = 1/(z-1).

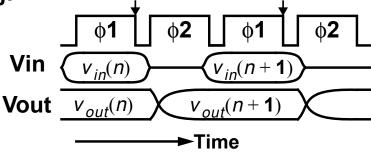

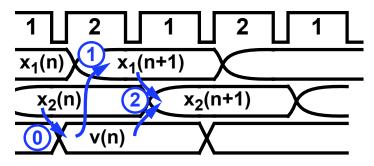

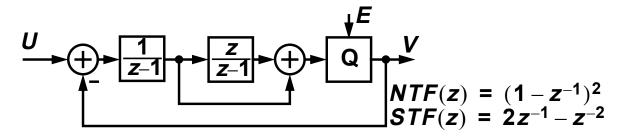

## Timing in a $\Delta\Sigma$ ADC

- The safest way to deal with timing is to construct a timing diagram and verify that the circuit implements the desired difference equations

- E.g. MOD2:

#### **Difference Equations:**

$$V(n) = Q(x_2(n)) \tag{0}$$

$$x_1(n+1) = x_1(n) - v(n) + u(n)$$

(1)

$$x_2(n+1) = x_2(n) - v(n) + x_1(n+1)$$

(2)

ECE1371 21

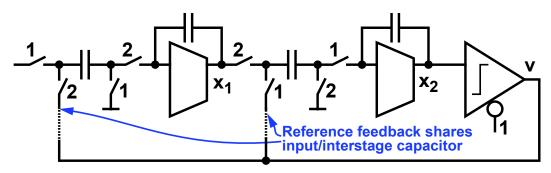

### **Switched-Capacitor Realization**

**Timing**

Timing looks OK!

### Signal Swing

- So far, we have not paid any attention to how much swing the op amps can support, or to the magnitudes of u, V<sub>ref</sub>, x<sub>1</sub> and x<sub>2</sub>

- For simplicity, assume:

the full-scale range of u is ±1 V,

the op-amp swing is also ±1 V and

V<sub>ref</sub> = 1 V

- We still need to know the ranges of  $x_1$  and  $x_2$  in order to accomplish *dynamic-range scaling*

ECE1371 23

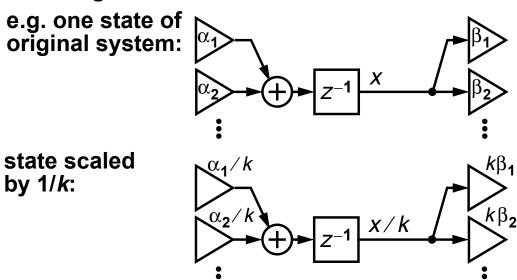

### **Dynamic-Range Scaling**

In a linear system with known state bounds, the states can be scaled to occupy any desired range

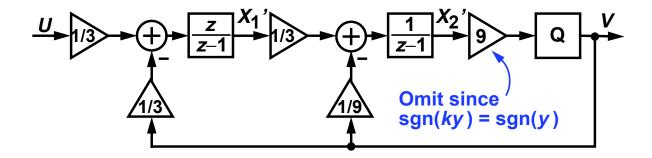

#### Scaled MOD2

• Take  $||x_1||_{\infty} = 3$  and  $||x_2||_{\infty} = 9$

The fi st integrator should not saturate.

The second integrator will not saturate for dc inputs up to -3 dBFS and possibly as high as -1 dBFS.

Our scaled version of MOD2 is thus

ECE1371 25

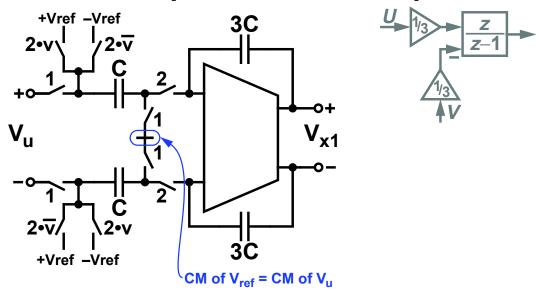

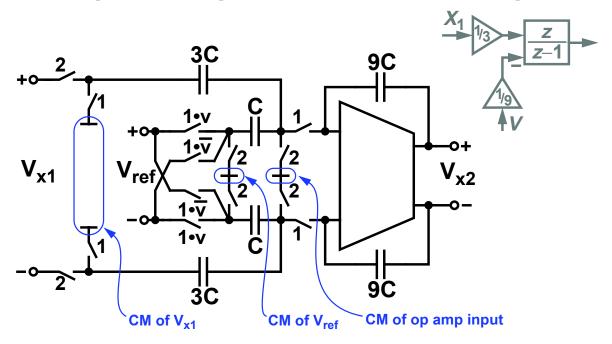

# First Integrator (INT1) Shared Input/Reference Caps

How do we determine C?

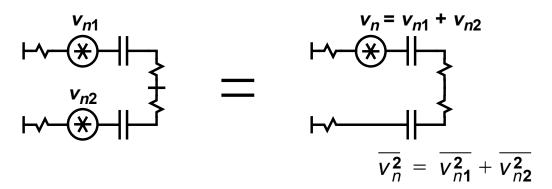

#### **Differential Noise**

- Twice as many switched caps

⇒ twice as much noise power

- The input-referred noise power in our differential integrator is

$$\overline{v_n^2} = 4kT/C_1$$

ECE1371 27

# INT1 Absolute Capacitor Sizes For SNR = 100 dB @ -3-dBFS input

The signal power is

$$\overline{V_s^2} = \frac{1}{2} \cdot \frac{(1 \text{ V})^2}{2} = 0.25 \text{ V}^2$$

-3 dBFS  $\frac{A^2}{2}$

- Therefore we want  $\overline{v_{n, \text{ in-band}}^2} = 0.25 \times 10^{-10} \text{ V}^2$

- Since  $\overline{v_{n, \text{ in-band}}^2} = \overline{v_n^2} / OSR$

$$C_1 = \frac{4kT}{\overline{V_n^2}} = 1.33 \text{ pF}$$

If we want 10 dB more SNR, we need 10x caps

ECE1371

# Second Integrator (INT2) Separate Input and Feedback Caps

ECE1371 29

### **INT2 Absolute Capacitor Sizes**

In-band noise of second integrator is greatly attenuated

- ⇒ Capacitor sizes not dictated by thermal noise

- Charge injection errors and desired ratio accuracy set absolute size

A reasonable size for a small cap is currently ~10 fF.

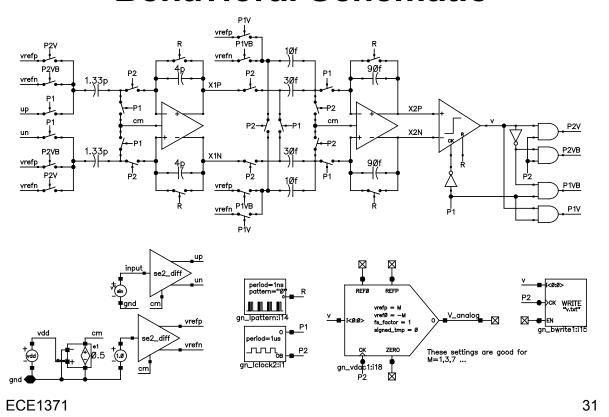

#### **Behavioral Schematic**

#### **Verification**

#### **Open-loop verification**

- 1 Loop filter

- 2 Comparator

Since MOD2 is a 1-bit system, all that can go wrong is the polarity and the timing. Usually the timing is checked by (1), so this verification step is not needed.

#### **Closed-loop verification**

- 3 Swing of internal states

- 4 Spectrum: SQNR, STF gain

- 5 Sensitivity, start-up, overload recovery, ...

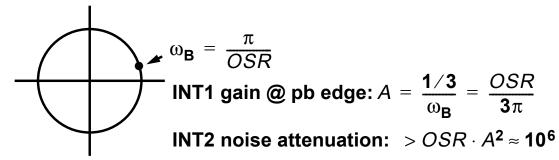

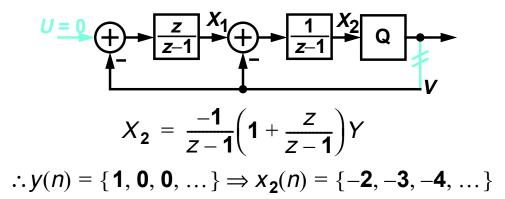

### **Loop-Filter Check— Theory**

Open the feedback loop, set u = 0 and drive an impulse through the feedback path

• If x<sub>2</sub> is as predicted then the loop filter is correct At least for the feedback signal, which implies that the NTF will be as designed.

ECE1371 33

# **Loop Filter Check— Practice**\*

<sup>\*. &</sup>quot;In theory there is no difference between theory and practice. But in practice there is."

#### **Hey! You Cheated!**

An impulse is {1,0,0,...}, but a binary DAC can only output ±1, i.e. it cannot produce a 0

Q: So how can we determine the impulse response of the loop filter through simulation?

A: Do two simulations: one with  $v = \{-1,-1,-1,...\}$  and one with  $v = \{+1,-1,-1,...\}$ . Then take the difference.

According to superposition, the result is the response to  $v = \{2,0,0,...\}$ , so divide by 2.

To keep the integrator states from growing too quickly, you could also use  $v = \{-1,-1,+1,-1,...\}$  and then  $v = \{+1,-1,+1,-1,...\}$ .

ECE1371 35

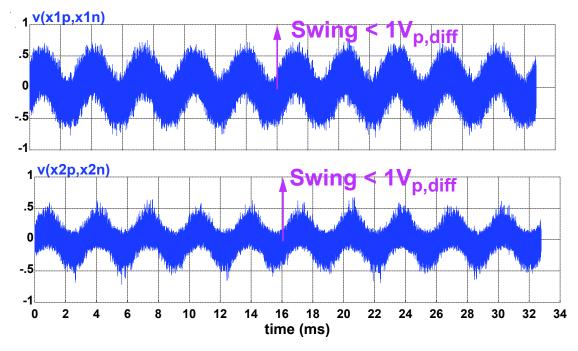

# Simulated State Swings –3-dBFS ~300-Hz sine wave

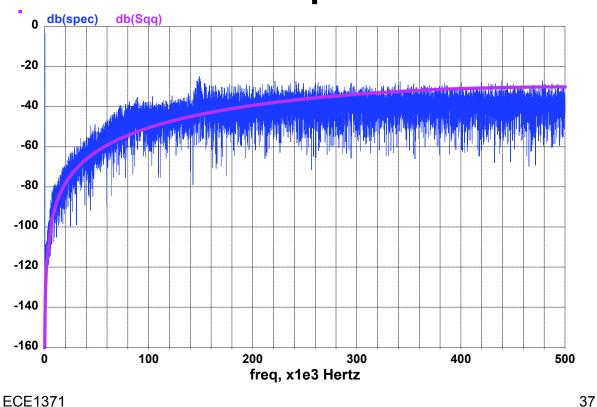

### **Unclear Spectrum**

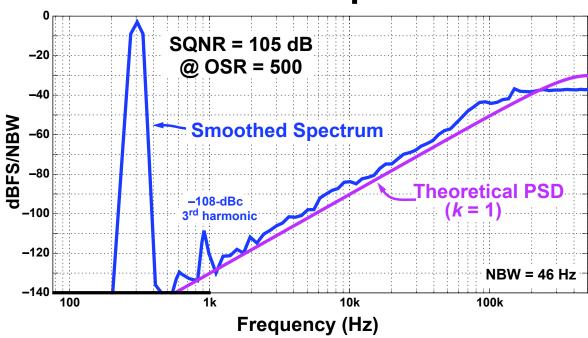

## **Professional Spectrum**

• SQNR dominated by -109-dBFS 3<sup>rd</sup> harmonic

### **Implementation Summary**

- 1 Choose a viable SC topology and manually verify timing

- 2 Do dynamic-range scaling

You now have a set of capacitor ratios.

Verify operation: loop filter, timing, swing, spectrum.

- 3 Determine absolute capacitor sizes Verify noise.

- 4 Determine op-amp specs and construct a transistor-level schematic Verify everything.

ECE1371 39

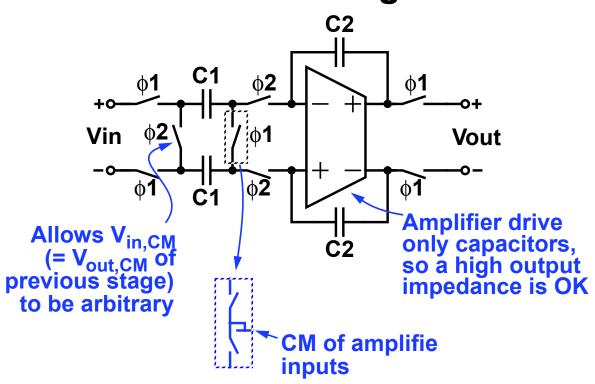

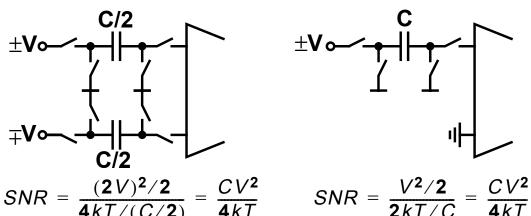

## Differential vs. Single-Ended

Differential is more complicated and has more caps and more noise ⇒ single-ended is better?

Same capacitor area ⇒ same SNR

Differential is generally preferred due to rejection of even-order distortion and common-mode noise/interference.

ECE1371

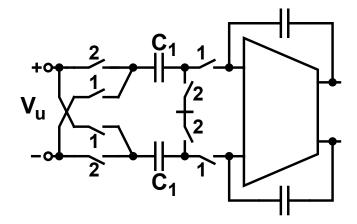

#### **Double-Sampled Input**

- Doubles the effective input signal

- Allows  $C_1$  to be 1/4 the size for the same SNR

- Doubles the sampling rate of the signal, thereby easing AAF further

ECE1371 41

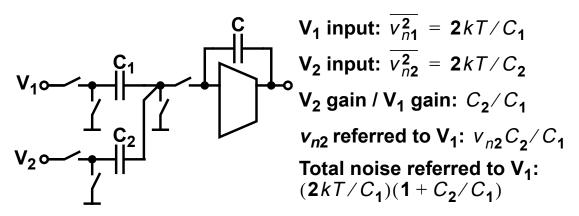

### Shared vs. Separate Input Caps

Separate caps ⇒ More noise:

But using separate caps allows input CM to be different from reference CM, and so is often preferred in a general-purpose ADC

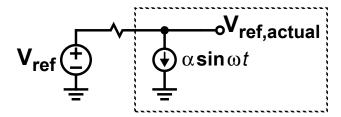

### Signal-Dependent Ref. Loading

Another practical concern is the current draw from the reference

ADC Output

$$\propto \frac{V_{in}}{V_{ref}(\mathbf{1} - \epsilon \sin \omega t)} \approx \frac{V_{in}}{V_{ref}}(\mathbf{1} + \epsilon \sin \omega t)$$

If the reference current is signal-related, harmonic distortion can result

ECE1371 43

### Shared Caps and Ref. Loading

$$q = \begin{cases} C(V_{ref} - V_u/2), v = +1 \\ C(V_{ref} + V_u/2), v = -1 \end{cases}$$

#### **Thus**

$$\bar{I} = \frac{C}{T}(V_{ref} - v \cdot V_u/2)$$

- If  $u = A\sin\omega_u t$ , then v = u + error also contains a component at  $\omega_u$  and thus I contains a component at  $\omega = 2\omega_u$ .

- Since ADC Output  $\propto V_{in}(1 + \epsilon \sin \omega t)$ , the signal-dependent reference current in our circuit can produce  $3^{rd}$ -harmonic distortion

Also, the load presented to the driving circuit is dependent on v and this noisy load can cause trouble.

With separate caps, the reference current is signal-independent

Yet another reason for using separate caps.

ECE1371 45

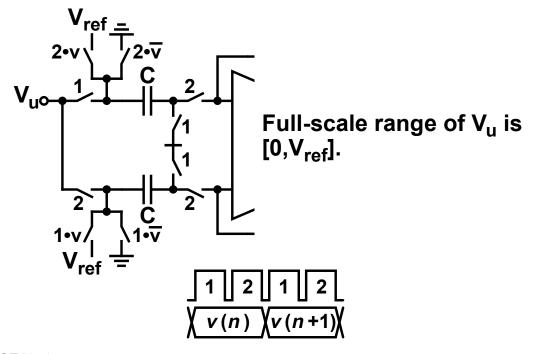

#### **Unipolar Reference**

• Be careful of the timing of *v* relative to the integration phase!

# Single-Ended Input Shared Caps

ECE1371 47

### Topological Variant– Feed-Forward

- + Output of first integrator has no DC component Dynamic range requirements of this integrator are relaxed.

- Although  $|STF| \approx 1$  near  $\omega = 0$ , |STF| = 3 for  $\omega = \pi$  Instability is more likely.

## Topological Variant— Feed-Forward with Extra Feed-In

- + No DC component in either integrator's output Reduced dynamic range requirements in both integrators, esp. for multi-bit modulators.

- + Perfectly flat STF

No increased risk of instability.

- Timing is tricky

ECE1371 49

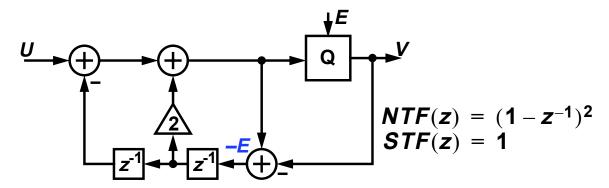

### Topological Variant– Error Feedback

- + Simple

- Very sensitive to gain errors

Only suitable for digital implementations.

# Is MOD2 The Only 2<sup>nd</sup>-Order Modulator?

Except for the filtering p ovided by the STF, any modulator with the same NTF as MOD2 has the same input-output behavior as MOD2

SQNR curve is the same.

Tonality of the quantization noise is unchanged.

Internal states, sensitivity, thermal noise etc. can differ from realization to realization

BUT, in terms of input-output behavior,

A 2<sup>nd</sup>-order modulator is truly different only if it possesses a truly different (2<sup>nd</sup>-order) NTF

ECE1371 51

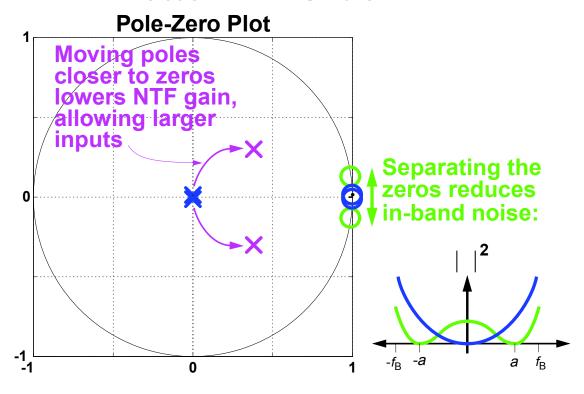

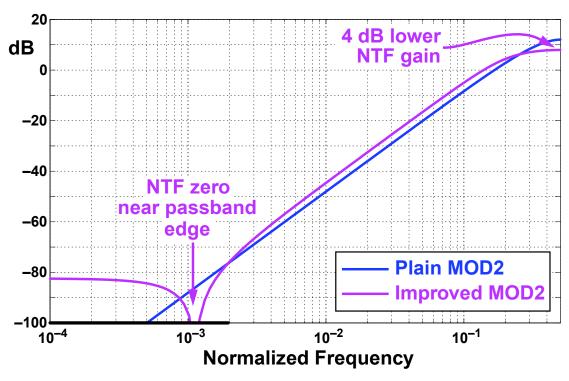

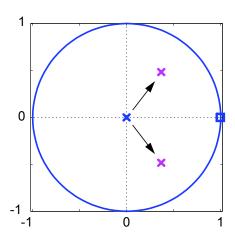

## A Better 2<sup>nd</sup>-Order NTF

## **NTF** Comparison

ECE1371 53

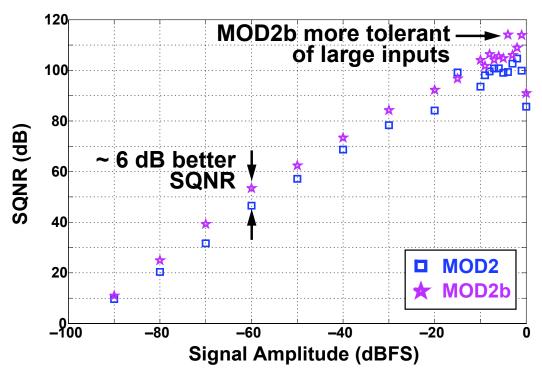

## **SNR vs. Amp Comparison**

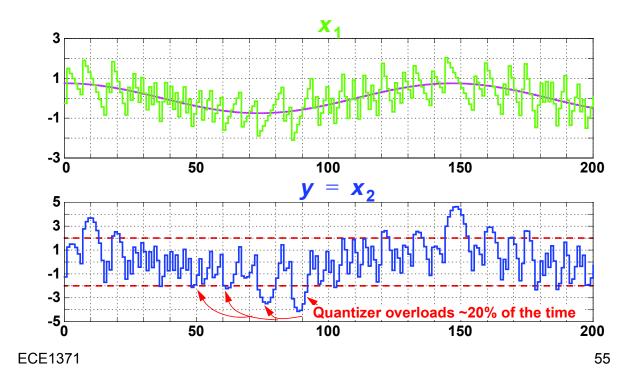

# MOD2 Internal Waveforms Input @ 75% of FS

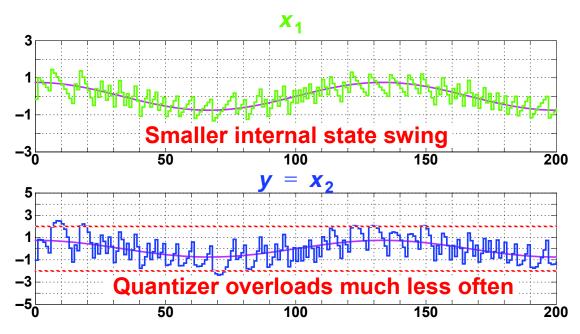

# MOD2b Internal Waveforms Input @ 75% of FS

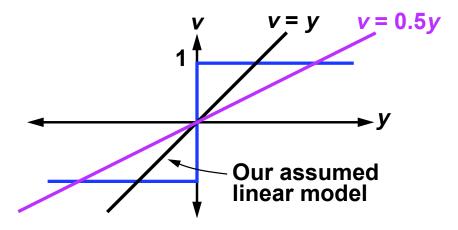

### Gain of a Binary Quantizer

- The effective gain of a binary quantizer is not known a priori

- The gain (k) depends on the statistics of the quantizer's input

Halving the signal doubles the gain.

ECE1371 57

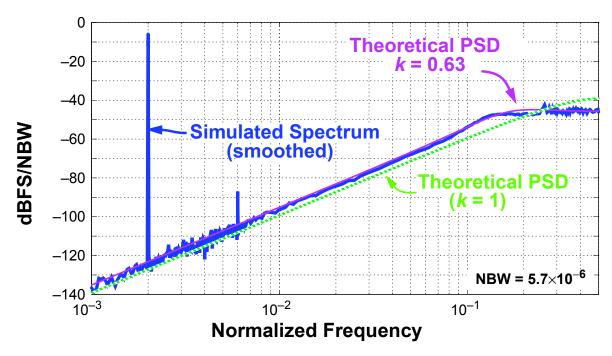

#### **Gain of the Quantizer in MOD2**

The effective gain of a binary quantizer can be computed from the simulation data using

$$k = \frac{E[|y|]}{E[v^2]}$$

[S&T Eq. 2.5]

- For the simulation of 2-14, k = 0.63

- $k \neq 1$  alters the NTF:

$$NTF_k(z) = \frac{NTF_1(z)}{k + (1 - k)NTF_1(z)}$$

#### **Revised PSD Prediction**

Agreement is now excellent

ECE1371 59

#### Variable Quantizer Gain

- When the input is small (below -12 dBFS), the effective gain of MOD2's quantizer is k = 0.75

- MOD2's "small-signal NTF" is thus  $NTF(z) = \frac{(z-1)^2}{z^2 0.5z + 0.25}$

- This NTF has 2.5 dB less quantization noise suppression than the  $(1-z^{-1})^2$  NTF derived from the assumption that k=1

Thus the SQNR should be about 2.5 dB lower than  $\times$ .

As the input signal increases, k decreases and the suppression of quantization noise degrades

SQNR increases less quickly than the signal power. Eventually the SQNR saturates and then decreases as the signal power reaches full-scale.