## **University of Toronto**

### **Term Test 1**

Date - Feb 10, 2010

Duration: 1.5 hrs

ECE334 — Digital Electronics Lecturer - D. Johns

# ANSWER QUESTIONS ON THESE SHEETS USING BACKS IF NECESSARY

- 1. Equation sheet is on last page of test.

- 2. Only tests written in pen will be considered for a re-mark.

- 3. Calculator type unrestricted

- 4. Grading indicated by []. Attempt all questions since a blank answer will certainly get 0.

|                      | Question                   | Mark |

|----------------------|----------------------------|------|

|                      | 1                          |      |

|                      | 2                          |      |

|                      | 3                          |      |

|                      | 4                          |      |

| Last Name: SOLUTIONS | 5                          |      |

|                      | Total                      |      |

| First Name:          |                            |      |

| Student #:           | $(\max \text{grade} = 29)$ |      |

- [5] Question 1: Answer the True [T] or False [F] questions below by circling the correct answer. Each correct answer is worth 0.5 marks.

- T F In a rising clock edge register, when the clock is high, the first (input) latch is in track mode while the second (output) latch is in hold mode.

- T For a CMOS gate, the pull-up network is always the dual of the pull-down network.

- T  $\stackrel{\frown}{\text{F}}$  Given a chain of identical CMOS inverters, the gate delay will DECREASE when  $C_{\text{ox}}$  is increased by 10%.

- T Given a chain of identical CMOS inverters, the gate delay will DECREASE when  $|V_{tn}|$  and  $|V_{tn}|$  are both increased by 10%.

- T (F) Given a chain of identical CMOS inverters, the gate delay will DECREASE when the widths of all transistors are increased by 10%

- For a CMOS gate, a large unwanted current will occur if both the pull-up network and pull-down network are on at the same time.

- T For pass transistor logic and where "1" equals Vdd and "0" equals ground, an NMOS transistor passes a "1" well but does not pass "0" well.

- T F Restoring logic uses negative gain circuits where the output saturates towards the logic levels.

- T (F) Moore's "law" states that "computer performance will double every 18 months".

- T (F) For detailed estimation of drain-bulk junction capacitance, the gate-source voltage is required.

Last Name: \_\_\_\_\_

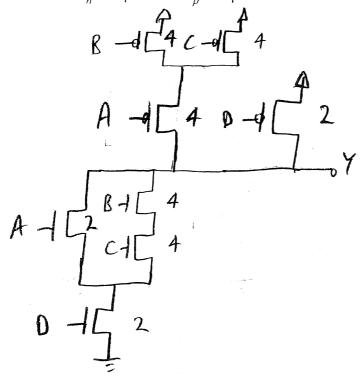

[6] Question 2: Show a CMOS gate that realizes the function  $Y = \overline{(A+BC)D}$ . Also, determine transistor sizes so that the worst case pull-down and pull-up is equivalent to a single inverter with  $W_n = 1 \, \mu \text{m}$  and  $W_p = 2 \, \mu \text{m}$ . All transistor lengths are  $0.25 \, \mu \text{m}$ .

W SHOWN BESIDE TRANSISTORS

SOLUTION IS NOT UNIQUE

### [6] Question 3:

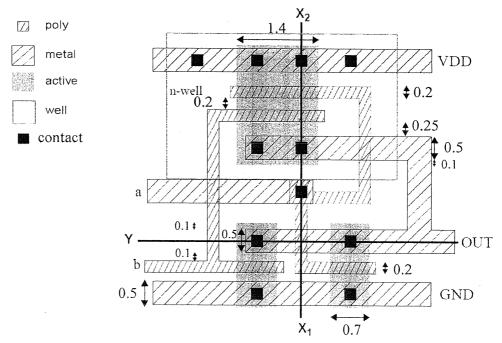

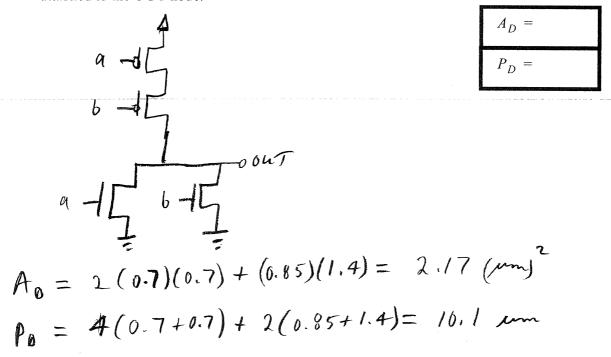

a) For the layout shown above, draw the schematic. Show the sizes of the NMOS and PMOS transistors. Also show the TOTAL drain area,  $A_D$ , and TOTAL drain perimeter,  $P_D$ , attached to the OUT node.

| Last Name: |  |

|------------|--|

|------------|--|

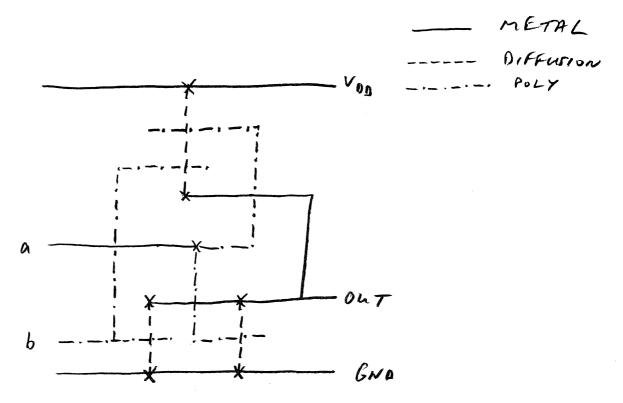

b) For the layout shown above, draw a stick diagram. Show your stick diagram legend that indicates which lines are poly, metal and active. Use "X" for contacts.

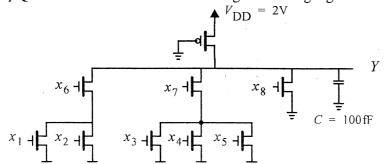

[6] Question 4: Consider the following ratioed logic gate

$$\mu_n C_{\text{ox}} = 200 \,\mu\text{A/V}^2$$

$$V_{tn} = 0.3 \,\text{V}$$

$$W_p = 0.5 \,\mu\text{m}$$

$$L_p = 1 \,\mu\text{m}$$

$$\text{all } W_n = 1 \,\mu\text{m}$$

$$\text{all } L_n = 0.25 \,\mu\text{m}$$

a) Using the RC delay estimate, find  $t_{\rm df\_min}$  and  $t_{\rm df\_max}$  (ignore effect of PMOS transistor).

$$td_{f-MAX} = 1 \times 1 \times 6, \ \times 2 \times 6, \ \times 3 \times 7, \ \times 5 \times 7$$

$$(W)_{ER} = (0.5) = ) RERN = \frac{2.5}{M_{o}C_{ox}(\%)(V_{00}-V_{EN})}$$

$$= 2$$

$$= 3.(8 \text{ K})$$

$$td_{f-MAX} = 1.2 REANC = 441 \text{ As}$$

$$td_{f-MAX} = ) \text{ ALC HIBST}$$

$$W_{f}$$

154-164 => 15/3-15/4 => +5/9-15/4 => +5/9-67 +5/8 +5/2 = +5/4 => +5/9-15/4 => +5/9-67 -15/8 +5/2 = +5/4 => +5/9-67 = 91.2 ps

b) If the effect of the PMOS transistor is taken into account, would the delay estimate for both  $t_{\rm df\ min}$  and  $t_{\rm df\ max}$  decrease, increase or stay the same? Explain.

IT WOULD DECREASE DELAY TIMES AS IT IS EQUIVALENT TO A RESISTANCE IN PARALLEL TO REAN OF NMOS TRANSISTORS.

- [6] Question 5: A CMOS process has a supply voltage of 2V and an NMOS threshold voltage of 0.3V. A circuit designer is evaluating a proposal to reduce  $V_{in}$  by 100 mV to reduce delay times for falling edges.

- a) By what factor would the delay for falling edges decrease?

$$\frac{2-0.2}{2-0.3} = 1.059$$

OR  $5.990$  DECREASE

b) By what factor would the subthreshold leakage current increase at room temperature at  $V_{\rm GS}=0$ ? Assume n=1.4.

$$\frac{e^{\frac{-0.3}{4(14)(26mv)}}}{e^{\frac{-0.3}{(14)(26mv)}}} = e^{\frac{-0.3}{(14)(26mv)}} = 15.6$$

c) Assuming the threshold voltage remains fixed at  $V_{tn} = 0.3 \,\mathrm{V}$ , does the delay for falling edges decrease or increase as the temperature is lowered? Explain your reasoning.

DELAY DECREASES SINCE MOBILITY INCREASES AS

| Last Name: |  |

|------------|--|

|            |  |

(blank sheet for scratch calculations)

#### **ECE334**

## **Digital Electronics**

### **Equation Sheet**

```

\begin{array}{l} \textbf{Constants:} \ k = 1.38 \times 10^{-23} \ \text{JK}^{-1} \ ; q = 1.602 \times 10^{-19} \ \text{C} \ ; V_T = kT/q \approx 26 \, \text{mV} \ \text{at } 300 \ \text{°K} \ ; \\ \epsilon_0 = 8.854 \times 10^{-12} \ \text{F/m} \ ; \ k_{\text{ox}} = 3.9 \ ; \ \textbf{caps:} \ C_{\text{ox}} = (k_{\text{ox}} \epsilon_0)/t_{\text{ox}} \ ; \ C_j = C_{j0}/(1 + V_R/\phi_0)^{M_j} \ ; \\ \textbf{NMOS:} \ \beta_n = \mu_n C_{\text{ox}} (W/L) \ ; \ V_{tn} > 0 \ ; V_{\text{DS}} \geq 0 \ ; (\text{triode}) \ I_D = \beta_n ((V_{\text{GS}} - V_{tn}) V_{\text{DS}} - (V_{\text{DS}}^2/2)) \ ; (\text{active}) \ I_D = 0.5 \beta_n (V_{\text{GS}} - V_{tn})^2 \ ; \\ \text{(triode)} \ V_{\text{DS}} \leq (V_{\text{GS}} - V_{tn}) \ ; (\text{active}) \ V_{\text{DS}} \geq (V_{\text{GS}} - V_{tn}) \ ; \ V_{tn} = V_{tn0} + \gamma (\sqrt{V_{\text{SB}}} + \phi_s - \sqrt{\phi_s}) \ ; \\ \text{(subthreshold)} \ I_D = I_{D0} e^{((V_{\text{GS}} - V_{tn})/(nV_T))} (1 - e^{-V_{\text{DS}}/V_T}) \ ; \\ \textbf{PMOS:} \ \beta_p = \mu_p C_{\text{ox}} (W/L) \ ; \ V_{tp} < 0 \ ; V_{\text{DS}} \leq 0 \ ; (\text{triode}) \ I_D = \beta_p ((V_{\text{GS}} - V_{tp}) V_{\text{DS}} - (V_{\text{DS}}^2/2)) \ ; (\text{active}) \ I_D = 0.5 \beta_p (V_{\text{GS}} - V_{tp})^2 \ ; \\ \text{(triode)} \ V_{\text{DS}} \geq (V_{\text{GS}} - V_{tp}) \ ; (\text{active}) \ V_{\text{DS}} \leq (V_{\text{GS}} - V_{tp}) \ ; \\ \textbf{Simple cap model:} \ C_g = C_{\text{ox}} WL \ ; \ \text{if} \ L_{\text{min}} \ ; \ C_g = C_{gu} W \ ; \ C_d = C_s = C_{du} W \ ; \\ \textbf{CMOS inverter:} \ V_{\text{TH}} = (V_{\text{DD}} + V_{tp} + V_{tn}r)/(1 + r) \ ; \ r = \sqrt{(\mu_n (W/L)_n)/(\mu_p (W/L)_p)} \ ; \\ \textbf{RC delay est:} \ t_{dr} = t_{df} = 1.2\tau \ ; \ \tau = R_{\text{eq}} C \ ; \ R_{\text{eqn}} = 2.5/(\mu_n C_{\text{ox}} (W/L)_n (V_{\text{DD}} - V_{\text{In}})) \ ; \ R_{\text{eqp}} = 2.5/(\mu_p C_{\text{ox}} (W/L)_p (V_{\text{DD}} + V_{tp})) \ ; \end{cases}

```