### **University of Toronto**

#### **Term Test 1**

Date - Feb 9, 2011

Duration: 1.5 hrs

ECE334 — Digital Electronics Lecturer - D. Johns

## ANSWER QUESTIONS ON THESE SHEETS USING BACKS IF NECESSARY

- 1. Equation sheet is on last page of test.

- 2. Only tests written in pen will be considered for a re-mark.

- 3. Calculator type unrestricted

- 4. Grading indicated by []. Attempt all questions since a blank answer will certainly get 0.

|                       | 3                |   |  |

|-----------------------|------------------|---|--|

|                       | 4                |   |  |

| Last Name: SO LUTIONS | 5                |   |  |

| -                     | Total            |   |  |

| First Name:           | ,                | - |  |

| CALL Devel He         | (max grade = 29) |   |  |

| Student #:            |                  |   |  |

Question

Mark

Last Name: \_\_\_\_\_

#### [5] Question 1: Each correct answer is worth 0.5 marks.

For the questions below, circle one of True [T] or False [F].

- The capacitance of a reverse biased junction increases as the reverse bias voltage is increased.

- T F The output of a CMOS tri-state inverter is one of  $V_{\rm DD}$ ,  $V_{\rm DD}/2$ , or 0.

T F  $C_{\rm ox}$  is inversely proportional to the gate oxide thickness.

- T F Channel length modulation is generally important in analog circuits but not usually important in digital circuits.

For the questions below, consider the gate delay for a chain of indentical CMOS inverters and only one parameter is changed. Circle one of "increase", "unchanged" or "decrease" that corresponds to the new gate delay

| increase | (unchanged) | decrease | $C_{\rm ox}$ is increased by 10%                                          |

|----------|-------------|----------|---------------------------------------------------------------------------|

| increase | unchanged   | decrease | $V_{ m DD}$ is increased by 10%                                           |

| increase | unchanged   | decrease | The widths of all transistors are increased by 10%                        |

| increase | unchanged   | decrease | $\left V_{tn}\right $ and $\left V_{tp}\right $ are both increased by 10% |

| increase | unchanged   | decrease | Temperature is increased by 10%                                           |

| increase | unchanged   | decrease | Electron and hole mobility are both increased by 109                      |

Last Name:

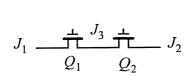

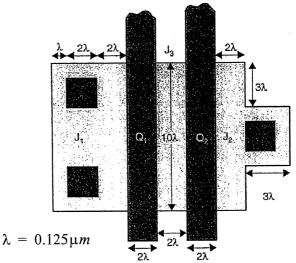

[6] Question 2: Consider the layout of 2 nmos transistors as shown below and use CMOS parameters on the equation sheet (last page).

a) Find the input capacitance for the gate of a single transistor (ignore overlap capacitance).

$$C_g = C_{OX} WL = (6)(10\lambda)(2\lambda) = (6)(1.25)(0.25) = 1.875 \text{ FF}$$

b) Find the overlap capacitance for the gate of  $Q_2$  to junction  $J_2$

$$C_{gdor} = C_{o} W = (0.3)(1.25) = 0.375 + F$$

c) Find the drain-bulk capacitance at  $J_3$  (using both area and sidewall capacitance).

c) Find the drain-bulk capacitance at

$$J_3$$

(using both area and sidewall capacitance).

$$CdB = C_j A_0 + C_{jSW} P_0 = (2)(1.25)(0.25) + (0.3)(2)(1.25+0.25)$$

$$= 0.625 + 0.9 = 1.525 + 6$$

d) Find the drain-bulk capacitance at  $J_2$  (using both area and sidewall capacitance).

$$CdB = C_{1}A_{0} + C_{1}S_{0}P_{0}$$

$$C_{1}A_{0} = (2)[(1.25)(0.25) + (0.375)(0.5)] = 1 + F$$

$$C_{1}S_{0}P_{0} = (0.3)[10\lambda + 4\lambda + 6\lambda + 4\lambda + 4\lambda] = (0.3)(30\lambda)$$

$$= (0.3)[3.75] = 1.125 + F$$

$$CdB = 1 + 1.125 = 2.125 + F$$

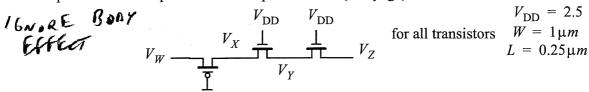

[6] Question 3: Consider the pass transistor logic shown below where  $V_W$  is the input and  $V_Z$  is the output. Use CMOS parameters on equation sheet (last page).

a) When  $V_W$  is initially 0V and then goes to  $V_{\rm DD}$ , find the final voltage values at  $V_X$ ,  $V_Y$ , and  $V_Z$ .

$$V_{x} = V_{00} = \frac{2.5V}{2.5-0.4}$$

$$V_{y} = V_{00} - V_{tw} = 2.5-0.4 = \frac{2.1V}{2.5-0.4}$$

$$V_{z} = V_{00} - V_{tw} = \frac{2.1V}{2.1V}$$

b) When  $V_W$  is initially  $V_{\rm DD}$  and then goes to 0V, find the final voltage values at  $V_X$ ,  $V_Y$ , and  $V_Z$ .

$$V_{x} = 0 - V_{tp} = 0.4V$$

$$V_{y} = V_{x} = 0.4V$$

$$V_{z} = V_{y} = 0.4V$$

Last Name:

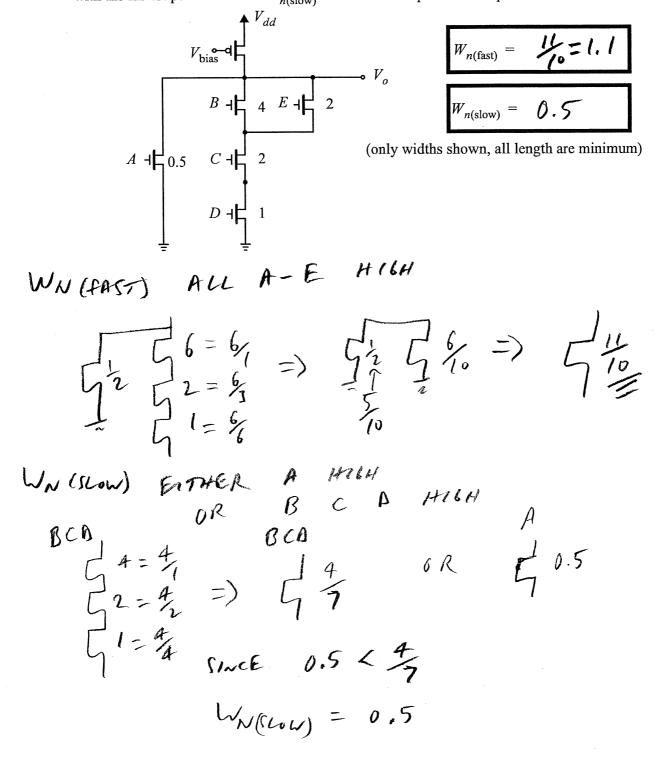

[6] Question 4: Using the concept of equivalent transistors, simplify the n-channel driver network shown below to a single pull-down transistor with a width of  $W_n$  (all lengths are same and minimum). Find this equivalent transistor for 2 cases:  $W_{n(\text{fast})}$  representing the input pattern with the fastest pull-down and  $W_{n(slow)}$  for the slowest pull-down input case.

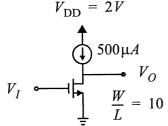

[6] Question 5: Consider the following inverter circuit. Assume the current source is ideal until the voltage across it is 1mV at which point it linearly drops to 0mA at 0V across it. Use CMOS parameters on equation sheet (last page).

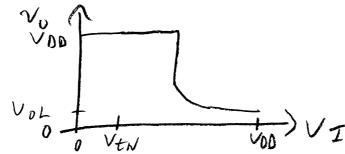

a) Sketch the input/output transfer curve for  $V_I$  from zero to  $V_{\mathrm{DD}}$  .

b) Find the output logic high and output logic low levels assuming  $V_I$  goes from 0 to  $V_{\rm DD}$ .

Find the output logic mgn and output logic low levels assuming

$$V_1$$

goes from  $V_1$  to  $V_2$ .

$$V_0 H = V_0 0 = \frac{2V}{2V}$$

$$\frac{1}{500\mu A} = (120e - 6)(10)[(2 - 0.4)V_{0L} - \frac{V_{0L}^{2}}{2}]$$

$$0.4167 = 1.6V_{0L} - \frac{V_{0L}^{2}}{2}$$

$$V_{0L}^{2} - 3.2V_{0L} + 0.833 = 0$$

$$V_{0L} = 2.91 \quad 6R \quad 0.286V$$

$$V_{0L} = 0.29V$$

Last Name:

**ECE334**

### **Digital Electronics**

### **Equation Sheet**

```

Constants: k = 1.38 \times 10^{-23} \text{ JK}^{-1}; q = 1.602 \times 10^{-19} \text{ C}; V_T = kT/q \approx 26 \text{ mV} at 300 °K;

\varepsilon_{0} = 8.854 \times 10^{-12} \text{ F/m}; \ k_{\text{ox}} = 3.9; \ \text{caps:} \ C_{\text{ox}} = (k_{\text{ox}} \varepsilon_{0})/t_{\text{ox}}; \ C_{j} = C_{j0}/(1 + V_{R}/\phi_{0})^{M_{j}};

\text{NMOS:} \ \beta_{n} = \mu_{n} C_{\text{ox}}(W/L); \ V_{ln} > 0; V_{\text{DS}} \ge 0; \text{(triode)} \ I_{D} = \beta_{n}((V_{\text{GS}} - V_{ln})V_{\text{DS}} - (V_{\text{DS}}^{2}/2)) \text{ (active)} \ I_{D} = 0.5\beta_{n}(V_{\text{GS}} - V_{ln})^{2};

(triode) V_{\rm DS} \leq (V_{\rm GS} - V_{tn}); (active) V_{\rm DS} \geq (V_{\rm GS} - V_{tn}); V_{tn} = V_{tn0} + \gamma(\sqrt{V_{\rm SB} + \phi_s} - \sqrt{\phi_s}); (subthreshold) I_D = I_{D0}e^{((V_{\rm GS} - V_{tn})/(nV_T))}(1 - e^{-V_{\rm DS}/V_T});

\mathbf{PMOS:} \ \ \beta_p = \ \mu_p C_{\mathrm{ox}}(W/L) \ \ ; \ \ V_{tp} < 0 \ ; V_{\mathrm{DS}} \leq 0 \ \ ; \\  (\mathrm{triode}) \ \ I_D = \ \beta_p ((V_{\mathrm{GS}} - V_{tp}) V_{\mathrm{DS}} - (V_{\mathrm{DS}}^2/2)) \ \ ; \\  (\mathrm{active}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\  (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\ (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\ (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\ (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\ (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\ (\mathrm{triode}) \ \ I_D = \ 0.5 \beta_p (V_{\mathrm{GS}} - V_{tp})^2 \ ; \\ (\mathrm{triode}) \

(triode) V_{DS} \ge (V_{GS} - V_{tp}); (active) V_{DS} \le (V_{GS} - V_{tp});

Simple cap model: C_g = C_{ox}WL; if L_{min}; C_{gu} = C_{ox}L_{min}; C_g = C_{gu}W; C_d = C_s = C_{du}W;

CMOS inverter: V_{\text{TH}} = (V_{\text{DD}} + V_{tp} + V_{tn}r)/(1+r); r = \sqrt{(\mu_n(W/L)_n)/(\mu_p(W/L)_p)}

RC delay est: t_{dr} = t_{df} = 1.2\tau; \tau = R_{eq}C; R_{eqn} = 2.5/(\mu_n C_{ox}(W/L)_n (V_{DD} - V_{tn})); R_{eqp} = 2.5/(\mu_p C_{ox}(W/L)_p (V_{DD} + V_{tp}));

(W_p/W_n)_{\rm opt} = \sqrt{\mu_n/\mu_p} \quad \text{Unit delay est:} \quad t_{\rm dl2}/t_{\rm df1} = (C_{\rm L2}/C_{\rm L1}) \times ((W/L)_{\rm n1}/(W/L)_{\rm n2})  Min delay: t_{\rm delay} = \tau_{\rm inv}(C_{\rm out}/C_{\rm in}); t_{\rm obs} = Nf\tau_{\rm inv}; f^N = C_{\rm out}/C_{\rm in}; usually f = 4 Power diss: P_{\rm dyn} = P_{1\to 0}fC_LV_{\rm DD}^2; P_{\rm dp} = 0.5P_{1\to 0}fV_{\rm DD}I_{\rm peak}(t_r + t_f); I_{\rm peak} = 0.5\beta_n(V_{\rm TH} - V_{fn})^2;

Elmore Delay: \tau_i \cong \sum C_k R_{ik}; dist RC, \tau \cong RC/2;

Interconnect: R = {k \choose \rho l}/(tw); R_{\Box} = \rho/t; C = (\epsilon_{ox}wl)/t; C = \epsilon_{ox}l(w/h + 0.77 + 1.06(w/h)^{0.25} + 1.06(t/h)^{0.5});

\textbf{Max delay constraint:} \ T_c \geq t_{\text{pcq}} + t_{\text{pd}} + t_{\text{setup}} \ \textbf{Min Delay constraint:} \ t_{\text{hold}} \leq t_{\text{ccq}} + t_{cd} \ \textbf{Metastability:} \ \textbf{MTBF} = e^{T/\tau_s} / (t_{\text{rd}} F_D F_{\text{CLK}})

SRAM: M3 is cell access transistor, M1 is inverter NMOS, M5 is inverter PMOS,

SRAM read: W_1/W_3 \ge (V_{DD} - V_A - V_{tn})^2/(2((V_{DD} - V_{tn})V_A - V_A^2/2)); I_{cell} = ((\mu_n C_{ox})/2)(W_3/L)(V_{DD} - 2V_{tn})^2/(2(V_{DD} - V_{tn})V_A - V_A^2/2))

\Delta V_{\rm BL} = (I_{\rm cell} \Delta t) / C_{\rm BL}

SRAM write: W_3/W_5 \ge (\mu_n(V_{DD} + V_{tb})^2)/(2\mu_n((V_{DD} - V_{tb})V_A - V_A^2/2))

```

# MOS Transistor; CMOS basic parameters. Channel length = $0.25 \mu m$ , $m_j = 0.5$ , $\phi_o = 0.9 \text{V}$

|      | V <sub>T0</sub> (V) | γ<br>(V <sup>0.5</sup> ) | $\mu C_{ox}$ $(\mu A/V^2)$ | λ<br>(V <sup>-1</sup> ) | $C_{ox}$ $(fF/\mu m^2)$ | С <sub>о</sub><br>(fF/µm) | $C_j$ $(fF/\mu m^2)$ | C <sub>jsw</sub><br>(fF/µm) |

|------|---------------------|--------------------------|----------------------------|-------------------------|-------------------------|---------------------------|----------------------|-----------------------------|

| NMOS | 0.4                 | 0.4                      | 120                        | 0.06                    | 6                       | 0.3                       | 2                    | 0.3                         |

| PMOS | -0.4                | 0.4                      | 30                         | 0.1                     | 6                       | 0.3                       | 2                    | 0.3                         |

$V_{T0}$  is the threshold voltage with zero bulk-source voltage;  $\gamma$  is used to account for non-zero bulk-source voltage;  $\mu C_{ox}$  is the transistor current gain parameter;  $\lambda$  is to account for the transistor finite output impedance (channel length modulation);  $C_{ox}$  is the gate capacitance per unit area;  $C_o$  is the gate overlap capacitance per unit length;  $C_j$  is the drain/source junction capacitance per unit area;  $C_{jsw}$  is the drain/source junction capacitance per unit length to account for drain/source perimeter capacitance. Assume this value is the same for all perimeters