## **University of Toronto**

#### **Term Test 2**

Date - Mar 16, 2011

Duration: 1.5 hrs

ECE334 — Digital Electronics Lecturer - D. Johns

# ANSWER QUESTIONS ON THESE SHEETS USING BACKS IF NECESSARY

- 1. Equation sheet is on last page of test.

- 2. Only tests written in pen will be considered for a re-mark.

- 3. Calculator type unrestricted

- 4. Grading indicated by []. Attempt all questions since a blank answer will certainly get 0.

| Student #:           | (max grade = 29) |  |  |

|----------------------|------------------|--|--|

| First Name:          |                  |  |  |

|                      | Total            |  |  |

| Last Name: SOLUTIONS | 5                |  |  |

|                      | 4                |  |  |

|                      | 3                |  |  |

|                      |                  |  |  |

Question

1

2

Mark

### [5] Question 1: Each correct answer is worth 0.5 marks.

For the questions below, circle one of True [T] or False [F].

- T F In a 45nm CMOS process, the subthreshold leakage current is due to current leaking in and out of the mosfet gates due to very thin gate oxides.

- T Pynamic direct-path power dissipation increases as clock and data edge slew-rates decrease.

- T F CMOS gates are made out of polysilicon so they will not melt during annealing.

- T (F) A self-aligned process means that the different masks are self-aligned with each other.

- T (F) A CMOS schmitt trigger is often used at the outputs of a digital chip to reduce noise.

- T F When creating metal wires on a chip, first silicon dioxide is grown and photoresist is used to etch where wires should exist. Next, aluminum is sprayed on using silicon dioxide as a mask.

- The silicon dioxide layer formed under the gate region is grown using wet oxidation instead of dry oxidation.

- T (F) Tungsten is used in via and contact holes due to its low resistance.

- The lowest level metal on a microchip is thicker than the highest level metal.

- For interconnect metal wires, the fringe capacitance is usually larger than the parallel plate capacitance.

[6] Question 2: Given that a minimum size inverter has a gate capacitance of 4fF and it's inherent delay equals 15ps, find the number of inverters for an inverter chain that minimizes the propogation delay to drive a 10pF load when using a fan-out factor of 4 for inverter sizing. Also, what is the propogation delay?

6 INVERTERS WITH SCAUNG SHOWN

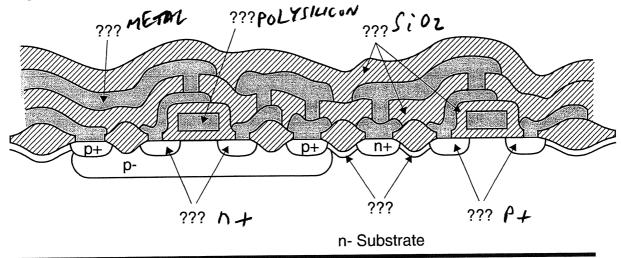

$t_d = (5)(4)(15PS) + (15PS)(\frac{10PF}{4PF})$ = 338 PS [6] Question 3: Consider the following cross-section of a p-well process (not n-well)

a) On the above diagram, label all the "???" signs with the material name (i.e. polysilicon, silicon dioxide, metal, p+, n+, p-, n-, etc.).

b) How is annealing performed and why is it performed after ion implantation?

TEMPERATURE IS IMPERSED AND THEN SLOWLY

DECREASED. IT IS USED TO BETTER DISTRIBUTE

TON CONCENTRATION AND REPAIRS DAMAGED

LATTICE

c) Name a dopant that can be used to make p-type silicon.

BORON

d) Name a dopant that can be used to make n-type silicon.

ARSENIC OR PHOSPHORUS

a) A metal wire has a thickness of 480nm, a width of 250nm and is 800nm above the p-substrate. Find the capacitance per unit length in units of  $fF/\mu m$ . Also, out of the total capacitance, find the percentage capacitance that relates to the parallel plate model and the percentage that relates to the fringe capacitance (the sum of the 2 should equal 100%).

$$C = k_{0} \times \mathcal{E}_{0} \left( \frac{1}{16} + 0.77 + 1.06 \left( \frac{1}{16} \right)^{0.25} + 1.06 \left( \frac{1}{16} \right)^{0.5} \right)$$

$$= (3.4) \left( 9.854e - 12 \right) \left( \frac{250}{800} + 6.77 + 1.06 \left( \frac{250}{800} \right)^{0.25} + 1.06 \left( \frac{480}{800} \right)^{0.5} \right)$$

$$= (3.45e - 11) \left( 0.3125 + 2.384 \right) = 93.1 \text{ pf/m} = 0.093 \text{ ff/mm}$$

$$9 C_{PAR} = \left( \frac{0.3125}{0.3125 + 2.384} \right) \times 100 = 1290$$

$$9 C_{PANGE} = 8890$$

b) A metal wire has a sheet resistance of 0.08  $\Omega/\Box$  and a capacitance of 0.2 fF/ $\mu m$ . Given that the wire is 1  $\mu m$  wide and 2mm long, construct a 3 segment  $\pi$ -model for the wire.

$$D = \frac{2 m m}{1 u m} = 2000 \quad R = 2000 \times 0.08 = 160 \Omega$$

$$C = 2000 \times 0.2 = 400 \text{ ff}$$

$$R_3 = 53.3 \Omega$$

$$R_4 = 53.3 \Omega$$

$$R_5 = 53.3 \Omega$$

$$R_5 = 53.3 \Omega$$

$$R_7 = 67 \Omega$$

c) For the above model in part b), what would be the Elmore time-constant for a source driving a resistor of size  $1k\Omega$  at one end of the wire with a capacitive load at the other end of 67

[6] Question 5: Consider the Schmitt trigger below. All transistors have minimum channel length and transistor relative widths are shown. Derive an expression for the switching threshold as  $V_{in}$  is increased from 0V. Ignore the body effect.

$$V_{in} = \frac{1}{\sqrt{N_{0}}} \frac{V_{0D}}{V_{0D}}$$

$$V_{in} = \frac{1}{\sqrt{N_{0}}} \frac{V_{in}}{V_{in}}$$

$$V_{in} = \frac{1}{\sqrt{N_{0$$

(blank sheet for scratch calculations)

#### **Digital Electronics**

```

Constants: k = 1.38 \times 10^{-23} \text{ JK}^{-1}; q = 1.602 \times 10^{-19} \text{ C}; V_T = kT/q \approx 26 \text{ mV} at 300 °K;

\varepsilon_0 = 8.854 \times 10^{-12} \text{ F/m}; k_{\text{ox}} = 3.9; caps: C_{\text{ox}} = (k_{\text{ox}} \varepsilon_0) / t_{\text{ox}}; C_j = C_{j0} / (1 + V_R / \phi_0)^{M_j}

NMOS: \beta_n = \mu_n C_{\text{ox}}(W/L); V_{tn} > 0; V_{\text{DS}} \ge 0; (triode) I_D = \beta_n ((V_{\text{GS}} - V_{tn}) V_{\text{DS}} - (V_{\text{DS}}^2/2)); (active) I_D = 0.5 \beta_n (V_{\text{GS}} - V_{tn})^2;

(triode) V_{DS} \le (V_{GS} - V_{tn}); (active) V_{DS} \ge (V_{GS} - V_{tn}); V_{tn} = V_{tn0} + \gamma(\sqrt{V_{SB} + \phi_s} - \sqrt{\phi_s});

(subthreshold) I_D = I_{D0}e^{((V_{GS} - V_{In})/(nV_T))}(1 - e^{-V_{DS}/V_T});

PMOS: \beta_p = \mu_p C_{\text{ox}}(W/L); V_{tp} < 0; V_{DS} \le 0; (triode) I_D = \beta_p ((V_{GS} - V_{tp})V_{DS} - (V_{DS}^2/2)); (active) I_D = 0.5\beta_p (V_{GS} - V_{tp})^2;

(triode) V_{\rm DS} \ge (V_{\rm GS} - V_{tp}); (active) V_{\rm DS} \le (V_{\rm GS} - V_{tp});

\textbf{Simple cap model:} \ \ C_g = \ C_{\text{ox}} WL \ ; \ \text{if} \ L_{\min}; \ C_{gu} \equiv C_{\text{ox}} L_{\min}; \ C_g = \ C_{gu} W \ ; \quad C_d = \ C_s = \ C_{du} W \ ;

CMOS inverter: V_{\text{TH}} = (V_{\text{DD}} + V_{tp} + V_{tn}r)/(1+r); r = \sqrt{(\mu_n(W/L)_n)/(\mu_p(W/L)_p)}

RC delay est: t_{dr} = t_{df} = 1.2\tau; \tau = R_{eq}C; R_{eqn} = 2.5/(\mu_n C_{ox}(W/L)_n (V_{DD} - V_{th})); R_{eqp} = 2.5/(\mu_p C_{ox}(W/L)_p (V_{DD} + V_{tp}));

(W_p/W_n)_{\text{opt}} = \sqrt{\mu_n/\mu_p} Unit delay est: t_{\text{df2}}/t_{\text{df1}} = (C_{\text{L2}}/C_{\text{L1}}) \times ((W/L)_{\text{n1}}/(W/L)_{\text{n2}})

Min delay: t_{\text{delay}} = \tau_{\text{inv}}(C_{\text{out}}/C_{\text{jn}}); \text{total}_{\text{delay}} = Nf\tau_{\text{inv}}; f^{N} = C_{\text{out}}/C_{\text{in}}; usually f = 4

Power diss: P_{\text{dyn}} = P_{1 \to 0}fC_{L}V_{\text{DD}}^{2}; P_{\text{dp}} = 0.5P_{1 \to 0}fV_{\text{DD}}I_{\text{peak}}(t_{r} + t_{f}); I_{\text{peak}} = 0.5\beta_{n}(V_{\text{TH}} - V_{tn})^{2};

Elmore Delay: \tau_i \cong \sum C_k R_{ik}; dist RC, \tau \cong RC/2;

Interconnect: R = {\kappa \choose \rho l}/(tw); R_{\Box} = \rho/t; C = (\epsilon_{ox}wl)/t; C = \epsilon_{ox}l(w/h + 0.77 + 1.06(w/h)^{0.25} + 1.06(t/h)^{0.5});

Max delay constraint: t_c \ge t_{pcq} + t_{pd} + t_{setup} Min Delay constraint: t_{hold} \le t_{ccq} + t_{cd} Metastability: MTBF = e^{T/\tau_s}/(t_{rd}F_DF_{CLK})

SRAM: M3 is cell access transistor, M1 is inverter NMOS, M5 is inverter PMOS,

W_1/W_3 \ge (V_{\rm DD} - V_{\rm A} - V_{\rm tn})^2/(2((V_{\rm DD} - V_{\rm tn})V_{\rm A} - V_{\rm A}^2/2)) \quad ; \quad I_{\rm cell} = ((\mu_n C_{\rm ox})/2)(W_3/L)(V_{\rm DD} - 2V_{\rm tn})^2

\Delta V_{\rm BL} = (I_{\rm cell} \Delta t) / C_{\rm BL}

SRAM write: W_3/W_5 \ge (\mu_p(V_{DD} + V_{to})^2)/(2\mu_n((V_{DD} - V_{to})V_A - V_A^2/2))

```

# MOS Transistor; CMOS basic parameters. Channel length = $0.25 \mu m$ , $m_i = 0.5$ , $\phi_o = 0.9 \text{V}$

|      | V <sub>T0</sub> (V) | $\begin{pmatrix} \gamma \\ (v^{0.5}) \end{pmatrix}$ | $\mu C_{ox} $ $(\mu A/V^2)$ | $\begin{pmatrix} \lambda \\ (\nu^{-1}) \end{pmatrix}$ | $C_{ox}$ $(fF/\mu m^2)$ | $C_o$ $(fF/\mu m)$ | $C_j$ $(fF/\mu m^2)$ | C <sub>jsw</sub><br>(fF/µm) |

|------|---------------------|-----------------------------------------------------|-----------------------------|-------------------------------------------------------|-------------------------|--------------------|----------------------|-----------------------------|

| NMOS | 0.4                 | 0.4                                                 | 120                         | 0.06                                                  | 6                       | 0.3                | 2                    | 0.3                         |

| PMOS | -0.4                | 0.4                                                 | 30                          | 0.1                                                   | 6                       | 0.3                | 2                    | 0.3                         |

$V_{T0}$  is the threshold voltage with zero bulk-source voltage;  $\gamma$  is used to account for non-zero bulk-source voltage;  $\mu C_{ox}$  is the transistor current gain parameter;  $\lambda$  is to account for the transistor finite output impedance (channel length modulation);  $C_{ox}$  is the gate capacitance per unit area;  $C_o$  is the gate overlap capacitance per unit length;  $C_j$  is the drain/source junction capacitance per unit area;  $C_{jsw}$  is the drain/source junction capacitance per unit length to account for drain/source perimeter capacitance. Assume this value is the same for all perimeters