# A Frequency-Scalable 15-bit Incremental ADC for Low Power Sensor Applications

Joshua Liang Electrical and Computer Engineering University of Toronto Toronto, Ontario, Canada Email: joshua.liang@utoronto.ca

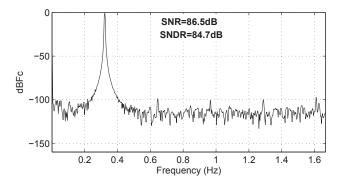

Abstract—A 15-bit low-power incremental ADC is designed for sensor applications. The ADC is designed to be frequency-scalable by 1000 times from 1.67S/s to 1.67kS/s. To reduce power, an opamp with class AB characteristics is used. The design was fabricated in  $0.18\mu m$  CMOS and occupies an area of  $0.35mm^2$ . Configured to operate at full-rate as a Delta-Sigma modulator, the ADC achieves 91.8dB peak SNDR while consuming 83 $\mu$ W from a 1.8-V supply. Operating as an incremental converter, the ADC powers off periodically to achieve frequency scalability, maintaining 84.7dB to 88.9dB peak SNDR while operating from 1.67S/s to 1.67kS/s and scaling analog power by up to 500 times.

### I. INTRODUCTION

Micromachined MEMS sensors have been applied increasingly in the automotive industry. Crucial to the development of power-efficient sensor solutions, is the development of lower-power interfaces including ADCs. This work addresses a class of piezoresistive pressure sensor devices applied in devices ranging from altimeters to tire pressure monitors. To reduce design costs, it was desired that a single ADC be capable of scaling its signal bandwidth by 1000 times from Hz to kHz operation. A power efficient solution would also have to scale its power by the same factor of 1000.

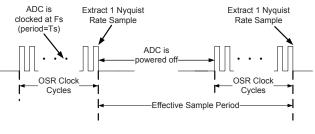

Scaling the power and bandwidth of analog circuits by 1000 times can be quite difficult. For example, by varying the bias current of circuits, their power consumption can be scaled. However, it is not easy to maintain correct circuit operation over a wide range of bias conditions. The alternative, used in [1] and [2] and chosen in this design is to always operate the circuits with the same bandwidth and sample rate, and power down circuits between conversions. In this way, analog circuits always operate at a consistent operating point. This scheme does however require a finite state machine to power circuits on and off. This controller must always remain on, consuming some static power.

The relatively high (15-bit) resolution and low bandwidth required for this application are amenable to the use of oversampled (delta-sigma) ADCs. Implementing this power-scaling scheme is not straight-forward with oversampled ADCs. Delta-sigma modulators rely on integrator circuits which accumulate charge in capacitors. To power down circuits between samples, these integrator circuits would have to maintain their charge while circuits are shut down. Due to leakage and startup issues, this is impractical. It was therefore decided to use a subset of delta-sigma modulators, the incremental ADC, which uses OSR back-to-back conversion steps (where OSR is the oversampling ratio) to produce each output and is then reset. Due to their simple post-filters, incremental converters may achieve lower SNR than equivalent delta-sigma ADCs, but their resettable operation makes them suitable for power-scaled operation.

This paper presents an incremental converter that can scale its bandwidth from 1.67Hz to 1.67kHz while maintaining 84.7-88.9dB peak SNDR. Power consumption at full-rate is  $83\mu$ W for the ADC

David A. Johns Electrical and Computer Engineering University of Toronto Toronto, Ontario, Canada Email: johns@eecg.utoronto.ca

Fig. 1. Illustration of Frequency-Scaled Operation

and  $42\mu$ W for the on-chip post-filter. Section II and III summarize the system and circuit-level design of the ADC. Section IV describes the experimental results.

## **II. SYSTEM DESIGN**

# A. Incremental Converter Design

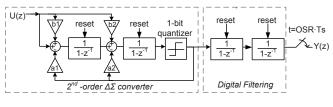

Incremental converters combine a delta-sigma modulator with a digital post-filter to form a Nyquist rate ADC [3]. The system operates for OSR cycles, before both the delta-sigma modulator and filter are reset. The output of the post-filter is sampled after every OSR cycles, providing a Nyquist rate data output. Although more advanced filtering might be used, at a minimum, post-filters consist of a cascade of digital integrators.

The required order of delta-sigma modulator is determined in part by the desired OSR. In this design, to reduce loading on the sensor device and ease the requirements of any input buffer that might be used, the input sampling capacitor sizes were reduced to 550fF. To achieve sufficiently low thermal noise, an OSR of 1500 was required. At this OSR, a 2nd order incremental converter offered sufficiently low quantization noise to obtain a thermal noise-limited design with the desired 15-bit accuracy. Therefore, a 2nd order incremental converter was designed, consisting of a 2nd order deltasigma modulator, followed by 2 digital post-integrators.

Fig. 2. 2nd Order Incremental Converter

#### B. 2nd Order Delta-Sigma Modulator

The delta-sigma modulator uses a cascade of integrators feedback (CIFB) topology [4] as shown in Fig. 2. The input feed-in to the

# 978-1-4244-5309-2/10/\$26.00 ©2010 IEEE

input of the second stage integrator reduces input signal content in the power-hungry first integrator stage and potentially suppresses non-linearities in that stage. The lack of an input feed-in to the quantizer eliminates the need for an additional summation before the quantizer. This leads to a low-pass, as opposed to an all-pass signal transfer function (STF), but it was found not to impact performance significantly. Due to the high OSR used, optimized zeros were impractical to implement so the zeros of the noise transfer function (NTF) were left at DC (z=1). Filter coefficients were selected using the Delta-Sigma Toolbox [4]. Also due to the high OSR, the opamps used required relatively high gains of 50dB or more.

A single-bit quantizer was used to avoid the need for additional digital circuits to suppress non-linearities in the feedback DAC. This is also desirable in incremental converters since it allows the first post-filter stage to be a simple counter.

# **III. CIRCUIT IMPLEMENTATION**

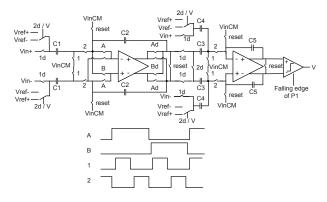

# A. Delta-Sigma Modulator

The delta-sigma modulator was implemented using switchedcapacitor circuits as shown in Fig. 3. Capacitors were shared between the input and feedback DAC to prevent additional thermal noise. Using a full 1.8V supply, clock-boosting was not required. The

Fig. 3. Switched-Capacitor Implementation of  $\Delta\Sigma$

first stage integrator was chopped [5] at half of the sample rate to suppress flicker noise, permitting operation at low frequencies. The chopper clock phases A and B were generated identically to the nonoverlapping clocks 1 and 2 using a second clock generator, driven by an on-chip clock divider.

## B. Opamp Design

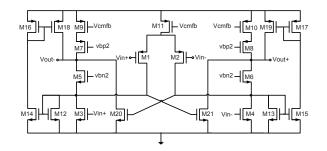

To minimize power and noise, it was desired to maximize the input transconductance of the opamps. This can be accomplished using class-AB techniques ([6],[7]) which combine the gm of complementary NMOS and PMOS devices. However such circuits often require additional biasing networks such as level shifters, or complicate common mode feedback. To avoid this, a solution was chosen that achieves much of the performance advantages of class-AB designs (see Fig. 4).

The design consists of a Folded-Cascode opamp in which both the PMOS input differential pair (M1/M2) and NMOS current sources (M3/M4) are driven. The design combines the gm of both pairs of devices. By allocating more of the current to the differential pair than the folding network, the improvement in gm is significant. To enhance the opamp's slew rate, a current mirror network, which turns on to provide additional current was added. The network is controlled by

the diode-connected devices M12 & M13, which only turn on under large signal conditions. An increased slew rate reduces the duration of slewing as the opamp output settles. This can relax the opamp's bandwidth requirements as more time is available for linear settling.

Fig. 4. Pseudo Class-AB Opamp

Since thermal noise from the second stage integrator is suppressed by the first stage integrator gain, its capacitor sizes were reduced requiring less power from the second stage opamp. Since potential power savings were lower in the second stage, a simple NMOSinput telescopic opamp was used. The NMOS tail current source was removed to lower the input common mode and ease the use of NMOS switches at the opamp input.

# C. Power-Down Control

As mentioned, in power-scaled operation, circuits (including bias circuits) are disabled between conversions to reduce power. The cascode devices in the opamps were used as switches to switch the opamps on and off. By disabling the clock input to the clock generators, digital circuits could be similarly powered down.

To reduce transients in analog circuits as they are powered on, bias circuits were powered on and allowed to settle for several clock periods before powering on the amplifier circuits [1]. Allowing this startup time increased overall power consumption by less than 10%.

#### D. Digital Circuits

The digital post-filter was synthesized using standard library cells. A shift-register was used to provide the digital output serially. An on-chip controller was also synthesized to control the power-scaled/reseting operation of the incremental converter. The controller was programmable to accommodate different sampling rates and additional options such as the duration of startup phases. To reduce its power, an on-chip divider was used to reduce the clock rate entering the controller.

#### **IV. EXPERIMENTAL RESULTS**

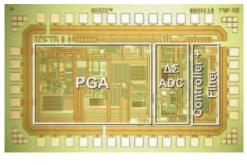

The complete design was fabricated in 1P6M  $0.18\mu m$  CMOS with a 1.8-V supply. Fig. 5 shows the ADC integrated with a previously designed programmable gain amplifier [2]. The ADC itself, including digital filter and controller occupy an active area of  $0.5mm \times 0.7mm = 0.35mm^2$ .

#### A. Delta-Sigma Modulator

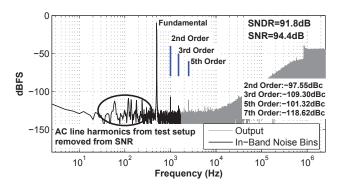

The ADC was configured to operate as a traditional delta-sigma modulator to evaluate its performance. A fully differential, low-distortion signal generator was used as the signal source. In this case, the filtering and resetting operations were disabled and the output of the delta-sigma modulator was sampled directly. In this configuration, the ADC achieves 91.8dB peak SNDR at an input level of 990mVpp differential (-3.6dBFS) over its 1.67kHz bandwidth. (SNDR values

# Fig. 5. Die Photo

include tones up to the 7th harmonic.) Fig. 6 shows the ADC's output spectrum. Several 60Hz harmonics seen in the ADC output were present in the signal source output when viewed with a spectrum analyzer. Since they are were not caused by the ADC, they were discounted from SNR calculations. From Fig. 6, the delta-sigma ADC actually has a usable bandwidth of up to 10kHz. Reducing the OSR from 1500 to 250, the delta-sigma still achieves 85.8dB peak SNDR over 10kHz of bandwidth. This was however traded off to increase SNR over a reduced bandwidth required in this application.

Fig. 6. Output Spectrum From Delta-Sigma Modulator

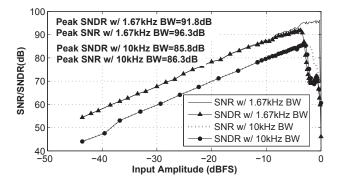

Fig. 7. SNR vs. Amplitude for Input @500Hz

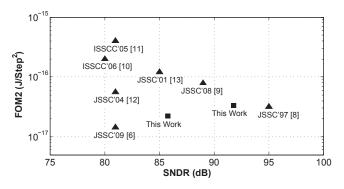

ADCs can be compared in terms of bandwidth and accuracy (measured here in SNDR) using the following Figure-of-Merit (FOM) [8]:

$$FOM1 = \frac{4kT \times Bandwidth \times SNDR}{Power} \tag{1}$$

where k is Boltzmann's constant and T is the temperature in Kelvin. This FOM compares the number of conversion steps achieved relative to the power consumed and thermal noise level. Inverting the FOM and assuming all comparisons are made at room temperature, leads

TABLE I Measurement Results for Delta-Sigma Modulator

|                     | Configuration 1  | Configuration 2  |

|---------------------|------------------|------------------|

| Supply Voltage      | 1.8V             | 1.8V             |

| Maximum Input Swing | 1.5Vpp diff.     | 1.5Vpp diff.     |

| Clock Rate          | 5MHz             | 5MHz             |

| OSR                 | 1500             | 250              |

| Signal Bandwidth    | 1.67kHz          | 10kHz            |

| Total Analog Power  | 33µW             | 33µW             |

| Digital Clock Power | $50\mu W$        | $50\mu W$        |

| Peak SNDR           | 91.8dB @ 990mVpp | 85.8dB @ 1.06Vpp |

| Peak SNR            | 96.3dB @ 1.44Vpp | 86.3dB @ 1.10Vpp |

| DR                  | 96.5dB           | 89.1dB           |

to an adjusted FOM of:

$$FOM2 = \frac{Power}{Bandwidth \times SNDR}$$

(2)

which measures relative power consumption and has units of  $J/(step)^2$ .

Fig. 8 compares this work to several recent low-power discretetime delta-sigma modulators using FOM2 described above. This design has performance comparable with other recent work but does consume more power due to its relatively high supply voltage. Digital clock power in particular, is quite high. The other designs all use supply voltages of 1V or less. [6] achieves the lowest FOM to date using inverters and a 0.7V supply. It should also be noted that [8] has a larger 3V input swing, allowing it to achieve a higher SNR. However, as mentioned, a conventional delta-sigma modulator cannot easily be power-scaled, necessitating the use of an incremental converter.

Fig. 8. FOM2 vs. SNDR for Various Discrete-Time  $\Delta\Sigma$  Modulators

## B. Power-Scalable Incremental Converter

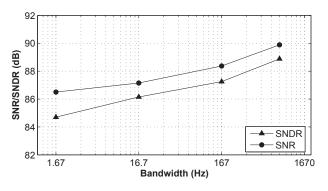

Operating as an incremental converter, the delta-sigma modulator is periodically reset and powered on and off by the on-board controller. The digital post-filter outputs digital data serially at the Nyquist rate. The peak SNR achievable from the on-chip filter is expected to be roughly 1.25dB [3] lower than can be achieved with a deltasigma modulator using an ideal decimation filter. The measured difference was 2dB. As a result, if power scaling is not required, it is advantageous to operate the ADC simply as a delta-sigma. Fig. 10 shows the peak SNR/SNDR for the incremental ADC as its bandwidth is scaled. At lower frequencies, the SNR drops off due to increased noise at low frequencies.

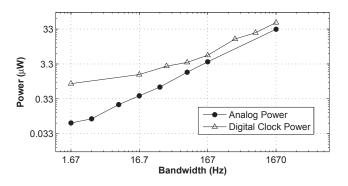

Operating at full-rate, the incremental converter consumes  $83\mu$ W for the delta-sigma and  $42\mu$ W for the post-filter. When power-scaled, measurements confirmed that the analog power of the delta-sigma ADC could scale from  $33\mu$ W down to 67nW at the lowest bandwidth

Fig. 9. Output Spectrum of Incremental Converter (Power-Scaled by 1000)

Fig. 10. Peak SNR/SNDR vs. Signal Bandwidth

due to the varying duty cycle (see Fig. 11). Power scaling of digital clock circuits was limited to roughly 50 times in measurements. This is because several stages of on-chip clock buffers always remain active, leading to a fixed minimum power consumption. This could be remedied by disabling the clock before any buffering is used.

For testing purposes, the on-chip controller was designed with wide programmability and consumed  $4.3\mu$ W. This power could be reduced using a simplified, less flexible controller. In addition, although the presence of the controller limits the minimum power of the ADC to  $4.3\mu$ W, in the intended application, combined with a variable gain amplifier, the controller would account for only a small portion of the interface's total power.

Fig. 11. ADC Power vs. Signal Bandwidth

#### V. CONCLUSION

A power-scalable incremental ADC has been presented which can scale its bandwidth by 1000 times from 1.67Hz to 1.67kHz while achieving 84.7-88.9dB SNDR. Operating at full-rate, power consumption is  $83\mu$ W for the ADC and  $42\mu$ W for the on-chip

TABLE II Specifications of Power-Scalable Incremental Converter

| Technology                       | 0.18µm CMOS      |

|----------------------------------|------------------|

| Supply Voltage                   | 1.8V             |

| Maximum Input Swing              | 1.5Vpp diff.     |

| Signal Bandwidth                 | 1.67Hz - 1.67kHz |

| Total Analog Power               | 67nW - 33µW      |

| Digital Clock Power              | 0.9µW - 50µW     |

| Digital Filter Power (full-rate) | $42\mu W$        |

| Peak SNDR                        | 84.7dB - 88.9dB  |

| Peak SNR                         | 86.5dB - 89.9dB  |

| Active Area                      | $0.35mm^{2}$     |

post-filter. Analog power was confirmed to scale as desired, but several clock buffers which always remain active limited digital power scaling to roughly 50 times.

#### ACKNOWLEDGEMENT

The authors would like to thank Bosch Research and Technology Center and the National Sciences and Engineering Council of Canada (NSERC) for research funding and Canadian Microelectronics Corporation (CMC) for fabrication services.

#### REFERENCES

- I. Ahmed and D. Johns, "A 50 MS/s (35 mW) to 1 kS/s (15μW) power scaleable 10b pipelined ADC with minimal bias current variation," in *Solid-State Circuits Conference*, 2005. Digest of Technical Papers. ISSCC. 2005 IEEE International, Feb. 2005, pp. 280–589 Vol. 1.

- [2] A. Nafee and D. Johns, "A 14 bit micro-watt power scalable automotive MEMS pressure sensor interface," in *Solid-State Circuits Conference*, 2008. ESSCIRC 2008. 34th European, Sept. 2008, pp. 450–453.

- [3] J. Markus, J. Silva, and G. C. Temes, "Theory and applications of incremental ΔΣ converters," *IEEE Transactions on Circuits and Systems— Part I: Fundamental Theory and Applications*, vol. 51, no. 4, pp. 678– 688, Apr. 2004.

- [4] R. Schreier, "The delta-sigma toolbox version 7.2," Feb. 2008.

- [5] J. M. de la Rosa, S. Escalera, B. Perez-Verdu, F. Medeiro, O. Guerra, R. del Rio, and A. Rodriguez-Vazquez, "A cmos 110-dB@40-kS/s programmable-gain chopper stabilized third-order 2-1 cascade sigmadelta modulator for lower-power high-linearity automotive sensor ASICs," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 11, pp. 2246– 2264, Nov. 2005.

- [6] Y. Chae and G. Han, "Low voltage, low power, inverter-based switchedcapacitor delta-sigma modulator," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 2, pp. 458–472, Feb. 2009.

- [7] Z. Cao, T. Song, and S. Yan, "A 14 mW 2.5 MS/s 14 bit ΔΣ modulator using split-path pseudo-differential amplifiers," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 10, pp. 2169–2179, Oct. 2007.

- [8] S. Rabii and B. Wooley, "A 1.8-V digital-audio sigma-delta modulator in 0.8-m CMOS," *Solid-State Circuits, IEEE Journal of*, vol. 32, no. 6, pp. 783–796, Jun 1997.

- [9] M. G. Kim, G.-C. Ahn, P. Hanumolu, S.-H. Lee, S.-H. Kim, S.-B. You, J.-W. Kim, G. Temes, and U.-K. Moon, "A 0.9V 92 dB doublesampled switched-RC delta-sigma audio ADC," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 5, pp. 1195–1206, May 2008.

- [10] J. Goes, B. Vaz, R. Monteiro, and N. Paulino, "A 0.9V ΔΣ modulator with 80dB SNDR and 83dB DR using a single-phase technique," in *Solid-State Circuits Conference*, 2006. ISSCC 2006. Digest of Technical Papers. IEEE International, Feb. 2006, pp. 191–200.

- [11] G. cho Ahn, D. young Chang, M. Brown, N. Ozaki, H. Youra, K. Yamamura, K. Hamashita, K. Takasuka, G. C. Temes, and U.-K. Moon, "A 0.6V 82dB ΔΣ audio ADC using switched-RC integrators," in *Solid-State Circuits Conference*, 2005. ISSCC 2005. Digest of Technical Papers. IEEE International, Feb. 2005, pp. 166–167.

- [12] L. Yao, M. Steyaert, and W. Sansen, "A 1-V 140-µW 88-dB audio sigmadelta modulator in 90-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 11, pp. 1809–1818, Nov. 2004.

- [13] M. Dessouky and A. Kaiser, "Very low-voltage digital-audio  $\Delta\Sigma$  modulator with 88-dB dynamic range using local switch bootstrapping," *Solid-State Circuits, IEEE Journal of*, vol. 36, no. 3, pp. 349–355, Mar 2001.

2421