# **Automatic Porting of Binary File Descriptor Library**

### Maghsoud Abbaspour

Electrical and Computer Engineering University of Toronto

Oct 19, 2001

maghsoud@eecg.toronto.edu

#### **Outline**

- Motivation.

- Retargetability(What, Why).

- Architecture Description Languages

- Retargetable binary File Descriptor library.

- Binary File Format(ELF).

- Application Binary Interface(ABI) and ABI modeling.

- Relocation (Definition and modeling).

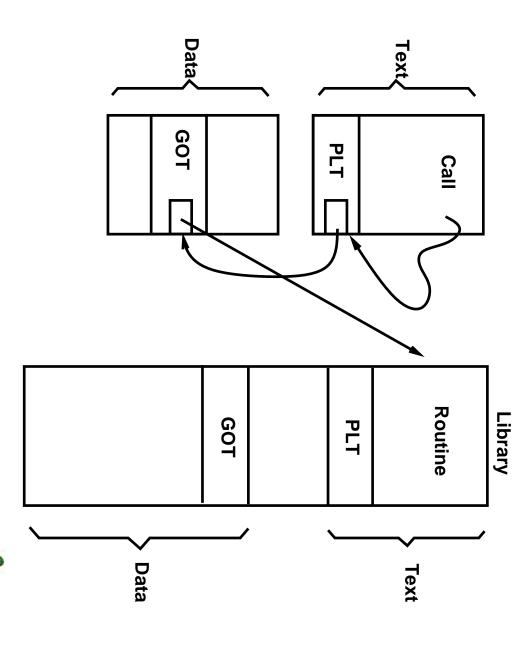

- PLT and GOT (definitions and PLT modeling).

- Implementation.

- Result.

## Retargetability, what?

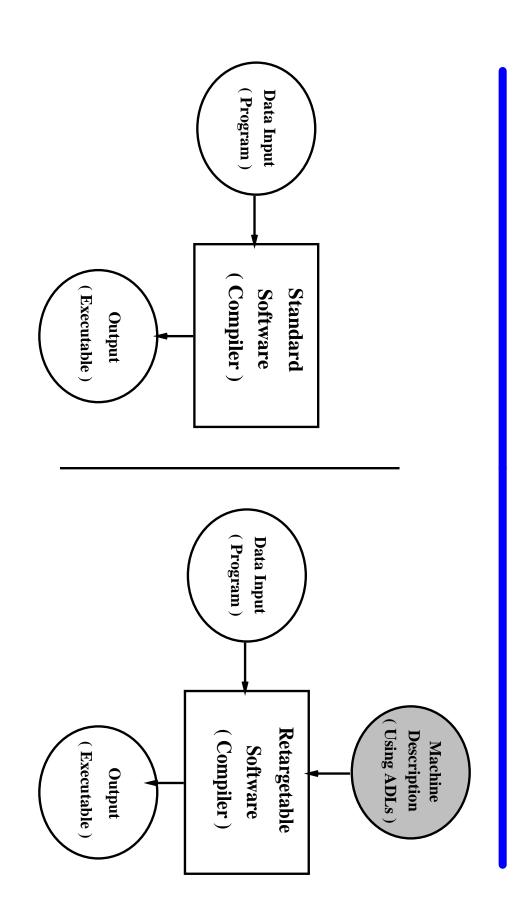

processors. Different level for switching to another target: A software is said to be retargetable if it can be applied to range of target

- **Portability**: rewriting some part of the software to use in new target

- description and target dependent parts are generated automatically. Retargetability: target characteristic is captured using target

- Machine independence: no change.

## Retargetability, why?

- Time-to-Market or Time-to-Money.

- Software toolkit for new processors (ASIPs).

- Design Complexity (Expoenetially ).

- Growing number of applications(Network processors, Communications processors,...).

- Small life time, high risk market, Lower-design volume

## Design Automation Tool Supports

- Hardware Design Support

- RTL model, RTL Floorplanning, Logic synthesis and ...

- Retagrgetable Compiler and Retagrgetable Simulator for architecture exploration.

- Software Design Supoort

- Retagrgetable Compiler.

- Retagrgetable Simulator.

- RetagrgetableBinary Tools( Assembler, Linker, Debugger,... ).

# **Architecture Description Languages (ADLs)**

- HDLs can not be used to generate toolkit.

Instruction Set Architecture (ISA) description languages.

- Architecture Exploration

- Can not run an Application program on a HDL simulator in behavioral

- Running an Application program is very time consuming on a HDL simulator in structural level.

- support). Simple and general (text only, simple and wide range architecture

- Suport automatic tool-kit generation(Compiler, Simulater,...)

#### ADLs Cont.

- Architecture View

- micro-architecture compnents and stores information is used for Synthesis

- ISA View

- Instruction set modeling and binary encoding information is used for Compiliation tools generation.

- Simulation View

- Timing information is used for Simulation tools generation.

#### **ISA Modeling**

An **ISA architectural model** is a member of

```

ISA = tuple

:\langle

angle^{Instrn};

: ILP;

: ABI;

: \langle \rangle^{Store};

```

level parallelism and A is a ABI model of the micro-architecture. where S is a set of stores, I is the set of instructions, P is the instruction

#### What is BFD? ΑIX **RS6000** 1386 Spa Linux RS6000 1386 BFD 3 **Application** Front-End Back-End Sparc င္ပ Solaris RS6000 П 1386 Sparc ELF COFF AOUT

## **ELF**: Binary File Format(BFF)

#### What is ELF?

#### Linking view

ELF header

Program header table(optional)

Section 1

Section n

į

:

Section header table

#### **Execution view**

ELF header

Program header table

Segment 1

Segment 2

Section header table(optional)

## **Application Binary Interface (ABI)**

#### What is the ABI?

An ABI defines a binary interface for application programs that are compiled and packaged for a specific OS running on a specific hardware architecture.

#### ABI Component:

- Calling Convention.

- Relocation.

- PLT entries (ELF obj format specific ).

#### Relocation

- what is relocation

- Relocations of Sparc:

| $R\_SPARC\_PC22$ | $R\_SPARC\_GOT22$ | $R\_SPARC\_WDISP30$ | $R\_SPARC\_DISP32$ | $R\_SPARC\_32$ | $R\_SPARC\_16$ | Name        |

|------------------|-------------------|---------------------|--------------------|----------------|----------------|-------------|

| S + A - P >> 10  | G >> 10           | S+A-P>> 2           | S + A - P          | S + A          | S + A          | Calculation |

#### Binary Code = 0100,0000,0000,0000 and a relocation entry will be added for this symbol Reloc Expr. = S + A - P >> 2 Control Transfer to "PC + (4 x disp30) CALL: 01 r\_offset(P), index (sym),type, addend(A) disp30 value(S),sizename, type,... .rel.text .sym .text Reloc. Entry

### Relocation Cont.

Relocation model A relocation type is a member of

```

bitpos

bitsize

right shift \\

Reloc = tuple {

complain

expCode

\{ignore, bit, sign, unsigned\};

: int;

: int;

: int;

: byte;

: int;

```

### Relocation Cont.

- id is an unique integer identifier.

- $expCode = \langle C_7, C_6, ..., C_0 \rangle$  encodes the expression  $\Sigma_i C_i P_i$ , with  $P_7, ...P_0$  being -GOT, A, B, G, GOT, L, -P, S respectively.

### Relocation Cont.

- rightshift represents the number of bits at the right side of the calculated  $\Sigma_i C_i P_i$  that should be dropped.

- bitpos and bitsize represents the bit position as well as the size of the relocation field within the instruction or datum to be relocated.

- complain encodes the action to take when specific type of overflow occurs

# Procedure Linkage Table(PLT) and Global Offset Table(GOT)

#### PLT modeling

## A PLT entry is a member of

```

instrns

size

plt = tuple \ \big\{

: [\ ]^{int};

: int;

```

- size is the number of words (4 byte) for each PLT entry.

- instrns is a sequence of binary words.

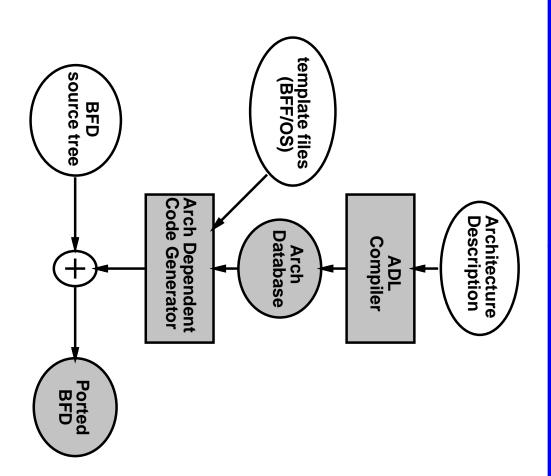

#### **Implementation**

#### **Implementation**

Complexity of ABI specification.

| i386 | sparc | Processor              |

|------|-------|------------------------|

| 13   | 26    | ABI complexity (#line) |

- Input file Templates.

- Genrated files.

| 1           | /ld/config/mysparc-elf.mt  |

|-------------|----------------------------|

| 868         | /ld/Makefile.in            |

| 9           | elf32_mysparc.sh           |

|             | /ld/emulparam/             |

| 183         | /ld/configure.in           |

| 6582        | /bfd/elfcode.h             |

| 44          | /bfd/cpu-mysparc.c         |

| 785         | /bfd/target.c              |

| 1014        | config.sub                 |

| 229         | /include/elf/common.h      |

| 1482        | /bfd/elf32-mysparc.c       |

| 166         | /bfd/config.bfd            |

| 286         | /bfd/configure.in          |

| 112         | /bfd/configure.host        |

| 1483        | /bfd/archures.c            |

| 3           | /bfd/config/mysparc-elf.mt |

| (generated) |                            |

| #line       | Generated Files            |