### TECHNOLOGY MIGRATION FOR HARD IPS

by

Fang Fang

A thesis submitted in conformity with the requirements for the degree of Master of Applied Science Graduate Department of Electrical and Computer Engineering University of Toronto

Copyright © 2003 by Fang Fang

### **Abstract**

Technology Migration for Hard IPs

#### Fang Fang

#### Master of Applied Science

Graduate Department of Electrical and Computer Engineering

University of Toronto

2003

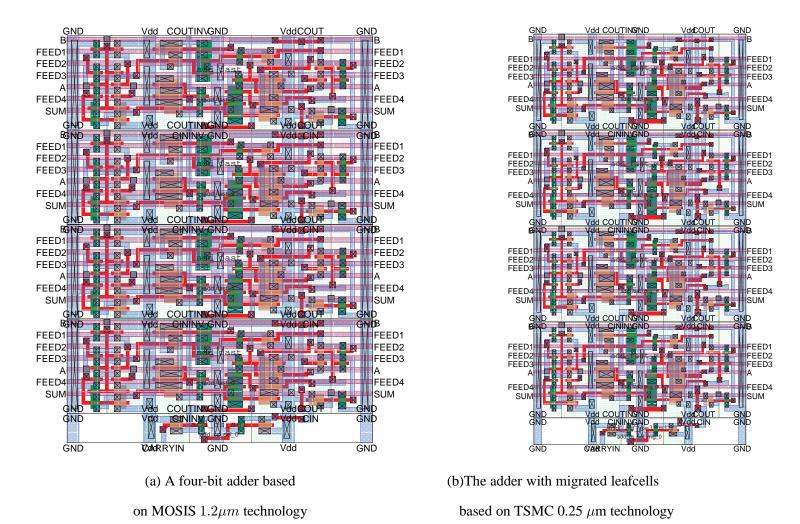

As the foundries accelerate their update of advanced processes with increasingly complex design rules, the cost of hard intellectual property (IP) development becomes prohibitively high. A technology migration tool that can port hard IPs from old technology to new technology is presented in the thesis. The thesis makes four primary contributions: First, it proposes a new fast design rule constraint generation algorithm that further limits the searcing spaces. Second, it introduces a dual-pass strategy to solve the high level layout architecture constraints for migrating all the library leaf cells. Third, it proposes a new optimization metric, called geometric closessness, that can help retain advanced design intention. Finally, soft constraints method is proposed to trace the conflicting constraints specified by the users. We test our migration tool by successfully migrating Berkeley low power libraries, originally developed for 1.2um MOSIS process to TSMC 0.25um and 0.18um technologies.

## Acknowledgements

## **Contents**

| 1 | Intr | oduction                                          | 1  |

|---|------|---------------------------------------------------|----|

|   | 1.1  | Motivation                                        | 3  |

|   | 1.2  | Contribution                                      | 3  |

|   | 1.3  | Organization of thesis                            | 4  |

| 2 | Bacl | kground                                           | 5  |

|   | 2.1  | Virtual Grid Compaction and Shear-line Compaction | 5  |

|   | 2.2  | Constraint Graph Compaction                       | 7  |

|   | 2.3  | Hierarchical Layout Compaction                    | 11 |

|   | 2.4  | Other Developments                                | 12 |

| 3 | Mig  | ration Engine                                     | 15 |

|   | 3.1  | Background                                        | 15 |

|   | 3.2  | Migration Engine                                  | 28 |

|   | 3.3  | Design Rule Constraint Generation                 | 30 |

|   | 3.4  | Objective function                                | 46 |

|   | 3.5  | Integer Linear Programming Solver                 | 51 |

| 4 | Mig  | ration for datapath and standard cell libraries   | 52 |

|   | 4.1  | Datapath library migration                        | 52 |

|   | 4.2  | Standard Cell Library Migration                   | 61 |

| 5            | Exp | eriments and Conclusion | <b>67</b> |

|--------------|-----|-------------------------|-----------|

|              | 5.1 | Experimental Setup      | 67        |

|              | 5.2 | Experimental Result     | 68        |

|              | 5.3 | Limitation              | 76        |

|              | 5.4 | Conclusion              | 78        |

|              | 5.5 | Future work             | 79        |

| 6            | App | endix                   | 80        |

| Bibliography |     |                         |           |

## **List of Tables**

| 5.1 | Layout architecture characteristics                             | 71 |

|-----|-----------------------------------------------------------------|----|

| 5.2 | Layout structure characteristics                                | 75 |

| 5.3 | User specified layout architecture requirements for cell haf001 | 78 |

| 6.1 | Experiment results of datpath library migration                 | 82 |

| 6.2 | Experiment results for standard cell library migration          | 84 |

# **List of Figures**

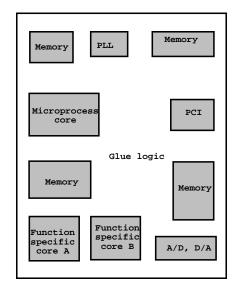

| 1.1 | A general architecture of SoC                                                   | 2  |

|-----|---------------------------------------------------------------------------------|----|

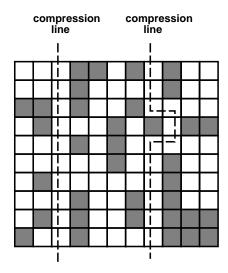

| 2.1 | Before virtual grid compaction.                                                 | 6  |

| 2.2 | After virtual grid compaction.                                                  | 6  |

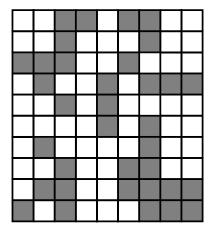

| 2.3 | A spacing constraint is presented by an edge in the directed graph              | 7  |

| 2.4 | A's shadow is blocked by B. So there is no edge between A ad C in the con-      |    |

|     | straint graph                                                                   | 8  |

| 2.5 | Each circuit element is expanded by D/2 in both positive and negative X direc-  |    |

|     | tions. The elements that stay within the same slot in scanning bar are recorded |    |

|     | in the same X coordinate bin                                                    | 9  |

| 2.6 | The constraint graph for a cell to be pitch matched                             | 11 |

| 2.7 | Port abstraction method                                                         | 12 |

| 2.8 | Wire jogging.                                                                   | 13 |

| 3.1 | A layout is composed of several planes                                          | 16 |

| 3.2 | The tile structure in metal1 plane                                              | 18 |

| 3.3 | The process to find right neighor tiles                                         | 21 |

| 3.4 | The process to locate the tile that contains a given point                      | 23 |

| 3.5 | Tile enumeration.                                                               | 26 |

| 3.6 | Each edge rule can be applied in any of the four directions                     | 26 |

| 3.7 | An example of edge rule                                                         | 27 |

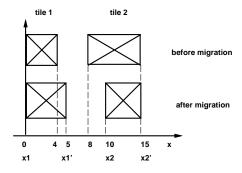

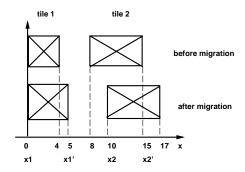

| 3.8  | Tiles are aligned in grids                                                                    | 29 |

|------|-----------------------------------------------------------------------------------------------|----|

| 3.9  | Each tile has new position and shape after migration with no design rule viola-               |    |

|      | tions                                                                                         | 30 |

| 3.10 | Design rule checker looks for non-OKType tiles within constraint region                       | 31 |

| 3.11 | (a) An example layout in active plane. The shaded rectangles 1, 3, 5, 6 and 10                |    |

|      | represent poly tiles. Rectangle 8 is diffusion tile. Other rectangles are all space           |    |

|      | tiles. (b) The constraint graph generated from poly spacing rule                              | 32 |

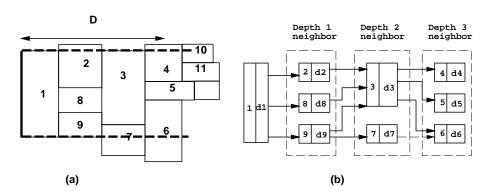

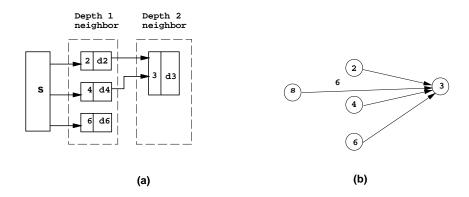

| 3.12 | (a) A fraction of a layout plane. Tile 1 is the source tile that is being pro-                |    |

|      | cessed for edge rule constraint generation. (b) Depth-K shadowing neighbor-                   |    |

|      | hood graph for tile 1                                                                         | 34 |

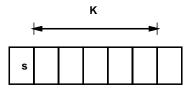

| 3.13 | The best case for Depth-K searching algorithm                                                 | 37 |

| 3.14 | The maximum number of tiles to be visited for tile s                                          | 38 |

| 3.15 | A leaf cell muxf201                                                                           | 38 |

| 3.16 | The constraint graph for IntraPlane constraints                                               | 39 |

| 3.17 | Corner constraint region checking                                                             | 39 |

| 3.18 | (a) In the old layout, tile 3 doesn't overlap with tile s in X direction. (b) After           |    |

|      | X direction migration and Y direction migration, tile 3 moves into shadow area                |    |

|      | of tile 1. (c) Interpass Constraint graph for tile s (d) Interpass constraints for            |    |

|      | tile s                                                                                        | 40 |

| 3.19 | N-well tile stays on well plane while diffusion tile stays on active plane                    | 42 |

| 3.20 | (a)The Depth-K shadowing neighborhood graph for interplane edge rule (b)                      |    |

|      | InterPlane edge rule constraint between source tile $s$ and tile $3$                          | 43 |

| 3.21 | InterPlane constraints generated for cell muxf201                                             | 44 |

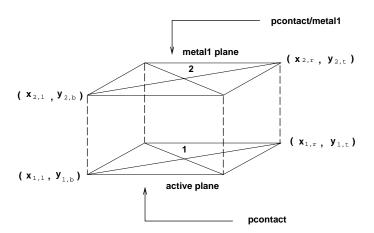

| 3.22 | A contact has different tile types on the planes it connects. The poly contact in             |    |

|      | this figure has <b>pcontact</b> tile (tile 1) on active plane and <b>pcontact/metal1</b> tile |    |

|      | (tile 2) on metal 1 plane                                                                     | 45 |

| 3.23 | Connect constraints generated for cell muxf201                                                | 46 |

| 3.24 | Tile 1 is the leftmost tile in a layout and $x_l$ is the X coordinate of its left edge. |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | Tile 2 is the rightmost tile in the layout and $x_r$ is the X coordinate of its right   |    |

|      | edge                                                                                    | 47 |

| 3.25 | The old layout and migrated layout with minimum perturbation objective func-            |    |

|      | tion                                                                                    | 49 |

| 3.26 | The old layout and migrated layout with geometric closeness objective function.         | 50 |

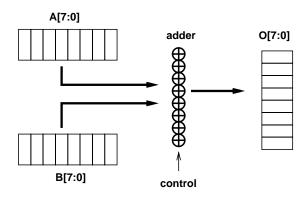

| 4.1  | An 8-bit adder block diagram.                                                           | 53 |

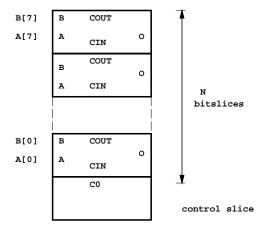

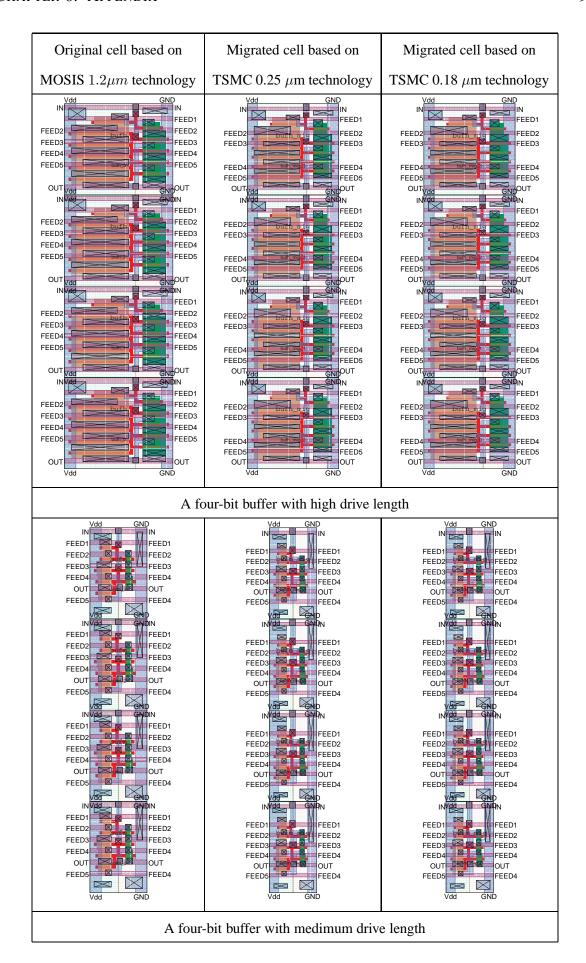

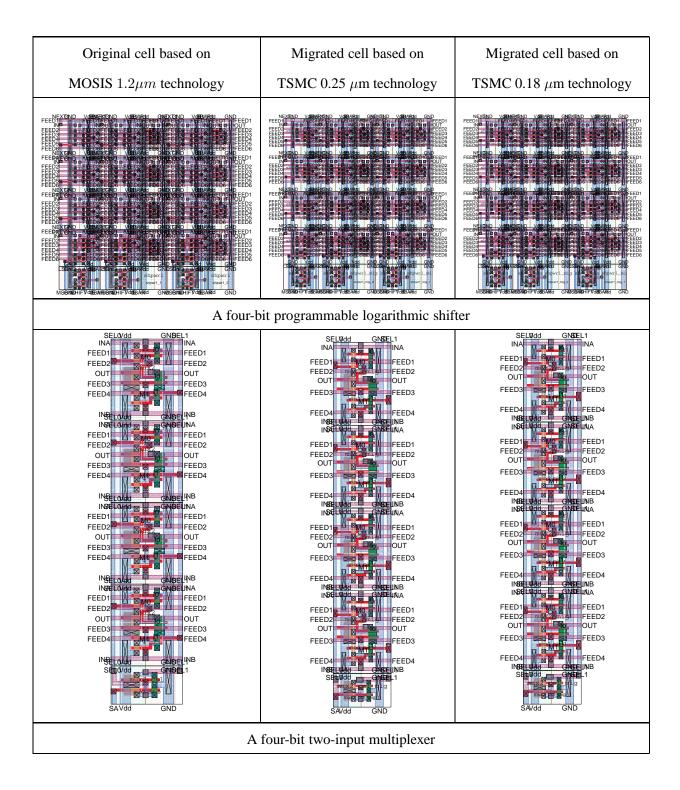

| 4.2  | An 8-bit adder constructed by abutting 8 adder bitslices and 1 control slice            | 54 |

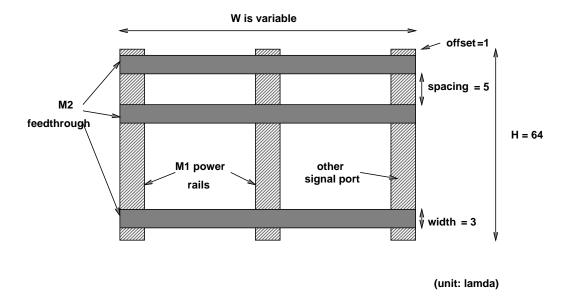

| 4.3  | An example of datapath library cell                                                     | 54 |

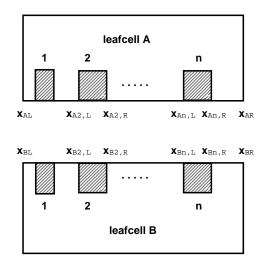

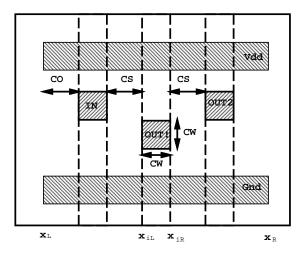

| 4.4  | Port matching of leaf cells                                                             | 55 |

| 4.5  | Dual-pass migration strategy                                                            | 57 |

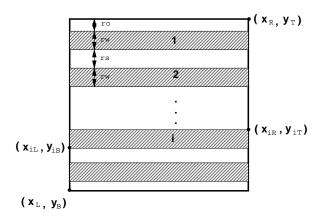

| 4.6  | Cell with routing track for data signals                                                | 58 |

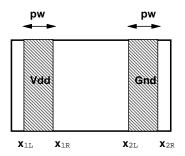

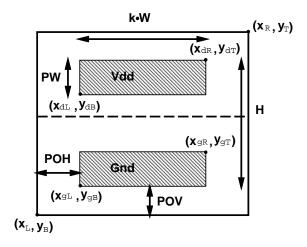

| 4.7  | The width of each power net has to be equal to $pw$ given by the designer in the        |    |

|      | specification file.                                                                     | 59 |

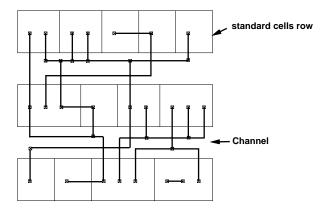

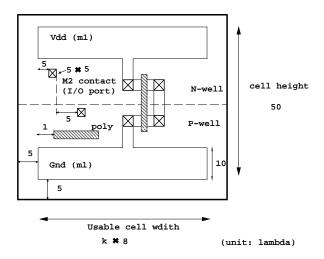

| 4.8  | Standard cells design                                                                   | 62 |

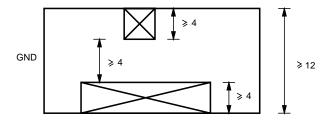

| 4.9  | Layout architecture for a standard cell library                                         | 63 |

| 4.10 | All I/O ports stay in fixed grids                                                       | 64 |

| 4.11 | The requirements on power rails                                                         | 65 |

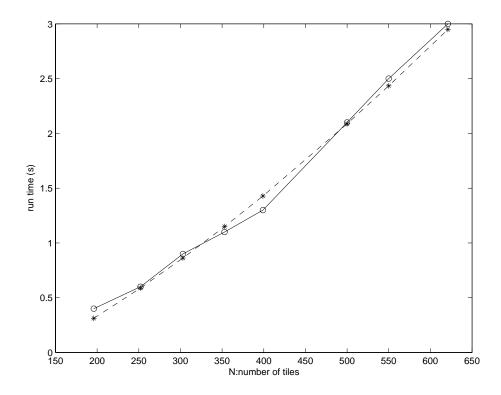

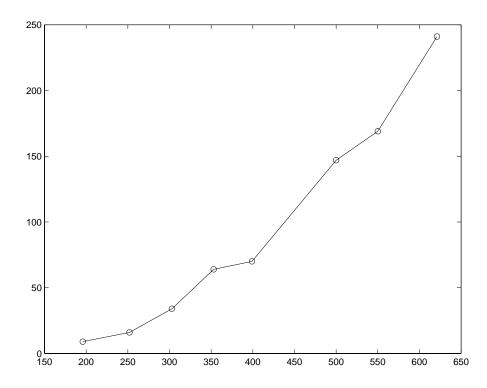

| 5.1  | The run time of design rule constraint generation                                       | 69 |

| 5.2  | The run time of ILP solver                                                              | 70 |

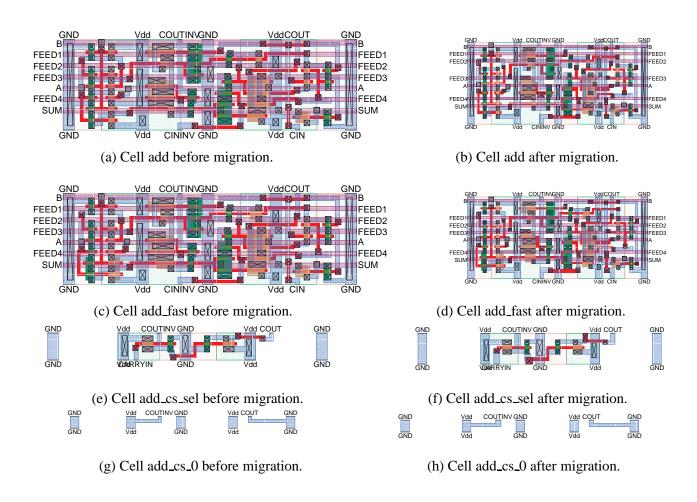

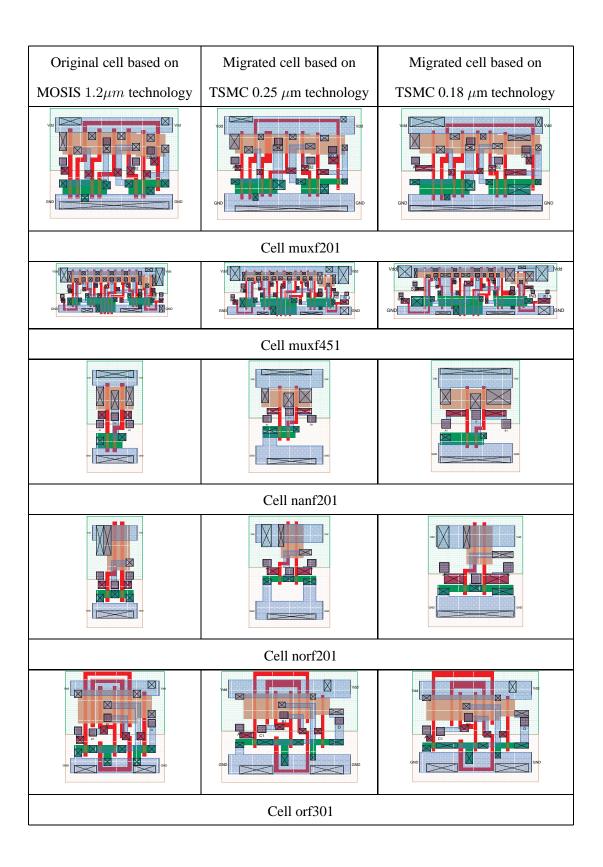

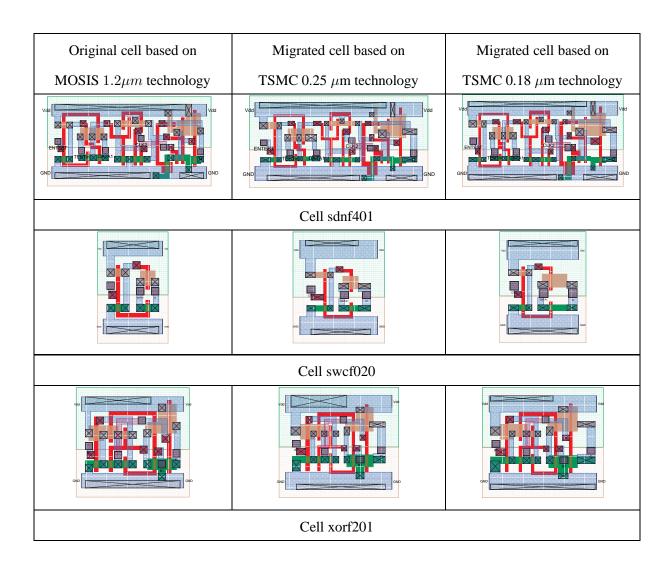

| 5.3  | The leafcells for ripple carry adder                                                    | 71 |

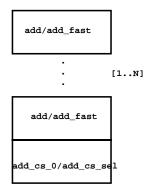

| 5.4  | The floorplane of an N bit adder                                                        | 72 |

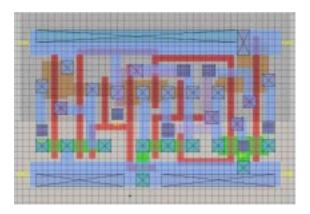

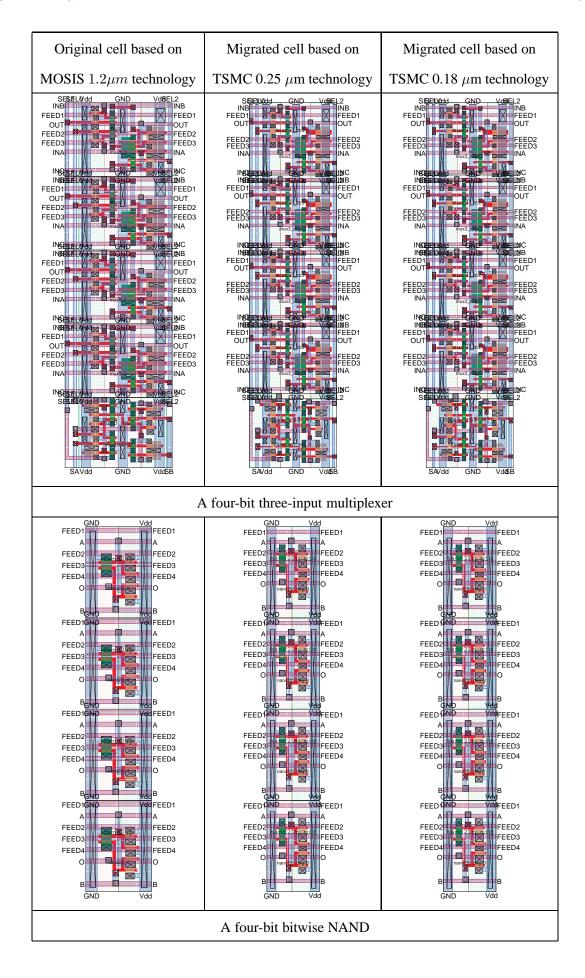

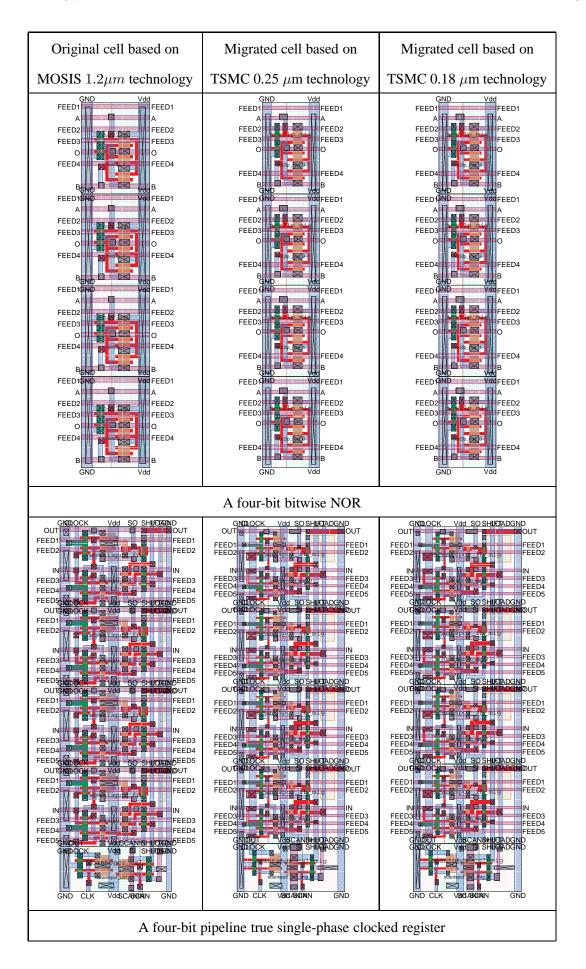

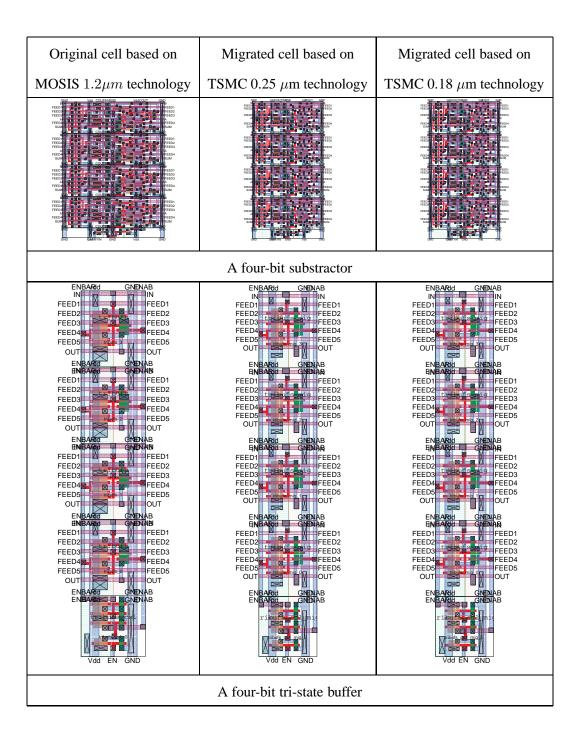

| 5.5  | Migration of a four-bit adder                                                           | 73 |

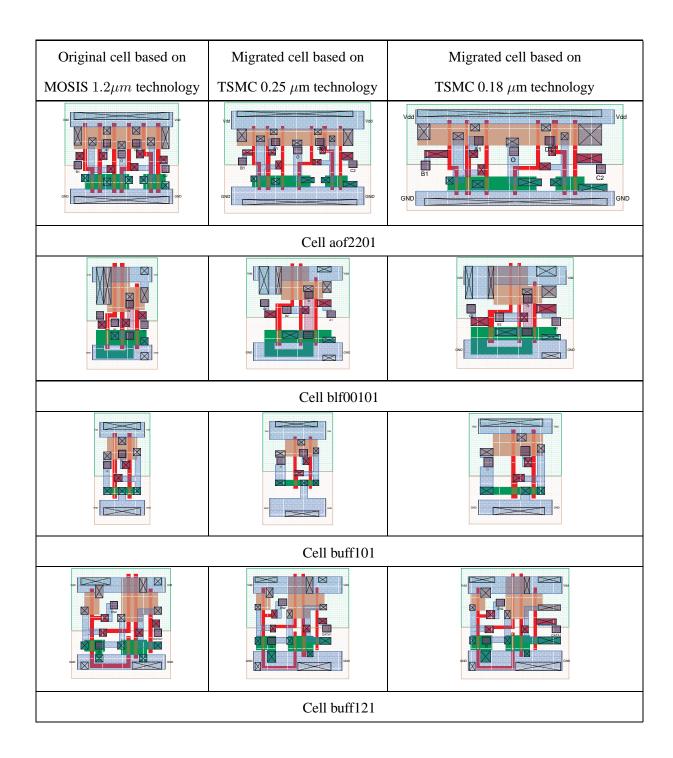

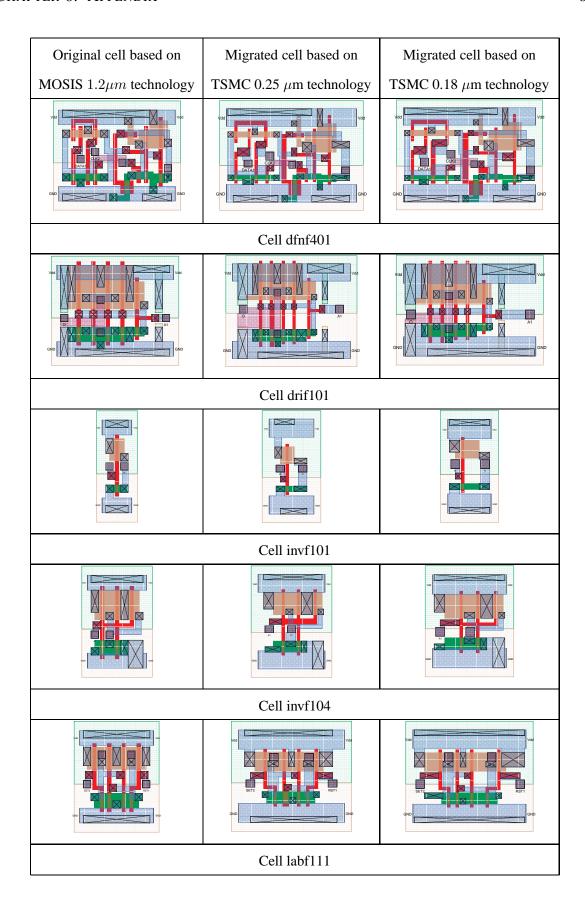

| 5.6  | Two old standard cells based on standard MOSIS $1.2 \mu m$ technology                   | 74 |

| 5.7  | Migrated cells based on TSMC 0.18µm technology                                          | 74 |

| 5.8  | The migration results under geometric closeness objective function and mini- |    |

|------|------------------------------------------------------------------------------|----|

|      | mum perturbation objective function                                          | 76 |

| 5.9  | Cell haf001 before migration                                                 | 76 |

| 5.10 | Cell haf $001$ after migrated towards TSMC $0.18 \mu m$ technology           | 77 |

| 5.11 | The design rule requirements on power rail                                   | 77 |

## Chapter 1

## Introduction

The ASIC technology has evolved from a chip-set philosophy to system-on-chip (SoC) concept. SoC is generally defined as an IC designed by stitching multiple stand-alone VLSI designes to provide full functionality for an application [21]. A general architecure of today's SoC is shown in Figure 1.1. The definition of SoC implies that the complexity of SoC is greatly increased compared to ASIC. And with the time-to-market pressure, the SoC desingers are tuning to block-based design approach that emphasis on design reuse in order to achieve fast development. The macros, also called intellectual-properties (IPs), usually come in tow forms: soft IPs, delivered in the form of synthesizable RTL code, and hard IPs, delivered in the form of fully placed and routed netlist and fixed layout layout mapped to a specific technology. There are some trade-offs between choosing hard IPs and choosing soft IPs for block reuse. Since the soft IPs can be re-synthesised by the SoC integrators for their chosen technology, they are favored in terms of their portablitity and re-usability. On the other hand, the hard IPs have a physical representation, and are delivered in the form of layout file such as GDSII file. The SoC is essentially a combination of these hard IPs that implement function blocks such as memories, microprocessors in Figure 1.1. Therefore, they are more predictable than soft IPs in terms of timing, power and area and result in less effor during SoC integration.

The primary bottleneck that prevents wide adoption of hard IPs is the dependency of layout

Figure 1.1: A general architecture of SoC.

on process. In standard ASIC design, a library with a rich selection of gates with different drive strengths, buffer sizes and dual polarities for functions must be provided to IC designers. Today's standard cell library contains hundreds of leaf cells with different functions and different drive lengths. There are many unique design considerations such as porosity, apsect ration, power distribution, etc., related to physical design of these libraries. It takes great design effort to create such libraries from scratch. Therefore most fabless companies choose to use libraries offered by hard IP companies to avoid the high cost associated with library development. To make things worse, manufacturing processes are updated every 18 months, each time using a different set of design rules. This makes the development cost of hard IPs too high even for hard IP vendors, since they have to offer different versions for different foundries as well. Automatic layout migration technology, which can port libraries from old technology to new technology and thus amortize the high development cost associated with custom design across different foundries and processes, is therefore crucial for the sustained growth of IP-based design.

### 1.1 Motivation

Layout migration tools available today cannot cope with all the challenges involved. First, most migration tools are based on layout compaction, a technology developed a decade ago, when the layout area is the primary concern. Layout compaction tends to compress space between polygons recklessly as long as design rules are not violated. In modern design using aggressive circuit styles in deep submicron processes, space is often among the first class citizens of advanced layout considerations, for example, to combat signal integrity. Other specialized advanced circuit considerations, such as new transistor sizes, device matching, are rarely considered in an integrated fashion. Second, most techniques reported in the literature are designed to migrate a specific circuit that uses a library of cells, rather than the library itself. Without considering the overall library architecture such as power/ground net width, routing track number and port matching, the cell layouts migrated under this circuit-driven strategy work only for the specific circuits, so there is no guarantee that they work under all occasions, and each time a new circuit is migrated, all the leaf cells in the whole library need to be migrated again.

## 1.2 Contribution

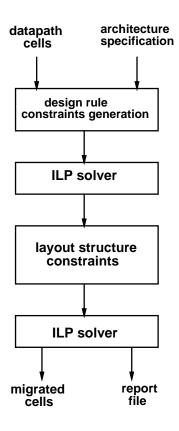

An integer linear programming (ILP) based migration framework which is customized for datapath IP and standard cell IP migration is presented in this thesis. New libraries based on new technologies can be generated when given the libraries of the old process and new library architecture specifications. Several innovations that help solve the difficult problems discussed earlier are listed below:

• A new design rule generation algorithm, *Depth-K searching algorithm*, which takes less searching effort than the shadow propagation method currently employed for constraint generation [18], is used in this project.

- A new optimization objective, called *geometric closeness*, to reward geometric resemblance of migrated layout to the original layout is introduced in this project. Under this metric, space is explicitly represented. Preservation of space and non-space polygons is given equal priority. This ensures that the original layout design considerations are not corrupted

- In order to address the overall library architecture requirements, a *dual-pass strategy* is employed in the migration tool that helps meet high level layout architecture constraints. This is in contrast to the top-down constraint propagation strategy employed by traditional hierarchical compactors, which are limited only to area minimization.

- Since the library architecture is specified by users, they may conflict with design rules, which will lead to an infeasible solution. A new concept, called *soft constraints*, is proposed in order to obtain a best-effort solution. A concrete feedback is provided where architecture requirements fail, which thereby helps the user interactively define the proper library architecture.

## 1.3 Organization of thesis

The rest of the thesis is organized as follows: First a review of previous work is given in chapter 2. Then a detailed discussion of the basic migration engine implementation is presented in chapter 3. Chapter 4 talks about what are the specific layout architecture requirements for datapath library and standard cell library and how the requirements are solved with the dual-path approach. The experimental results are given in Chapter 5. Finally, Chapter 6 gives the conclusion and summarizes the future work.

## Chapter 2

## **Background**

Automatic layout migration was among the oldest CAD problems investigated and a large body of research was carried out under the layout compaction problem. Surveys of layout compaction can be found in [6] and [9]. Early compactors are performed on symbolic layout in which circuit elements are presented by simple lines or rectangles, known as *sticks*. The symbolic layout compaction methodologies include shear-line approach, virtual grid approach and constraint graph approach, which will be discussed in the following sections.

## 2.1 Virtual Grid Compaction and Shear-line Compaction

Commercial layout systems such as **MULGA** [25] use the virtual grid compaction approach to compress the layout. Once the symbolic layout is generated, the virtual grid compaction method compresses space by moving objects. The procedure includes two main steps:

- search for movable objects by consultation with layout topology and design rules;

- perform the compaction by moving these objects.

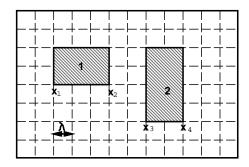

In order to identify the movable objects and the moving distance, the layout is represented by a  $m \times n$  matrix as shown in Figure 2.1. Each entry of the matrix represents a mask element marked as a shaded cell or space marked as a blank cell. The size of the grid unit is determined

by design rules. Objects are restricted to one unit move usually. The movable objects are decided by searching for a path of blank cells across the matrix. The path could be a straight line or a union of straight lines connected as shown in Figure 2.1. Therefore, the compaction is proceeded by repeatedly removing paths along X and Y direction until no path could be found. The migrated layout is shown in Figure 2.2.

Figure 2.1: Before virtual grid compaction.

Figure 2.2: After virtual grid compaction.

The shear-line approach is very similar to virtual grid compaction except that the grid spacing is fixed to the worst case design rule [8] [1].

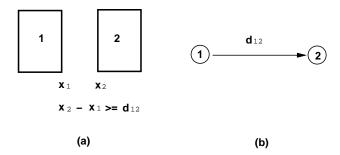

The compaction is made easy with the matrix representation of the layout. However, the grid size must be carefully decided because coarse grid results in smaller matrix and thus less run time, but the compaction may not be efficient. On the other hand, high grid resolution will lead to large matrix and thus slow down the run time. Another disadvantage of this compaction method is that the optimization goal can only be the minimization of the layout area. With this approach, no other optimization goals can be achieved.

## 2.2 Constraint Graph Compaction

The constraint graph compaction was first discussed by Hsueh and Pederson [18]. Many other compaction tools such as **FLOSS** [5], **CABBAGE** [18] and **SLIM** [1], use this strategy to compact layouts. In this approach, the topology constraints and design rule requirements are presented with a weighted directed graph, called *constraint graph*. Each vertex represents a circuit element. For each spacing constraint between two elements, there is an arc (i, j) with weight  $d_{ij}$ .

Figure 2.3: A spacing constraint is presented by an edge in the directed graph.

The new position of each element can be obtained either by running longest path algorithm or by using linear programming solver depending on the optimization goal the user chooses. Because of its flexibility, we adopt this approach in our migration tool.

#### 2.2.1 Constraint Generation

The key part of constraint graph compaction is design rule constraint generation, which is used to identify the spacing relationship among all the elements according to design rules and layout topology. The constraint generation process is very similar to design rule checking except that the circuit elements outside of checking region need to be considered as well because they may be pushed into the checking region after compaction. One of the most often used methods to generate constraints is called "shadow-propagation" method used in CABBAGE [18]. This approach trims the searching area by shining an imaginary light from the element being checked as shown in Figure 2.4. Based on the assumption that the relative positions between two elements will not be changed, which means that the element C will not move to the shadow of element A in Figure 2.4, only the constraints between the given element and the elements that the shadow first meet are generated. The worst case complexity for shadow-propagation method is proven to be  $O(N^{1.5})$ , where N is the total number of elements in the symbolic layout. With the experimental result, the experimental complexity is found to be  $O(N^{1.2})$ .

Figure 2.4: A's shadow is blocked by B. So there is no edge between A ad C in the constraint graph.

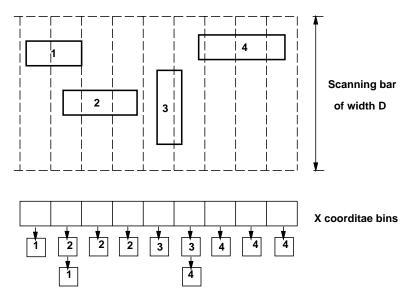

Another approach to generate constraints come from a design rule checking method called scan line approach [20], which is demonstrated in Figure 2.5. The circuit elements that stay too far from the checking element are filtered out by the scanning bar of width D, which is the worst-case design rule distance. The X coordinate bins record all the circuit elements for design rule checking. There are two key issues related with this approach. First, the number

of bins in the X direction must be carefully decided. Too few bins may cause the missing of constraints. On the other hand, too many bins results in redundant constraints as the same pair of elements may occupy many bins. The scan line approach sets the bin number according to statistical analysis of element density so that each pin covers 2.52 elements on average. The other key issue is that interative sorting of the shape record buffer when adding or deleting elements. The experimental data indicate that with N elements in the layout, the expected time complexity required is O(Nlog(N)) [20].

Figure 2.5: Each circuit element is expanded by D/2 in both positive and negative X directions. The elements that stay within the same slot in scanning bar are recorded in the same X coordinate bin.

With constraint graph generated, some techniques are used to reduce the redundant edges and thus reduce the complexity of solving the constraint graph. The intervening group method incrementally generates the the constraint graph by effectively avoiding adding vertices when a pair of vertices are constrained to be far enough [12]. A combination of shadowing-propagation and binning is proposed with worst case complexity claimed to be  $O(N^{1.5})$ . All these techniques are based on the shadowing-propagation method to build constraint graph and remove the unnecessary edges after the constraint graph is generated.

The constraint generation methods discussed above are all performed on sybmolic layout. In symbolic layout, the circuit elements such as transistor, contact and wire are modelled as sticks snapped to virtual grids. At symbolic layout level, circuit elements do not have detailed mask information. The positions of circuit elements are decided by respecting the high level design rules such as minimum spacing rules and minimum width rule, etc. In order to generate real mask layout, another process to transform symbolic layout to mask layout is needed after symbolic layout compaction. In this thesis, we directly migrate the mask layout without taking the symbolic layout transfromation step. A new constraint generation method applied directly on mask layout represented in corner stitching data structure, called *Depth-K searching algo-rithm*, is proposed in this thesis that can further reduce the searching area by limiting the depth it traverses than the shadowing-propagation algorithm. And with corner stitching layout representation, it avoids the iterative sorting of shape buffers in scan line approach. The data in the Appendix show that the experimental run time is proportional to  $O(N^{1.4})$ .

### 2.2.2 Objective Function

After the constraint graph is built, there are two ways to solve the graph. One is to decide each vertex's longest path length from the boundary vertex, which amounts to finding the shortest path algorithm in a directed graph with arc weight negated. Most of early compaction tools are based on this approach. However, the implied compaction goal of this approach is to minimize the layout area. In order to accommodate more compaction goals such as minimization of power or perturbation, the constraint graph is solved by dumping constraints to linear programming solver and obtaining the result under the user specified compaction goal.

The *minimum perturbation objective function* proposed in [10] was the first work that departed from the traditional area minimization optimization goal and argued the importance of rewarding geometric similarity between the migrated layout and the original layout. However, the quantitative measure that they develop for geometric similarity is asymmetrical and penalizes both right edges in the X direction and upper edges in the Y direction. In our migration

tool, we slightly modify the minimum perturbation objective function by minimizing the size change of each rectangle in the layout.

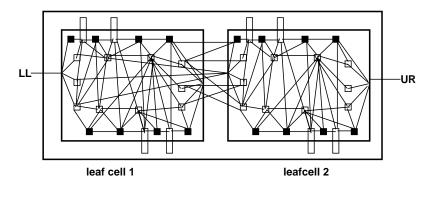

## 2.3 Hierarchical Layout Compaction

The majority of the hierarchical layout compactors reported in literature focus on solving the pitch matching problem, which means that certain elements among different cells must match in size and position when cells are abutted. The method described in [11] first compacts leaf-cells and then locates the abutting ports to fixed grids. After that, the compacted cells are assembled and compacted at the higher level of hierarchy as shown in Figure 2.6 [9]. In this method, routing is needed to guarantee the connection.

Figure 2.6: The constraint graph for a cell to be pitch matched.

The pitch matching method introduced in [15] matches the abutting ports by directly adding abutting constraints between cells to the constraint graph. This method assumes that hierarchical layout is given. The constraints for all leafcells have to be dumped to linear programming solver so that port matching constraints can be solved. As the number of leafcells increases, this method will be limited by the capability of linear programming solver.

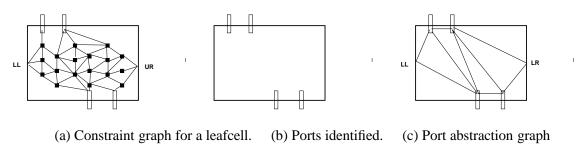

A powerful pitch matching algorithm is reported in [13] based on port abstraction method. The port abstraction graph can be considered as a simplification of the constraint graph for each

cell, where constraints unrelated to the ports are removed as shown in Figure 2.7. The longest path between ports are computed and the port locations of each cell are then solved by solving the combined port abstraction graph of the circuit that uses the cell to be migrated. The result is then set as constraints to drive the migration of each leaf cell. The port abstraction method is very powerful in solving pitch matching problem. However, the main problem related is that the port position is decided by the longest path algorithm, which means that the ports will be placed as close as possible to each other. It implies that the total layout area will be minimized and it is not suitable to handle other objective functions. So our migration tool takes another approach called *Dual-pass strategy* that can decide port locations with considerations of both design rules and the objective function.

Figure 2.7: Port abstraction method.

### 2.4 Other Developments

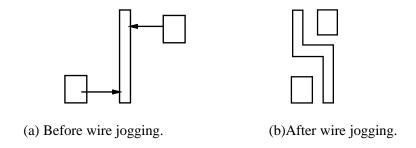

The automatic jogging wires and wire length minimization are the two problems that have been investigated together with compaction problem. One of the first approach for wire jogging was presented in [18]. In this approach, the wire is bended at the "torque" points on a straight wire as shown in Figure 2.8.

The usage of wire jogging is limited because it could reduce the layout size in one direction but potentially, increasing the size in another direction [9]. In our project, we introduce the geometric closeness objective function to keep the original shape of the layout to a maximum extent. The wire jogging will introduce big changes to the layout, therefore, it is not considered

Figure 2.8: Wire jogging.

in our tool.

Another effort has been spent on minimizing the wire length on critical path. This is achieved by uniformly distributing spaces among circuit elements [18] or by "pulling" circuit elements back so that the length of connection wire is not increased drastically. As our migration tool could minimize the wire length by migrating layouts under minimum area objective function, we will not include this step in our tool.

As fabrication technology in the IC industry advances, some foundries are demanding the use of more complicated rules such as conditional design rules. For example, some conditional rules require that the spacing of two edges depend on the context in which edges are situated [4]. Finding the optimal solution under contditional rule has been proven to be NP-complete. However, some heuristic method has been reported that can solve compaction under simplified conditional rules: bridge rules [4]. This algorithm has some potential applications. On the other hand, solving the conditional rule depends on the correct design rule modelling. The edge rule system we use currently has accomadated conditional rules. So our tool does not taken this issue into account.

All the compaction methods discussed above are one-dimentional compaction. Several techniques have been proposed for simulatneous two-dimentional compaction [17] [26]. The methodologies mainly include two steps. First, the compact layouts without respecting minimum distance requirements. Then select each pair of elements and add spacing constraints that could be in the X direction or in the Y direction. Compared to one-dimentional compaction, two-dimentional compaction methodology has not been widely used. The main reason is that

two-dimentional compaction is proven to be NP-complete [17] [6]. The effctiveness of these heuristic algorithms needs to be further verified. And with the X compaction and Y compaction performed together, the layouts have more freedom for topology changes. Therefore, we still adopt the traditional one-dimentional compaction appraach for our migration tool.

## Chapter 3

## **Migration Engine**

## 3.1 Background

Layout and design rules are the objects that a migration tool processes. This section reviews the layout representation methodology and design rule modeling methodology. In the text that follows, we use the *formal algorithm notation* (FAN) to state definitions and describe algorithms [27]. FAN relies on a type system, where each type is presented by a set, to present the algorithm in a formal, precise manner. For example, we use the notation  $\langle \rangle^A$  to represent the power set of A, therefore, any value of type  $\langle \rangle^A$  will be a set of values of type A. Readers are expected to find this notation very similar to any strongly-typed programming languages and hence be translated into implementation.

### 3.1.1 Layout Representation

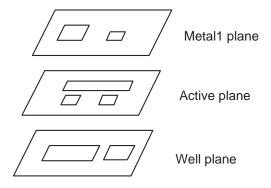

A layout is a drawing of a set of polygons, each associated with a different layer, such as metal, poly, or diffusion, given by the fabrication technology. For simplification, polygons are often constrained to be rectangular, called *Manhattan layout*, and polygons related by their layers are organized in logical layers, called *planes*, as shown in Figure 3.1.

### 3.1.2 Corner stitching

Figure 3.1: A layout is composed of several planes.

Choosing a good layout representation is a key to producing fast geometric operations for migration tools. In this project, a data structure called *corner stitching* which can provide fast operations such as neighbor finding is used to represent the layout [19]. A brief discussion of the corner stitching algorithm is given in this section.

We first define **Technology** and the data structure to represent it.

**Definition 1 Technology** defines the information that are related to the fabrication technology. It includes **LayerType** which is a set of mask types, **PlaneType** which is a set of plane types and a mapping from LayerType to PlaneType **PlaneMap** which is used to identify the plane that a polygon with certain mask type can stay on and **DesignRuleBase** which is used to store all the design rules specified by fabrication technology and will be discussed in more detail in Section 3.1.4.

```

Technology = \mathbf{tuple} \left\{ \\ LayerType = \left\{ space, \, ndiff, \, pdiff, \, poly, \, m1, \, m2, 2 \, \dots \right\}; \\ PlaneType = \left\{ active, \, m1, \, m2, \, poly, \, \dots \right\}; \\ PlaneMap : LayerType \mapsto PlaneType; \\ DesignRuleBase : LayerType \times LayerType \mapsto \left\langle \right\rangle^{EdgeRule}; \\ \end{cases}

6

```

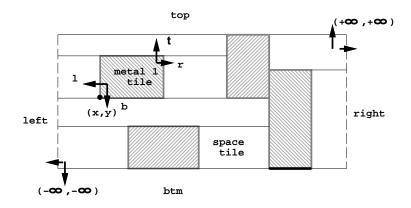

Each polygon, also called a *tile*, is associated with a specific mask type as defined in Line 2. Tiles are linked by four pointers called *corner stitches*. Figure 3.2 gives an example of the tile structure in *metal1* plane. The pointer l at the lower left corner of a tile points to the direct left neighbor at the lower left corner of the tile. Pointer b at the lower left corner of a tile points to the direct bottom neighbor at the lower left corner of the tile. Similarly, pointers t and t at the upper right corner of a tile point to the upper neighbor and right neighbor of the tile, respectively. The coordinate  $\{x,y\}$  is the position of the tile's lower left corner. The tile data structure is given in Definition 2. With the data structure for tile, the geometrical and physical characteristics of each tile can be fully determined from **Tile**. For example, given a tile u, the upper right coordinate, (u.r.x, u.t.y), is decided by its right neighbor u.r and top neighbor u.t because the X coordinate of tile u's right edge is also the X coordinate of the left edge of right neighbor u.t and Y coordinate of tile u's upper edge is also the Y coordinate of lower edge of top neighbor u.t. Through tile u's mask type u.type, the plane that u stays on can be obtained from function PlaneMap(u.type). Thus the location and shape of each tile can be fully decided from Tile data structure.

#### **Definition 2 Tile**

Figure 3.2: The tile structure in metal1 plane

```

Tile = tuple {

8

type

: LayerType;

9

l, b, t, r

: Tile;

10

x, y

: Z;

11

}

12

```

Each plane is associated with a plane type as defined in Definition 1. A plane is composed of an ordered set of tiles. It extends from negative infinity to positive infinity. Four pseudo tiles *top*, *btm*, *left*, *right* are located at four boundaries of a layout. Any of these four pseudo tiles can be used as the starting tile for traversing a layout. The algorithms for traversing layout will be discussed in Section 3.1.3. The data structure for a plane is given in Definition 3.

#### **Definition 3 Plane**

```

Plane = tuple {

13

type

: PlaneType;

14

:\langle\rangle^{Tile}:

15

tiles

top, btm

: Tile;

16

left, right

: Tile;

17

}

18

```

Other than tiles and planes, layout designers tend to attach labels to certain signals. The data structure for label is given in Definition 4.

#### **Definition 4 Label**

```

Label = tuple {

19

name

: string;

20

tile

: Tile;

21

}

22

```

With the definitions for tile and plane, a layout can be formulated as a structure which includes a mapping from PlaneType to Plane and a set of labels as shown in Definition 5.

#### **Definition 5 Layout**

```

Layout = tuple {23planes: PlaneType \mapsto Plane;24labels: \langle \rangle Label;25}26

```

### 3.1.3 Algorithms

There are many algorithms used for processing tiles using corner stitching representation methodology defined in the previous section, such as neighbor tile finding, locating and enumerating tiles, searching area, etc [19]. This section gives a discussion of three algorithms often used in our migration engine.

**Algorithm 1** Find all the right neighbor tiles of given a tile s.

```

rightNeighborFind = func(

27

pl: Plane,

28

s: Tile

29

):[]^{Tile} {

30

var nbr : Tile;

31

\mathbf{var} \ nbrSet : []^{Tile};

32

33

nbrSet = \emptyset;

34

35

nbr = ti.r;

if( nbr \neq pl.right )

36

do {

37

nbrSet = nbrSet cup \{nbr\};

38

nbr = nbr.b;

39

} while (nbr.y > s.y)

40

return nbrSet ;

41

}

42

```

#### Example 1

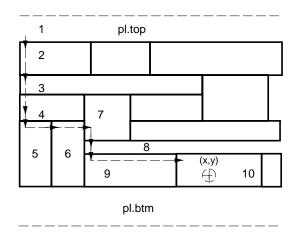

Figure 3.3 shows an example to demonstrate this algorithm. The searching process is as follows:

- 1. First, it visits the top right neighbor of tile s through its  $\mathbf{r}$  pointer. If s.r is not the right pseudo tile, add it into the neighbor tiles set.

- 2. Check if the bottom edge of the neighbor tile is still above the bottom edge of tile s. If this is true, move downward until it finds a tile whole bottom edge is lower than that of s.

- 3. Otherwise, return the neighbor tiles set.

Figure 3.3: The process to find right neighor tiles.

**Algorithm 2** Find the tile that contains a given (x,y) location on a given plane.

```

searchTiles = func(

43

layout: Layout,

44

pl: Plane,

45

x: \mathcal{Z},

46

y: \mathcal{Z}

47

): Tile {

48

var ti : Tile;

49

50

ti = pl.top;

51

if(y < ti.y)

52

do ti = ti.b; while(y < ti.y);

53

else return ti;

54

if(y < pl.btm.u.y) return ti;

55

if(x > ti.r.x) do {

56

57

ti = ti.r;

while(ti.y > y) ti = ti.b;

58

} while(x > ti.r.x)

59

60

return ti;

}

61

```

Here is an example to illustrate the process of finding the tile.

#### Example 2

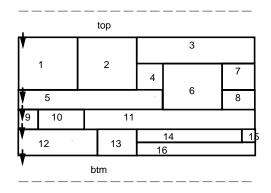

Considering a simple layout in Figure 3.4, to find a tile that contains the point (x, y), the algorithm starts from the top tile (tile 1) in the layout. The searching procedure is as follows:

1. First it checks whether y coordinate of the given point is beyond scope of the **top** tile or **btm** tile. If this is true, the tile that contains the given point is set to **top** tile or **btm** tile.

- 2. Otherwise, the search moves downward, until it finds the tile whose vertical range covers the desired point (For example, this occurs when tile 5 is found).

- 3. Select the right neighbor whose horizontal range contains the desired point and then trace rightward (For example, tile 6 has three neighbors: tile 7, tile 8 and tile 9. The lower bound of tile 7 and tile 8 is upper to the desired point, so it traces downward until tile 9 is found and from tile 9, trace goes rightward). The rightward trace keeps on until it finds the tile that contains the point (tile 10).

Figure 3.4: The process to locate the tile that contains a given point

**Algorithm 3** Enumerate all tiles on a given plane. In this algorithm, each tile is visited only after all tiles above it and to its left have been visited.

```

enumerateTiles = func(pl:Plane):[]^{Tile} {

62

var tiles : []^{Tile};

63

var start : Tile;

64

65

tiles = \emptyset;

66

start = pl.top.b;

67

while(start.b \neq pl.btm) {

68

tiles = eachTile( pl,tiles, start );

69

start = start.b;

70

71

return tiles;

72

73

74

eachTile = func(

75

pl: Plane, tiles: []^{Tile}, ti: Tile

76

):[]^{Tile} {

77

var right : Tile;

78

79

tiles = tiles \cup \{ti\};

80

if( ti.r == NULL ); return tiles;

81

else {

82

right = ti.r;

83

while(right.y >= ti.y) {

84

tiles = eachTile( pl, tiles, right);

85

right = right.b;

86

}

87

88

89

90

```

#### Example 3

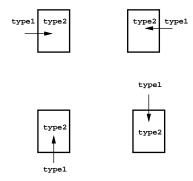

Figure 3.5 illustrates the algorithm. The process is as follows:

- 1. Start from the left most neighbor of the top tile at its bottom side in a given plane. Then step down through all the tiles at the left most side of the plane (the tiles with arrows inside in the figure).

- 2. For each tile in step 1, enumerate it recursively using the **eachTile** procedure given in lines from 1) to 4).

- 1) Enumerate the tile.

- 2) If the **r** stitch of the tile points to NULL, return from **eachTile** procedure (for example, when tile 2 is the current tile, tile 3 is its neighbor. But as tile 3 doesn't have any right neighbor, the procedure returns to the state when tile 2 is the current tile).

- 3) Otherwise, visit all the tiles that touch the right side of the current tile (for example, when tile 13 is the current tile, visit tile 14 and tile 16).

- 4) For each of these neighbors, if the **l** stitch points to the current tile, then call **eachTile** procedure to enumerate the neighbor recursively ( for example, this occurs when tile 1 is the current tile and tile 2 is the neighbor).

- 3. The enumeration algorithm stops when it comes to the bottom tile of the plane.

### 3.1.4 Design Rule Modeling

The second input to migration tool is design rules. For IC designers, design rules are usually provided by manufacturers in the technology file. Each rule is explained by a simple English sentence with graphs illustrations to show the conditions in which the rule is applied. However, in order to be codified for use by migration tool, design rules need to be specified in an accessible and unambiguous format. There are two major methodologies for representing design

Figure 3.5: Tile enumeration.

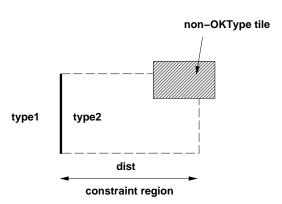

rules. One is called *mask-based* design rule which is the basis of commercial design rule check package *Dracula* [2]; the other is called *edge-based* design rule model which is the basis of layout edit tool Magic [2]. In this project, the *edge-based* design rule model is used because of its ability to translate the high level design rules such as minimum spacing rule, minimum width rule, etc, into a set of edge rules and thus we can represent the design rules as constraints between individual edges. This section will briefly introduce this model and its data structure. For detailed discussion, please refer to [24].

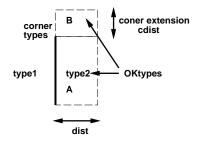

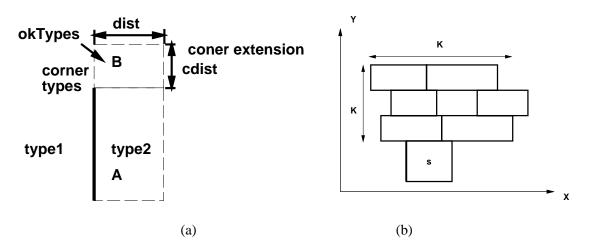

Figure 3.6: Each edge rule can be applied in any of the four directions.

The edge rule is applied on an edge between two tiles of different LayerType in any of four directions as shown by arrows in Figure 3.6. Without loss of generality, in the following discussion, we assume that the edge rule is applied towards the east. A distance *dist* and certain mask layers called *okTypes* area are specified so that only tiles of *okTypes* are permitted within

Figure 3.7: An example of edge rule.

the area A called *constraint region* as shown in Figure 3.7. In the corner region B, if the tile of type *cornerTypes* is just above and on the left of the edge, only *okTypes* tiles are allowed in area B. For simplicity, we call those tiles whose mask types do not belong to *okTypes forbidden tiles* for each edge rule. The constraint region can be on the same plane as the plane that tiles of type1 and type2 stay on, or any different planes as indicated in each edge rule.

The following data structure is used for modeling edge rules in the migration tool.

#### Definition 6 Edge rule.

```

EdgeRule = tuple {

91

:\langle\rangle^{LayerType};

okTypes

92

93

dist

:\langle\rangle^{LayerType};

cornerTypes

94

: Z;

95

cdist

: \langle \rangle^{\{area, rect, \dots\}};

flag

96

: PlaneType;

97

plane

}

98

```

Given a pair of LayerType, a set of edge rules can be accessed through *DesignRuleBase* defined in *Technology*.

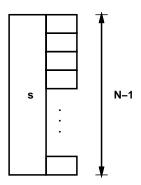

# 3.2 Migration Engine

As the layout is composed of a set of tiles, the migration engine can generate a new layout by determining new positions of horizontal and vertical edges of all tiles. It employs the traditional 1-D compaction strategy by first migrating along the X direction, i.e. determining positions of vertical edges, and then the Y direction. Without loss of generality, in the discussion that follows, we assume migration in the X direction only.

The basic strategy for migration is to abstract all the requirements or constraints among all the edges in a layout, such as design rules and other practical consideration. And then with respect to all these constraints, new edge positions are decided under certain optimization goal. With the corner stitching data structure discussed in Chapter 2, tile shapes and design rules are specified in the Mead and Conway's  $\lambda$  based methodology [16], which means that the positions of tiles are all specified in terms of  $\lambda$ . Take the layout in Figure 3.8, tiles are all aligned in grids whose minimum spacing is  $1\lambda$ , which implies that the coordinates of all edges are integers. At the same time, design rules are specified in terms of  $\lambda$  also. And all design rules can be expressed as inequalities when they are applied to the layout. For example, suppose the minimum width requirement for tile 1 is  $4\lambda$  in Figure 3.8 and this rule can be translated into an inequality as:

$$x_2 - x_1 \ge 4 \tag{3.1}$$

Thus, the layout migration problem can be formulated as an integer linear programming (ILP) problem:

$$minimize \qquad o^T x$$

$$subject\ to \qquad Ax \ge b$$

$$x \ge 0$$

Here x is a vector of variables to be determined, and in the simplest case would just be

Figure 3.8: Tiles are aligned in grids

coordinates for all vertical edges. In this project, x is a vector of coordinates for all tiles' left vertical edges. Vectors o represent the coefficients of x in the objective function of optimization. Each row of array A represents coefficients of x in an inequality. We call this type of migration as constraint-based migration.

Suppose we want to migrate the layout in Figure 3.8 so that the new layout does not have design rule violations and the layout area is minimum. For simplicity, we only consider the minimum width rule and minimum spacing rule for tile 1 and tile 2. The minimum width for tile 1 and tile is  $4\lambda$  and minimum distance between tile 1 and tile 2 is  $3\lambda$ . This problem is formulated as:

minimize

$$x_4 - x_1$$

$$subject to \quad x_2 - x_1 \ge 4$$

$$x_4 - x_3 \ge 4$$

$$x_3 - x_2 \ge 3$$

$$x_1 \ge 0$$

$$x_2 \ge 0$$

$$x_3 \ge 0$$

$$x_4 \ge 0$$

After solving this ILP problem, we can get the value for each x, and new positions of each

edge can be obtained as shown in Figure 3.9.

Figure 3.9: Each tile has new position and shape after migration with no design rule violations.

Section 3.3 will discuss how to translate the design rules requirements into inequalities in 3.2, so called constraints, so that the generated layout is design rule clean. In addition, three goals to optimize the migrated layout are compared in section 3.4 and a brief discussion of ILP solver is also provided at the end of this chapter.

# 3.3 Design Rule Constraint Generation

The design rule constraint generation is used to generate the distance requirements of every pair of edges according to design rules so that the migrated layout does not have design rule violations. This section will discuss how to generate these constraints according to the edge rules specified by the technology.

# 3.3.1 Design Rule Checking

The design rule constraint generation process is very similar to design rule checking. Before the discussion of design rule constraint generation, we can first look at how design rule checking works.

To check a region, the design rule checker first searches all tiles in the plane. For each tile, the checker examines all the neighbors along one side. As the tile may have more than

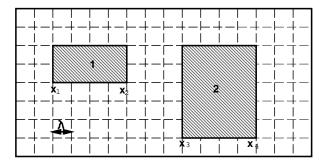

one neighbor that are of different mask types. A design rule checker divides the tile's side into several edges that has only one with one material on each side. When processing the edge, checker uses the mask types of tiles at each side of the edge as the index into the design rule database to find the edge rule r: EdgeRule that can be applied on that edge. Then, design rule checker searches within the constraint region for tiles whose mask type don't belong to r.okTypes as shown in Figure 3.10. The plane that a constraint region stays on can be on either the plane that the edge being processed stays on or another plane which is decided by r.plane. In the next section, we will look at the  $IntraPlane\ checking\ process$  where the constraint region stays on the same plane as the tile processed. Section 3.3.5 will discuss the  $InterPlanechecking\ process$  where checker needs to jump to another plane to look for forbidden tiles.

Figure 3.10: Design rule checker looks for non-OKType tiles within constraint region.

## 3.3.2 IntraPlane Design Rule Constraint Generation

Design rule constraint generation can take similar procedure as design rule checking discussed in previous section, except that the searching region should go beyond constraint region specified by design rules. The reason is that migration assumes that every tile has the potential to move, which means those forbidden tiles that are not inside constraint region in the original layout may move into constraint region after migration. An intuitive way to avoid missing con-

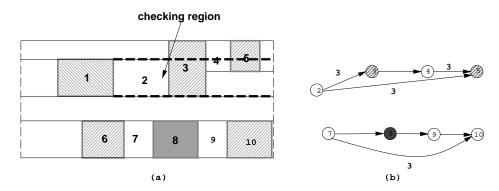

straints is to extend the constraint region to the boundary of layout as the checking region in Figure 3.11(a) and generate constraints between all necessary pair of edges. Take poly spacing rule as an example, the TSMC 0.25um technology specifies that the spacing of poly should be greater than  $3\lambda$ , which can be translated into edge rule as the following:

**edge** poly  $\overline{poly}$  3  $\overline{poly}$  3

Figure 3.11: (a) An example layout in active plane. The shaded rectangles 1, 3, 5, 6 and 10 represent poly tiles. Rectangle 8 is diffusion tile. Other rectangles are all space tiles. (b) The constraint graph generated from poly spacing rule.

Given a simple layout as Figure 3.11(a), according to this rule, four constraints need to be generated to guarantee enough spacing between poly when processing the edge between tile 1 and tile 2 (corner region checking is not considered at this moment). They are:

- $x_3 x_2 \ge 3$  The left edge of tile 3 should be at least  $3\lambda$  away from left edge of tile 2.

- $x_5 x_2 \ge 3$  The left edge of tile 5 should be at least  $3\lambda$  away from left edge of tile 2.

- $x_5 x_3 \ge 3$  The left edge of tile 5 should be at least  $3\lambda$  away from left edge of tile 3.

- $x_{10} x_7 \ge 3$  The left edge of tile 10 should be at least  $3\lambda$  away from left edge of tile 7.

These constraints can be visualized using a directed graph  $G = \langle V, E \rangle$  as shown in Figure 3.11(b). Each vertex represents the X coordinate of a tile's left edge. For each inequality of the form  $x_j - x_i \ge d_{ij}$ , there is an arc  $\langle v_i, v_j \rangle$  with weight  $d_{ij}$ .

Note that with constraint-based migration methodology, the width and height of tiles may be changed after migration in order to satisfy the constraints. However, migration must maintain that the given circuit topology keep the same functionality of the circuit, i.e., the corner stitching representation of the layout is kept unchanged. So after migration, the four pointers of each tile must point to the same tiles as in the old layout. The relative position of tiles are not changed. For example, the tile 5 in Figure 3.11 is on the right side of tile 3 in the old layout and after migration tile 5 cannot move to the left side of tile 3. Therefore, the arc  $\langle v_2, v_5 \rangle$  in Figure 3.11(b) is redundant because the tile 5 is always on the right side of tile 3 and the distance constraint between left edge of tile 2 and tile 3 ( arc  $\langle v_2, v_3 \rangle$  ) guarantees that the distance between left edge of tile 2 and tile 5 cannot be less than  $3\lambda$ . In other words, if an edge of forbidden tile (tile 5) stays behind another forbidden tile (tile 3), it will not generate constraint between the edge that is being processed and the edge in the "shadow" of forbidden tiles.

Another redundant arc in Figure 3.11(b) is arc  $\langle v_7, v_{10} \rangle$ . As discussed before, the tile structure will not be changed after migration, which implies that tiles cannot be eliminated after migration. We can assume that the minimum tile width should be greater than or equal to  $1\lambda$ . So the minimum separation between the left edge of tile 7 and tile 10 should be greater or equal than the sum of minimum width requirement of tile 7, 8 and 9, which is greater than or equal to the minimum spacing  $3\lambda$ . This makes the arc  $\langle v_7, v_{10} \rangle$  redundant for migration.

A new design rule constraint generation method *Depth-K searching* algorithm is proposed in this project which greatly reduces the checking region and reduces the redundant constraints. A detailed discussion of this algorithm follows.

# 3.3.3 The Depth-K searching algorithm

To gain more insight into the problem, we first build a graph *shadowing neighborhood graph* that captures the neighboring relation. As we can observe from Figure 3.11 that constraints should be generated only for tiles that overlap with the checking edge vertically, a *shadowing neighborhood graph* defined in Definition 7 is used to limit the searching space.

**Definition 7** Given a tile called source tile in a plane, its shadowing neighborhood graph  $N = \langle V, E^N \rangle$  is a directed graph whose vertices correspond to the tiles that overlap with the source tile in the Y direction, and an edge  $\langle u, v \rangle \in E^N$  iff tile u and v share a common edge.

While the shadowing neighborhood graph is effective limiting the search space in the Y direction, we propose a new strategy to further limit the searching space in X direction. We observe that as we explore along the X direction, each tile has a minimum width requirement dictated by the design rule or by topology keeping requirement. This can be summed up along the path and be used as the bottom bound estimate of the distance between the source tile and the current tile. Let's assume D is the maximum dist value among all the edge rules. If the lower bound exceeds the constraint distance D, further exploration of the current tile can be stopped.

Figure 3.12: (a) A fraction of a layout plane. Tile 1 is the source tile that is being processed for edge rule constraint generation. (b) Depth-K shadowing neighborhood graph for tile 1.

**Example 4** Consider the layout example in Figure 3.12 (a). The shadow is indicated by the dashed line. A fraction of the neighborhood graph is shown in Figure 3.12(b), where each tile is labeled with its minimum width requirement of d1, d2 etc. Suppose the constraint distance is D, and  $d1 + d2 + d3 \le D$ ,  $d1 + d2 + d3 + d4 \ge D$ , then tile 10 and tile 11 will be pruned from the searching space.

As such, it is guaranteed that there exists an upper bound of the depth we have to search. We denote the maximum number of depths as K, which is totally decided by the design rules. Given K, the definition of Depth-K shadowing neighborhood graph is given in Definition 8 and Algorithm 4 shows how it is built.

**Definition 8** Given a shadowing neighborhood graph  $N = \langle V, E^N \rangle$ , its **Depth-K shadowing** neighborhood graph is a directed graph  $\overline{N} = \langle V, \overline{E^N} \rangle$  such that  $\langle u, v \rangle \in \overline{E^N}$  iff  $\exists p \in u \leadsto v.|p| \leq K$  and  $[u.y, u.t.y] \cap [v.y, v.t.y] \neq \varnothing$ .

**Algorithm 4** *Depth-K searching algorithm.*

```

input: s : Tile;

99

pl: Plane;

100

r: EdgeRule;

101

output: \overline{N} = \langle V, \overline{E^N} \rangle;

102

func depthKShadowingClosure() {

103

V = \{s\};

104

\overline{E^N} = \varnothing:

105

forall(u \in rightNeighobrFind(pl, s)) {

106

explore(s, u, 1);

107

}

108

}

109

func explore(u, v, depth) {

110

if( [s.y, s.t.y] \cap [v.y, v.t.y] = \emptyset \lor depth + + > K)

111

112

return;

\overline{E^N} = \overline{E^N} \cup \langle u, v \rangle;

113

V = V \cup \{v\};

114

if(v.type \notin r.okType)

115

return;

116

forall(w \in rightNeighborFind(pl, v))

117

explore(v, w, depth);

118

}

119

```

After Depth-K shadowing neighborhood graph is built, design rule constraints for source tile s can be added to constraint graph  $G=\langle V,E\rangle$  by traversing its Depth-K shadowing neighborhood graph  $\overline{N}=\langle V,\overline{E^N}\rangle$ . Algorithm 5 shows how the design rule constraint are generated when given the Depth-K shadowing neighborhood graph.

#### **Algorithm 5** *Edge rule constraint generation.*

```

input: s : Tile;

120

\overline{N} = \langle V, \overline{E^N} \rangle;

121

R: EdgeRule;

122

output: G = \langle V, E \rangle;

123

func addEdgeConstraints() {

124

forall(u \in V)

125

if( u.type \notin R.OKType ) {

126

E = E \cup \langle s, u \rangle;

127

weight(\langle s, u \rangle) = R.dist;

128

}

129

}

130

131

```

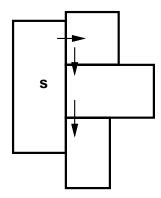

To analyze the complexity of Depth-K searching algorithm, we assume that the total number of tiles in a layout is N. For any source tile s, the best case for the Depth-K searching algorithm is for a row of tiles to sit beside s as shown in Figure 3.13. In this case, this algorithm would process K tiles for s. The worst case is shown in Figure 3.14 where s has N-1 neighbors and N-1 tiles need to be processed for s. From the experimental result given in Section 5.2.1, the expected time complexity of the whole design rule constraint generation process is  $O(N^{1.4})$ , which includes both time cost for tile enumeration algorithm and Depth-K searching algorithm.

Figure 3.13: The best case for Depth-K searching algorithm

Figure 3.14: The maximum number of tiles to be visited for tile s

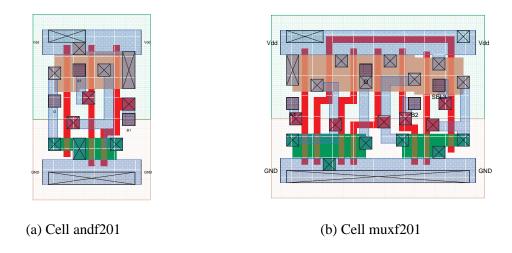

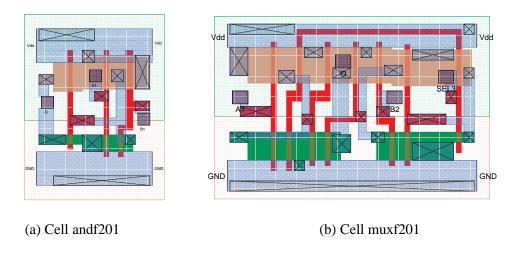

Figure 3.15 and 3.16 gives an example of IntraPlane design rule constraints generated for leaf cell muxf201. The constraint graph is visualized in Figure 3.16.

Figure 3.15: A leaf cell muxf201.

# **3.3.4** Corner checking and Interpass constraint generation

In addition to the design rule constraints in the constraint region, edge rule also specifies the corner region of an edge that needs to be examined as shown in Figure 3.17(a). The shape of corner region is a  $cdist \times dist$  rectangle. As every tile has the potential to move, the constraint generation should also search beyond the corner constraint region. The Depth-K searching

Figure 3.16: The constraint graph for IntraPlane constraints.

algorithm can be applied to constraint generation in the corner region also. The only difference is that in the Y direction, the searching should proceed to the  $K^{th}$  neighbor tile as shown in Figure 3.17(b). As this algorithm is very similar to the Depth-K searching algorithm, we will not give a detailed description of it.

Figure 3.17: Corner constraint region checking

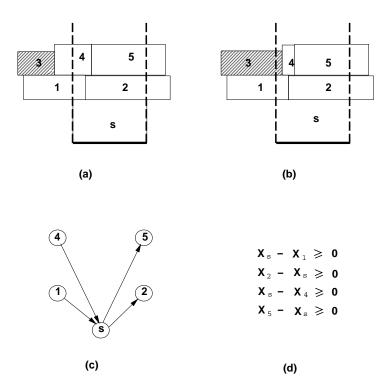

As we employ the traditional 1-D migration, X migration and Y migration are independent of each other, which may give rise to missing constraints for both X migration and Y migration.

**Example 5** Considering the layout in Figure 3.18, let's suppose that tile 3 is located above the constraint searching region and it is not included in the Depth-K shadowing neighborhood graph. So, during X direction migration no constraint is generated between left edge of tile 1 and left edge of tile 3. After X direction migration and Y direction migration, it is possible that tile 3 moves into area A. A design rule violation may occur if the distance between left edge of tile 3 and left edge of tile 1 is less than the distance requirement from edge rule.

Figure 3.18: (a) In the old layout, tile 3 doesn't overlap with tile s in X direction. (b) After X direction migration and Y direction migration, tile 3 moves into shadow area of tile 1. (c) Interpass Constraint graph for tile s (d) Interpass constraints for tile s.

To solve this problem, additional constraints called *interpass constraints*, need to be generated to prevent the arbitrary movement of tiles during X and Y direction migration. Take the

layout in Figure 3.18(a) for example, given a source tile s, for each tile that overlaps the left boundary of tile s in the X direction such as tile 1 and tile 4, we generate constraints between the left edge of tile s and both vertical edges of tile 1 and tile 4 to guarantee that the left edge of s stays within tile 1 and tile 4 as illustrated in Figure 3.18(c,d). With interpass constraints, those tiles that do not overlap source tile in the original layout will always be kept away from checking area, thus no new design rule violations will occur after migration.

#### **Algorithm 6** Interpass Constraint Generation

```

input: s : Tile;

132

\overline{N} = \langle V, \overline{E^N} \rangle:

133

output: G = \langle V, E \rangle;

134

func InterpassConstraints() {

135

forall(u \in V)

136

if( s.x \in [u.x, u.r.x] ) {

137

E = E \cup \langle u, s \rangle;

138

weight(\langle u, s \rangle) = 0;

139

E = E \cup \langle s, u.r \rangle;

140

weight(\langle s, u.r \rangle) = 0;

141

}

142

}

143

```

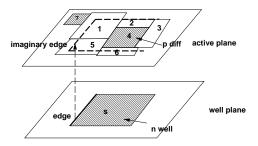

## 3.3.5 InterPlane Constraint generation

Other than the constraints between tiles on the same plane, edge rules also specify the distance requirements between tiles on different planes, indicated by the value of *plane* in each edge rule. For example, the minimum spacing requirement between N-well and pdiffusion in TSMC  $0.25\mu m$  technology is  $6\lambda$ . However, Well tiles and active tiles are in different planes in the

corner stitching layout representation as shown in Figure 3.21. So the value of *plane* in this edge rule given in is set to *active* as shown below:

edge

$$space$$

$N-well$   $\overline{pdiff}$  6  $\overline{pdiff}$  6 active

Figure 3.19: N-well tile stays on well plane while diffusion tile stays on active plane.

The Depth-K searching algorithm is modified slightly to be applied for interplane constraint generation. For intraplane constraint generation, the Depth-K shadowing neighborhood graph is built on the same plane as the plane that the source tile s stays on and the constraint region starts from the edge of tile s. However, for interplane constraint generation, the Depth-K shadowing neighborhood graph is built on checking plane as indicated in the edge rule. We first map the edge being processed to an imaginary edge on the checking plane as shown in Figure 3.21. The imaginary edge has exactly the same length and location as the edge being processed. Then the Depth-K shadowing neighborhood graph can be built with Depth-K searching algorithm on the checking plane. The Depth-K shadowing neighborhood graph for layout in Figure 3.21 and the corresponding interplane edge rule constraint are given in Figure 3.20.

However, for interplane edge rules, the constraints generated above are not enough to guarantee that validity of the migrated layout. The main reason is that the movement of tiles in different plane are independent if no further constraints are generated, which may cause design rule violations in the migrated layout. For example, if no constraints between the left edge of tile 1 in Figure 3.21 and that of source tile s, the tile 7 which is also a P-diffusion tile may move to the right of edge and the distance may be within  $6\lambda$ , which will cause design rule

Figure 3.20: (a) The Depth-K shadowing neighborhood graph for interplane edge rule (b) InterPlane edge rule constraint between source tile *s* and tile 3.

errors. Also, tile 4 may also move outside of the constraint region which makes constraints between tile s and tile 3 unnecessary. So two more types of constraints need to be generated with the interplane design rule.

• InterPass constraints in the X direction for interPlane edge rule. This set of constraints is used to guarantee that the imaginary edge of source tile s still overlap's with the same tiles in the old layout. Given the layout in Figure 3.21, we will generate constraints:

$$x_s - x_1 \ge 0$$

$x_s - x_2 \le 0$

$x_s - x_5 \ge 0$   $x_s - x_4 \le 0$

$x_s - x_6 \le 0$  (3.2)

With these constraints, the relative position in the X direction of those tiles in different planes will be kept unchanged. Therefore, forbidden tiles such as tile 7 on the left side of the imaginary edge will not move to the right side of it after migration and vice versa. Otherwise, the new layout may have design rule violations between the source tile and forbidden tile that were not considered in Depth-K shadowing neighborhood graph.

• InterPass constraints in the Y direction for interPlane edge rule. It is very similar to interpass constraints for intraPlane edge rule, except that source tile is in different plane.

For the layout in Figure 3.21, we need to generate constraints for the bottom edge of tile s to guarantee that after migration, the bottom edge of tile s still overlaps with tiles that overlapped with it in the original layout:

$$y_s - y_5 \ge 0 \qquad y_s - y_1 \le 0$$

$$y_s - y_6 \ge 0 \qquad y_s - y_4 \le 0$$

The constraints for top edge of tile s can be built in the same way. With this set of constraints, the forbidden tiles in the checking plane will still stay within the constraint region after migration. Other forbidden tiles that were above or below the constraint region will be kept away from the constraint region so that no new violation will occur after migration.

Figure 3.21 shows a real example of InterPlane constraints generated for leaf cell muxf201 given in Figure 3.15.

Figure 3.21: InterPlane constraints generated for cell muxf201.

#### 3.3.6 Connect Constraints Generation

Connect constraints are generated to guarantee the correct presentation of contact tiles after migration. As we know from Chapter 2, corner-stitching partitions the mask layers into separate planes. Layers that overlap may cause electrical constructs to be partitioned into the same plane. Those layers that overlap with little electrical significance will be partitioned into different planes [22]. For example, polysilicon, diffusion, and their overlaps (transistors) are stored in **active** plane, while metal1 that does not interact with these layers is stored in a different plane, **metal1** plane.

However, because the **contact** mask type connects layers in different planes, it is a special case. It has to be represented in all planes that it connects. In the technology file, contact is specified in a Contact section with specialized syntax. An example of polycontact is shown below:

| contact  |      |        |

|----------|------|--------|

| pcontact | poly | metal1 |

| end      |      |        |

The contact declaration begins with a contact type called *base type*. In this example, pcontact is a base type for polycontact. The remainder of this declaration is a list of non-contact mask types (poly and metal1 in the example) that are connected by this contact. These types are referred to as *component* type of the contact. The home plane of the first component type will be the home plane for contact and contact also has an *image* tile type on the planes where other component type tiles stay. For example, pcontact's home plane is active plane which is also the home plane for poly. A pcontact has a image tile type *pdcontact/metal1* that is stored in metal1 plane as illustrated in Figure 3.22.

Figure 3.22: A contact has different tile types on the planes it connects. The poly contact in this figure has **pcontact** tile (tile 1) on active plane and **pcontact/metal1** tile (tile 2) on metal1 plane.

Although a contact has two tile copies using the corner stitching representation, the contact still represents **one** via hole in physics. So, the base tile and image tile of a contact should have exactly the same shape and stay at the same location on the component planes. Given a layout for migration, the corner stitching data structure itself has no mechanism to grantee this requirement. Therefore, we generate four equalities called *connect constraints* for this requirement to guarantee that base type tile and image type tile of a contact are exactly the same after migration. For example, for the poly contact in Figure 3.22, we will generate:

$$x_{1,l} = x_{2,l}$$

$$x_{1,r} = x_{2,r}$$

$$y_{1,b} = y_{2,b}$$

$$y_{1,t} = y_{2,t}$$

Figure 3.23 shows a real example of Connect constraints generated for leaf cell muxf201 given in Figure 3.15.

Figure 3.23: Connect constraints generated for cell muxf201.

# 3.4 Objective function

After constraints are generated, the migration engine needs to build an objective function according to the kind of optimization goal the user wants to achieve and dump both the constraints and objective function to the ILP solver. The new positions of each tile will be determined from the ILP solver. The performance of the migrated layout is largely influenced by the choice of objective function. In this section, we discuss three objective functions and their impacts on layout.

#### 3.4.1 Minimum area objective function

The traditional minimum layout area objective function takes the layout area as the criteria and shrinks area to a maximum extent. Given a layout in Figure 3.24, the minimum layout objective function will be formulated as:

minimize

$$x_r - x_l$$

(3.3)

Figure 3.24: Tile 1 is the leftmost tile in a layout and  $x_l$  is the X coordinate of its left edge. Tile 2 is the rightmost tile in the layout and  $x_r$  is the X coordinate of its right edge.

However, one of the disadvantages of the minimum area objective function is that this criterion tends to shrink the layout recklessly without considering layout design issues. There exist some circumstances that increasing the layout area a little bit would be beneficial to circuit performance and chip yield. For example, power lines in the layout are usually designed to be wide instead of narrow to minimize the electromigration and resistance effects. Also, layout designers tend to make space between two important signals to minimize the coupling between them. As the minimum area objective function cannot take care of these issues, we introduce the *minimum perturbation* and *geometric closeness* objective functions in the following sections.

#### 3.4.2 Minimum perturbation objective function

In order to take full advantage of the original design and make minimum changes to the migrated layout, the *Minimum perturbation* objective is proposed in [10], which is defined as:

$$minimize \sum |x - x^{old}| (3.4)$$

where x is the vector of variables that determine X coordinates of all vertical edges and  $x^{old}$  is the vector of constants that are the original X coordinates of all vertical edges in the layout. The minimum perturbation function minimizes the position changes of all edges and snaps the edges to their original positions as much as possible. However, the disadvantage of this function is that it minimizes the absolute coordinates of edges and will penalize more on the movement of edges on the right side of the layout.

**Example 6** Consider a simple layout given in Figure 3.25 with two tiles of metal2 type. Because of technology change, the minimum width requirement of tile 1 is changed from  $4\lambda$  to  $5\lambda$  and the distance requirement between tile 1 and tile 2 is changed from  $4\lambda$  to  $5\lambda$  too. Based on minimum perturbation objective function, the layout will be migrated to the one on the lower part of Figure 3.25. The right edge of tile 1 will be stretched rightward by  $1\lambda$  and left edge of tile 2 will be moved rightward by  $2\lambda$ . However, the right edge of tile 2 stays at the old position because without change of its position, its width is  $5\lambda$  which satisfies the new design rule. Otherwise, the objective function value will be greater than the one with  $x_2'$  unchanged.

It can been seen from this example that the movement of edges on the left side will add penalties on the edges on the right side if we want to preserve the original shape of tiles on the right.

Figure 3.25: The old layout and migrated layout with minimum perturbation objective function.

#### 3.4.3 Geometric closeness objective function

To remove this penalty, a new objective function, *geometric closeness* objective function is introduced which is defined as :

Minimize

$$\sum |(x_{ri} - x_{li}) - (x_{ri}^{old} - x_{li}^{old})|$$

(3.5)

Here,  $x_{ri}$  and  $x_{li}$  are the X coordinates of the right and left edges of each tile in the layout. The constants  $x_{ri}^{old}$  and  $x_{li}^{old}$  are the X coordinates of the right and left edges of the corresponding tile in the original layout. Instead of minimizing the absolute coordinate changes of edges, this function minimizes the shape changes of all tiles so that each tile change will not add penalty to other tiles.

To linearize, or to remove the absolute value computation in Equation (3.5), we use a method similar to [10] by introducing two variables  $R_i$  and  $L_i$  for each tile, such that Equation (3.6) are introduced as constraints,

$$R_{i} \geq x_{ri} - x_{li}$$

$$R_{i} \geq x_{ri}^{old} - x_{li}^{old}$$

$$L_{i} \leq x_{ri} - x_{li}$$

$$L_{i} \leq x_{ri}^{old} - x_{li}^{old}$$

$$(3.6)$$

and the objective function is replaced by Equation (3.7):

$$Minimize \sum (R_i - L_i) \tag{3.7}$$

Equation (3.7) and Equation (3.5) is equivalent for this ILP problem and the proof is given in the following:

#### **Proof:**

From constraints:

$$R_i \geq x_{ri} - x_{li}$$

and  $R_i \geq x_{ri}^{old} - x_{li}^{old}$

we get  $R_i \geq max\{(x_{ri} - x_{li}), (x_{ri}^{old} - x_{li}^{old})\}$

Similarly,  $L_i \leq min\{(x_{ri} - x_{li}), (x_{ri}^{old} - x_{li}^{old})\}$

Because for any i,  $(R_i - L_i)$  has the minimum value only when  $R_i = max\{(x_{ri} - x_{li}), (x_{ri}^{old} - x_{li}^{old})\}$  and  $L_i = min\{(x_{ri} - x_{li}), (x_{ri}^{old} - x_{li}^{old})\}$ , we get:

$$\min\{\sum (R_i - L_i)\}\$$

$$= \min\{\sum (\max\{(x_{ri} - x_{li}), (x_{ri}^{old} - x_{li}^{old})\} - \min\{(x_{ri} - x_{li}), (x_{ri}^{old} - x_{li}^{old})\})\}\$$

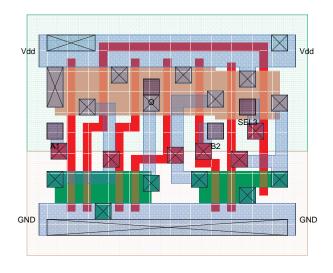

$$= \min\{\sum |(x_{ri} - x_{li}) - (x_{ri}^{old} - x_{li}^{old})|\}\$$