# A Gentle Introduction to High Level Synthesis

#### Jianwen Zhu

Electrical and Computer Engineering University of Toronto

jzhu@eecg.toronto.edu

http://www.eecg.toronto.edu/~jzhu

1

#### **Outline**

- Overview

- Scheduling

- Resource Sharing

- **■** Summary

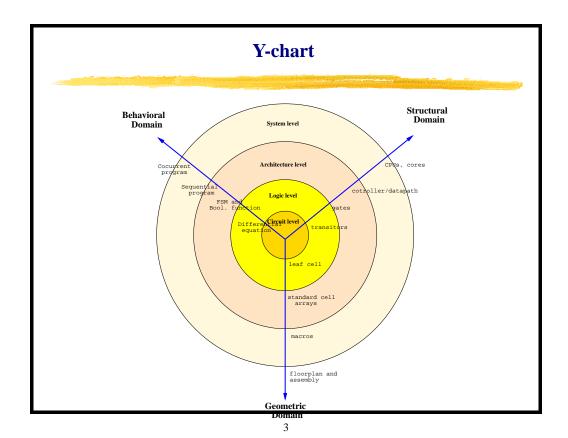

## **High-level Synthesis**

- What is Synthesis

- Given a functional model of a design

- Find a structural model of a design

- Such that some figure of merit is optimized

- Speed

- Area

- Power

- Noise

- Subject to some constraints

- What is High-level Synthesis

- Given an algorithm model of a design

- Find a micro-architecture

- Controller: sequential random logic, ROM

- Datapath: adder, ALU, mux, register, register file

- Such that speed/area/power is optimized

- Subject to some constraints

# **High-level Function Model**

- Can be captured by an imperative program

- **■** C/C++, Java, ...

- Behavioral VHDL/Verilog

- Untimed state machine

- Can be transformed into control-dataflow graph (CDFG) by synthesis front-end

- Ease for machine manipulation

- Control flow: statement

- Data flow: expression

5

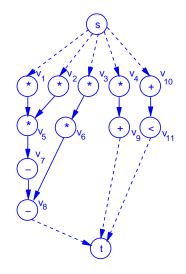

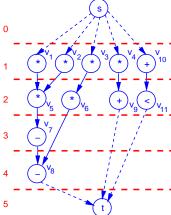

### **Example of Dataflow Graph**

```

2

while(x;a) {

x1 = x + dx;

3

u1 = u - (3 * x + u * dx)

- (3 * y * dx);

5

y1 = y + u * dx;

x = x1;

7

u = u1;

8

9

y = y1;

10

11

```

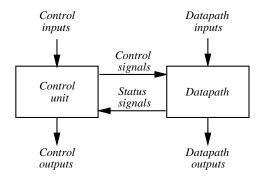

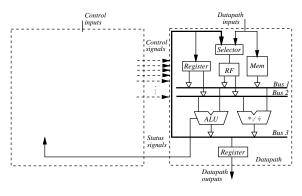

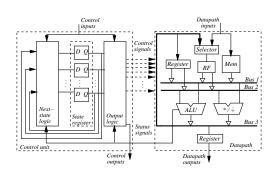

#### **Micro-architecture**

- Controller is responsible for *when* and *what* register transfer operations (assignments) to perform

- Datapath is responsible for *how* to perform the register transfer operations

7

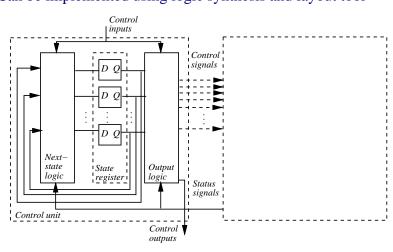

#### **Micro-architecture: Controller**

- Controller is a sequential network

- Can be implemented using logic synthesis and layout tool

# Micro-architecture: Datapath

- Datapath is a network of sequential and combinational components:

- Registers, register files

- Adders, Subtracters, ...

- Steering components: buses, selectors, ...

9

### **Quality Metrics/Constraints**

- Latency: the time it takes to process the data

- Throughput: the rate to process the data

- Cycle time

- Area

- Power

#### **Outline**

- Overview

- Scheduling

- **■** Resource Sharing

- Summary

11

# **Scheduling**

■ Have to decide *when* each operation is performed

untimed state machine  $\mapsto$  timed state machine flow graph  $\mapsto$  ASM chart

- Pretty much like the determine the class schedule

- Dependency constraint: ECE241 is a prerequisite of ECE451

- Resource constraint: Do not have enough #rooms to hold all classes simultaneously

- Here

- Dependency constraint: A depends on the result of B

- Resource constraint: there are at most 3 adders

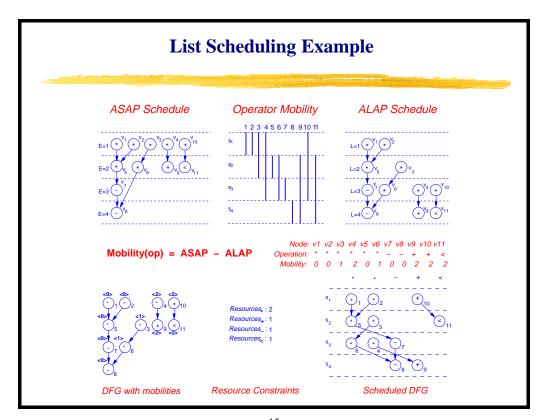

#### **Unconstrained Scheduling: List Scheduling**

- As Soon As Possible (ASAP) schedule

- hedule

- As Late As Possible (ALAP) schedule

13

### **Resource-constrained List Scheduling Scheduling**

- Keep a list a ready operations whose predecessors are all scheduled

- Schedule an operation from the ready list

- Has no resource conflict

- Has higher priority

- Heuristics to determine the priority

- Mobility

- Out degree

- Distance to the sink

# Outline Overview Scheduling Resource Sharing Summary

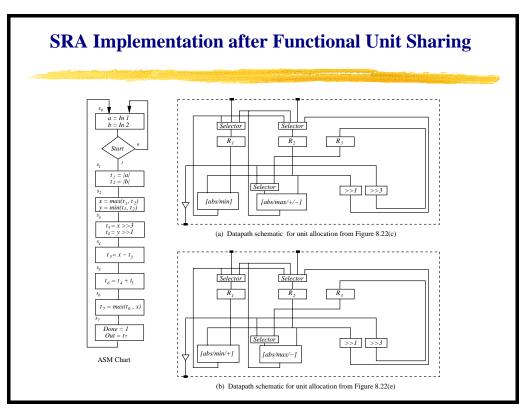

# **Square Root Approximation (SRA) Example**

- $\blacksquare \text{ Computes } O = \sqrt{a^2 + b^2}$

- Approximation:

O = max((0.875x + 0.5y), x) where x = max(|a|,|b|), y = min(|a|,|b|)

- A scheduled design

- ASM chart

17

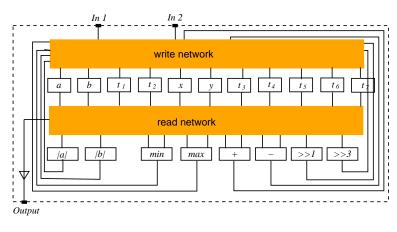

# A Straight-forward Approach

- Map each variable to a distinct register

- Map each operations to a distinct combinational component

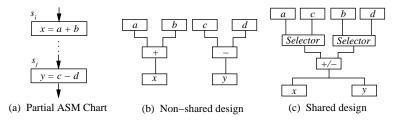

#### **Solving Resource Sharing Problem**

- Resources (registers, functional units) can be shared

- Cast resource sharing problem into a graph problem

- Graph nodes: subject objects to be shared

- Graph edges: sharing relation

- Dual problem:

- Coloring of conflict graph

- Clique-partitioning of compatibility graph

19

### **Resource Sharing Algorithm**

- Graph coloring

- Color one node at a time

- Select the color different from its neighbors

- Graph partitioning

- Select two compatible nodes at a time

- Merge them into a supernode

- Update edges accordingly

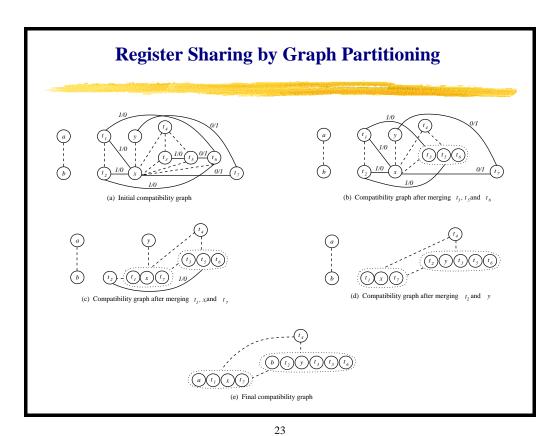

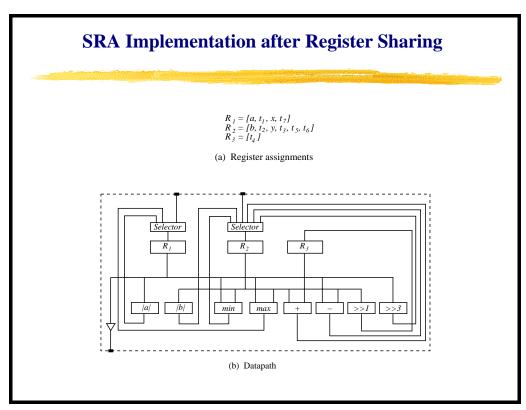

#### **Register Sharing**

- Two variables can share the same register if and only if they have non-overlapping life time

- Lifetime = [first time write, last time read]

- Casting register sharing into graph partitioning problem

- Each vertex represents a variable

- There is a *dashed edge* between two vertices if the corresponding vertices have overlapping life time

- There is a *solid edge* between two vertices if the corresponding vertices have non-overlapping life time

- The solid edge is annotated with #common src/#common dest

21

#

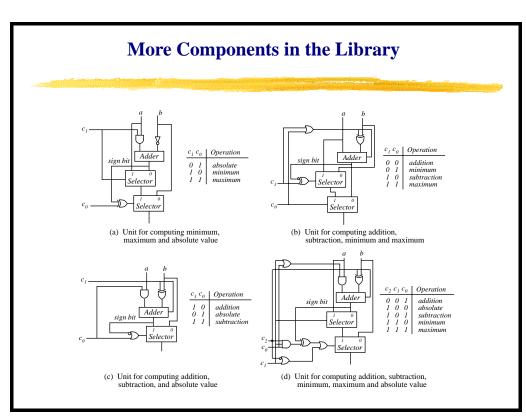

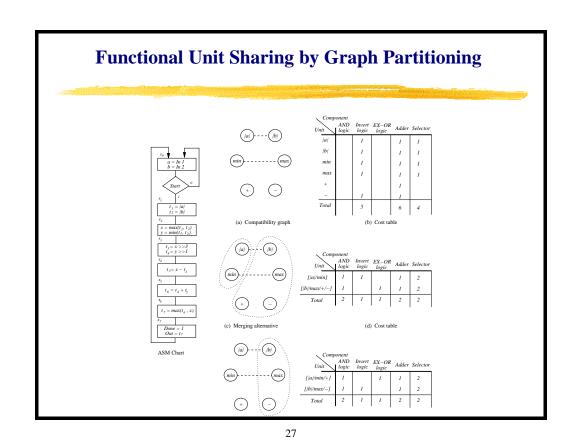

#### **Functional Unit Sharing**

- Two Operations can share the same functional unit if they are non-concurrent and has "similar" functionality

- Sharing priority: #common source, #common destinations

25

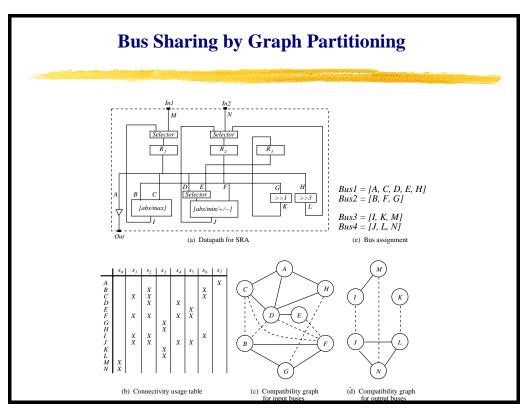

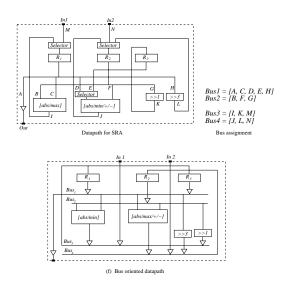

# **Bus Sharing**

- Wires can be expensive

- Different interconnections can be shared if they are not used at the same cycle

- Pitfall: may end up longer wires

29

31

### **Summary**

- High-level synthesis maps an imperative program into a micro-architecture, which can be further synthesized by lower-level tools

- Scheduling determines the control step at which each operation is performed

- Binding determines how variables, operations, data transfered are mapped into shared registers, functional units and buses.