# Xilinx Device Drivers <u>Driver Summary Copyright</u> <u>Main Page Data Structures File List Data Fields Globals</u>

## **Xilinx Device Drivers Documentation**

Generated on 30 Sep 2003 for Xilinx Device Drivers

## **Device Driver Summary**

A summary of each device driver is provided below. This includes links to the driver's layer 1, high-level header file and its layer 0, low-level header file. A description of the device driver layers can be found in the Device Driver Programmer Guide. In addition, <u>building block</u> components are described, followed by a list of layer 2 drivers/adapters available for the <u>VxWorks</u> Real-Time Operating System (RTOS).

### **ATM Controller**

The Asynchronous Transfer Mode (ATM) Controller driver resides in the *atmc* subdirectory. Details of the layer 1 high level driver can be found in the <u>xatmc.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xatmc\_l.h</u> header file.

### Ethernet 10/100 MAC

The Ethernet 10/100 MAC driver resides in the *emac* subdirectory. Details of the layer 1 high level driver can be found in the <u>xemac.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xemac l.h</u> header file.

### Ethernet 10/100 MAC Lite

The Ethernet 10/100 MAC Lite driver resides in the *emaclite* subdirectory. Details of the layer 0 low level driver can be found in the <u>xemaclite\_l.h</u> header file.

### **External Memory Controller**

The External Memory Controller driver resides in the *emc* subdirectory. Details of the layer 1 high level driver can be found in the <u>xemc.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xemc l.h</u> header file.

### **General Purpose I/O**

The General Purpose I/O driver resides in the gpio subdirectory. Details of the layer 1 high level driver can be found in the <u>xgpio.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xgpio\_l.h</u> header file.

### **Gigabit Ethernet MAC**

The 1 Gigabit Ethernet MAC driver resides in the *gemac* subdirectory. Details of the layer 1 high level driver can be found in the <u>xgemac.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xgemac\_l.h</u> header file.

### **HDLC**

The HDLC driver resides in the *hdlc* subdirectory. Details of the layer 1 high level driver can be found in the <u>xhdlc.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xhdlc l.h</u> header file.

### Intel StrataFlash

The Intel StrataFlash driver resides in the *flash* subdirectory. Details of the layer 1 high level driver can be found in the <u>xflash.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xflash\_intel\_l.h</u> header file.

### Inter-Integrated Circuit (IIC)

The IIC driver resides in the *iic* subdirectory. Details of the layer 1 high level driver can be found in the <u>xiic.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xiic\_l.h</u> header file.

### **Interrupt Controller**

The Interrupt Controller driver resides in the *intc* subdirectory. Details of the layer 1 high level driver can be found in the <u>xintc.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xintc\_l.h</u> header file.

### **OPB Arbiter**

The OPB Arbiter driver resides in the *opbarb* subdirectory. Details of the layer 1 high level driver can be found in the <u>xopbarb.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xopbarb\_l.h</u> header file.

### **OPB to PLB Bridge**

The OPB to PLB bridge driver resides in the *opb2plb* subdirectory. Details of the layer 1 high level driver can be found in the <u>xopb2plb.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xopb2plb l.h</u> header file.

### **PCI** Bridge

The PCI bridge driver resides in the *pci* subdirectory. Details of the layer 1 high level driver can be found in the <u>xpci.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xpci\_l.h</u> header file.

### **PLB Arbiter**

The PLB arbiter driver resides in the *plbarb* subdirectory. Details of the layer 1 high level driver can be found in the <u>xplbarb.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xplbarb\_l.h</u> header file.

### **PLB to OPB Bridge**

The PLB to OPB bridge driver resides in the *plb2opb* subdirectory. Details of the layer 1 high level driver can be found in the <u>xplb2opb.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xplb2opb</u> l.h header file.

### Rapid I/O

The Rapid I/O driver resides in the *rapidio* subdirectory. Details of the layer 0 low level driver can be found in the <u>xrapidio\_1.h</u> header file.

### **Serial Peripheral Interface (SPI)**

The SPI driver resides in the *spi* subdirectory. Details of the layer 1 high level driver can be found in the <u>xspi.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xspi\_l.h</u> header file.

### **System ACE**

The System ACE driver resides in the *sysace* subdirectory. Details of the layer 1 high level driver can be found in the <u>xsysace.h</u> header file. Details of the layer 0 low level

driver can be found in the xsysace\_1.h header file.

### Timer/Counter

The Timer/Counter driver resides in the *tmrctr* subdirectory. Details of the layer 1 high level driver can be found in the <u>xtmrctr.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xtmrctr\_l.h</u> header file.

### **UART Lite**

The UART Lite driver resides in the *uartlite* subdirectory. Details of the layer 1 high level driver can be found in the <u>xuartlite.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xuartlite 1.h</u> header file.

### **UART 16450/16550**

The UART 16450/16550 driver resides in the *uartns550* subdirectory. Details of the layer 1 high level driver can be found in the <u>xuartns550.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xuartns550\_l.h</u> header file.

### **Watchdog Timer/Timebase**

The Watchdog Timer/Timebase driver resides in the *wdttb* subdirectory. Details of the layer 1 high level driver can be found in the <u>xwdttb.h</u> header file. Details of the layer 0 low level driver can be found in the <u>xwdttb</u> l.h header file.

## **Building Block Components**

### Common

Common components reside in the *common* subdirectory and comprise a collection of header files and ".c" files that are commonly used by all device drivers and application code. Included in this collection are: <a href="mailto:xstatus.h">xstatus.h</a>, which contains the identifiers for Xilinx status codes; <a href="mailto:xparameters.h">xparameters.h</a>, which contains the identifiers for the driver configurations and memory map; and <a href="mailto:xbasic\_types.h">xbasic\_types.h</a>, which contains identifiers for primitive data types and commonly used constants.

### CPU/CPU\_PPC405

CPU components reside in the *cpu*[\_*ppc405*] sudirectory and comprise I/O functions specific to a processor. These I/O functions are defined in xio.h. These functions are used by drivers and are not intended for external use.

### **IPIF**

IPIF components reside in the *ipif* subdirectory and comprise functions related to the IP Interface (IPIF) interrupt control logic. Since most devices are built with IPIF, drivers utilize this common source code to prevent duplication of code within the drivers. These functions are used by drivers and are not intended for external use.

### **DMA**

DMA components reside in the *dma* subdirectory and comprise functions used for Direct Memory Access (DMA). Both simple DMA and scatter-gather DMA are supported.

### **Packet FIFO**

Packet FIFO components reside in the *packet\_fifo* subdirectory and comprise functions used for packet FIFO control. Packet FIFOs are typically used by devices that process and potentially retransmit packets, such as Ethernet and ATM. These functions are used by drivers and are not intended for external use.

## VxWorks Support

VxWorks RTOS adapters (also known as layer 2 device drivers) are provided for the following devices:

- 10/100 Ethernet MAC (Enhanced Network Driver Interface)

- Gigabit Ethernet MAC (Enhanced Network Driver Interface)

- UART 16550/16450 (Serial IO Interface)

- UART Lite (Serial IO Interface)

- System ACE (Block Device Interface)

# Xilinx Device Drivers <u>Driver Summary Copyright</u> Main Page Data Structures File List Data Fields Globals

## atmc/v1\_00\_c/src/xatmc.h File Reference

### **Detailed Description**

The implementation of the **XAtmc** component, which is the driver for the Xilinx ATM controller.

The Xilinx ATM controller supports the following features:

- Simple and scatter-gather DMA operations, as well as simple memory mapped direct I/O interface (FIFOs).

- Independent internal transmit and receive FIFOs

- Internal loopback

- Header error check (HEC) generation and checking

- Cell buffering with or without header/User Defined

- Parity generation and checking

- Header generation for transmit cell payloads

- Physical interface (PHY) data path of 16 bits

- Basic statistics gathering such as long cells, short cells, parity errors, and HEC errors

The driver does not support all of the features listed above. Features not currently supported by the driver are:

- Simple DMA (in polled or interrupt mode)

- Direct I/O (FIFO) operations in interrupt mode (polled mode does use the FIFO directly)

It is the responsibility of the application get the interrupt handler of the ATM controller and connect it to the interrupt source.

The driver services interrupts and passes ATM cells to the upper layer software through callback functions. The upper layer software must register its callback functions during initialization. The driver requires callback functions for received cells, for confirmation of transmitted cells, and for asynchronous errors. The frequency of interrupts can be controlled with the packet threshold and packet wait bound features of the scatter-gather DMA engine.

The callback function which performs processing for scatter-gather DMA is executed in an interrupt context and is designed to allow the processing of the scatter-gather list to be passed to a thread context. The scatter-gather processing can require more processing than desired in an interrupt context. Functions are provided to be called from the callback function or thread context to get cells from the send and receive scatter-gather list.

Some errors that can occur in the device require a device reset. These errors are listed in the SetErrorHandler function header. The upper layer's error handler is responsible for resetting the device and re-configuring it based on its needs (the driver does not save the current configuration).

#### **DMA Support**

The Xilinx ATMC device is available for both the IBM On-Chip Peripheral Bus (OPB) and Processor Local Bus (PLB). This driver works for both. However, a current limitation of the ATMC device on the PLB is that it does not support DMA. For this reason, the DMA scatter-gather functions (e.g., **XAtmc\_SgSend()**) of this driver will not function for the PLB version of the ATMC device.

#### Note:

Xilinx drivers are typically composed of two components, one is the driver and the other is the adapter. The driver is independent of OS and processor and is intended to be highly portable. The adapter is OS-specific and facilitates communication between the driver and the OS.

This driver is intended to be RTOS and processor independent. It works with physical addresses only. Any needs for dynamic memory management, threads or thread mutual exclusion, virtual memory, or cache control must be satisfied by the layer above this driver.

#### MODIFICATION HISTORY:

### **Data Structures**

```

struct XAtmc struct XAtmc_Config struct XAtmc_Stats

```

### **Configuration options**

These options are used in **XAtmc\_SetOptions**() to configure the device.

```

#define XAT_LOOPBACK_OPTION

#define XAT_POLLED_OPTION

#define XAT_DISCARD_SHORT_OPTION

#define XAT_DISCARD_PARITY_OPTION

```

```

#define XAT_DISCARD_LONG_OPTION

#define XAT_DISCARD_HEC_OPTION

#define XAT_DISCARD_VXI_OPTION

#define XAT_PAYLOAD_ONLY_OPTION

#define XAT_NO_SEND_PARITY_OPTION

```

### **Cell status**

These constants define the status values for a received cell. The status is available when polling to receive a cell or in the buffer descriptor after a cell is received using DMA scatter-gather.

```

#define XAT_CELL_STATUS_LONG

#define XAT_CELL_STATUS_SHORT

#define XAT_CELL_STATUS_BAD_PARITY

#define XAT_CELL_STATUS_BAD_HEC

#define XAT_CELL_STATUS_VXI_MISMATCH

#define XAT_CELL_STATUS_NO_ERROR

```

### Typedefs for callbacks

Callback functions.

```

typedef void(* XAtmc_SgHandler )(void *CallBackRef, Xuint32 CellCount) typedef void(* XAtmc_ErrorHandler )(void *CallBackRef, XStatus ErrorCode)

```

### **Functions**

```

XStatus XAtmc_Initialize (XAtmc *InstancePtr, Xuint16 DeviceId)

XStatus XAtmc_Start (XAtmc *InstancePtr)

XStatus XAtmc_Stop (XAtmc *InstancePtr)

void XAtmc_Reset (XAtmc *InstancePtr)

XStatus XAtmc_SelfTest (XAtmc *InstancePtr)

XAtmc_Config * XAtmc_LookupConfig (Xuint16 DeviceId)

XStatus XAtmc_SgSend (XAtmc *InstancePtr, XBufDescriptor *BdPtr)

XStatus XAtmc_SgRecv (XAtmc *InstancePtr, XBufDescriptor *BdPtr)

XStatus XAtmc SgGetSendCell (XAtmc *InstancePtr, XBufDescriptor **PtrToBdPtr, int

*BdCountPtr)

XStatus XAtmc_SgGetRecvCell (XAtmc *InstancePtr, XBufDescriptor **PtrToBdPtr, int

*BdCountPtr)

XStatus XAtmc_PollSend (XAtmc *InstancePtr, Xuint8 *BufPtr, Xuint32 ByteCount)

XStatus XAtmc PollRecv (XAtmc *InstancePtr, Xuint8 *BufPtr, Xuint32 *ByteCountPtr, Xuint32

*CellStatusPtr)

XStatus XAtmc_SetOptions (XAtmc *InstancePtr, Xuint32 Options)

```

```

Xuint32 XAtmc_GetOptions (XAtmc *InstancePtr)

XStatus XAtmc_SetPhyAddress (XAtmc *InstancePtr, Xuint8 Address)

Xuint8 XAtmc_GetPhyAddress (XAtmc *InstancePtr)

XStatus XAtmc_SetHeader (XAtmc *InstancePtr, Xuint32 Direction, Xuint32 Header)

Xuint32 XAtmc_GetHeader (XAtmc *InstancePtr, Xuint32 Direction)

XStatus XAtmc_SetUserDefined (XAtmc *InstancePtr, Xuint8 UserDefined)

Xuint8 XAtmc GetUserDefined (XAtmc *InstancePtr)

XStatus XAtmc SetPktThreshold (XAtmc *InstancePtr, Xuint32 Direction, Xuint8 Threshold)

XStatus XAtmc_GetPktThreshold (XAtmc *InstancePtr, Xuint32 Direction, Xuint8 *ThreshPtr)

XStatus XAtmc_SetPktWaitBound (XAtmc *InstancePtr, Xuint32 Direction, Xuint32 TimerValue)

XStatus XAtmc_GetPktWaitBound (XAtmc *InstancePtr, Xuint32 Direction, Xuint32 *WaitPtr)

void XAtmc_GetStats (XAtmc *InstancePtr, XAtmc_Stats *StatsPtr)

void XAtmc ClearStats (XAtmc *InstancePtr)

XStatus XAtmc_SetSgRecvSpace (XAtmc *InstancePtr, Xuint32 *MemoryPtr, Xuint32 ByteCount)

XStatus XAtmc_SetSgSendSpace (XAtmc *InstancePtr, Xuint32 *MemoryPtr, Xuint32 ByteCount)

void XAtmc_InterruptHandler (void *InstancePtr)

void XAtmc SetSgRecvHandler (XAtmc *InstancePtr, void *CallBackRef, XAtmc SgHandler

FuncPtr)

void XAtmc_SetSgSendHandler (XAtmc *InstancePtr, void *CallBackRef, XAtmc_SgHandler

FuncPtr)

void XAtmc_SetErrorHandler (XAtmc *InstancePtr, void *CallBackRef, XAtmc_ErrorHandler

FuncPtr)

```

### **Define Documentation**

#### #define XAT\_CELL\_STATUS\_BAD\_HEC

```

XAT_CELL_STATUS_LONG

XAT_CELL_STATUS_SHORT

Cell was too short

XAT_CELL_STATUS_BAD_PARITY

Cell parity was not correct

XAT_CELL_STATUS_BAD_HEC

Cell HEC was not correct

XAT_CELL_STATUS_VXI_MISMATCH

Cell VPI/VCI fields didn't match the expected header values

XAT_CELL_STATUS_NO_ERROR

Cell received without errors

```

#### #define XAT\_CELL\_STATUS\_BAD\_PARITY

XAT\_CELL\_STATUS\_LONG Cell was too long

XAT\_CELL\_STATUS\_SHORT Cell was too short

XAT\_CELL\_STATUS\_BAD\_PARITY Cell parity was not correct

XAT\_CELL\_STATUS\_BAD\_HEC Cell HEC was not correct

XAT\_CELL\_STATUS\_VXI\_MISMATCH Cell VPI/VCI fields didn't match the expected header values

XAT\_CELL\_STATUS\_NO\_ERROR Cell received without errors

#### #define XAT\_CELL\_STATUS\_LONG

XAT\_CELL\_STATUS\_LONG

XAT\_CELL\_STATUS\_SHORT

Cell was too short

XAT\_CELL\_STATUS\_BAD\_PARITY

Cell parity was not correct

XAT\_CELL\_STATUS\_BAD\_HEC

Cell HEC was not correct

XAT\_CELL\_STATUS\_VXI\_MISMATCH

Cell VPI/VCI fields didn't match the expected header values

XAT\_CELL\_STATUS\_NO\_ERROR

Cell received without errors

#### #define XAT\_CELL\_STATUS\_NO\_ERROR

XAT\_CELL\_STATUS\_LONG

XAT\_CELL\_STATUS\_SHORT

Cell was too short

XAT\_CELL\_STATUS\_BAD\_PARITY

Cell parity was not correct

XAT\_CELL\_STATUS\_BAD\_HEC

Cell HEC was not correct

XAT\_CELL\_STATUS\_VXI\_MISMATCH

Cell VPI/VCI fields didn't match the expected header values

XAT\_CELL\_STATUS\_NO\_ERROR

Cell received without errors

#### #define XAT\_CELL\_STATUS\_SHORT

XAT\_CELL\_STATUS\_LONG

XAT\_CELL\_STATUS\_SHORT

Cell was too short

XAT\_CELL\_STATUS\_BAD\_PARITY

Cell parity was not correct

XAT\_CELL\_STATUS\_BAD\_HEC

Cell HEC was not correct

XAT\_CELL\_STATUS\_VXI\_MISMATCH

Cell VPI/VCI fields didn't match the expected header values

XAT\_CELL\_STATUS\_NO\_ERROR

Cell received without errors

#### #define XAT\_CELL\_STATUS\_VXI\_MISMATCH

XAT\_CELL\_STATUS\_LONG Cell was too long XAT\_CELL\_STATUS\_SHORT Cell was too short

XAT\_CELL\_STATUS\_BAD\_PARITY Cell parity was not correct XAT\_CELL\_STATUS\_BAD\_HEC Cell HEC was not correct

XAT\_CELL\_STATUS\_VXI\_MISMATCH Cell VPI/VCI fields didn't match the expected

header values

XAT\_CELL\_STATUS\_NO\_ERROR Cell received without errors

#### #define XAT DISCARD HEC OPTION

XAT\_DISCARD\_SHORT\_OPTION Discard runt/short cells

XAT\_DISCARD\_PARITY\_OPTION Discard cells with parity errors

XAT\_DISCARD\_LONG\_OPTION Discard long cells

XAT\_DISCARD\_HEC\_OPTION Discard cells with HEC errors

XAT\_DISCARD\_VXI\_OPTION Discard cells which don't match in the

VCI/VPI fields

XAT\_PAYLOAD\_ONLY\_OPTION Buffer payload only

XAT\_NO\_SEND\_PARITY\_OPTION Disable parity for sent cells

#### #define XAT DISCARD LONG OPTION

XAT\_DISCARD\_SHORT\_OPTION Discard runt/short cells

XAT DISCARD PARITY OPTION Discard cells with parity errors

XAT\_DISCARD\_LONG\_OPTION Discard long cells

XAT\_DISCARD\_HEC\_OPTION Discard cells with HEC errors

XAT\_DISCARD\_VXI\_OPTION Discard cells which don't match in the

VCI/VPI fields

XAT\_PAYLOAD\_ONLY\_OPTION Buffer payload only

XAT\_NO\_SEND\_PARITY\_OPTION Disable parity for sent cells

#### #define XAT\_DISCARD\_PARITY\_OPTION

XAT\_DISCARD\_SHORT\_OPTION Discard runt/short cells

XAT\_DISCARD\_PARITY\_OPTION Discard cells with parity errors

XAT\_DISCARD\_LONG\_OPTION Discard long cells

XAT\_DISCARD\_HEC\_OPTION Discard cells with HEC errors

XAT\_DISCARD\_VXI\_OPTION Discard cells which don't match in the

VCI/VPI fields

XAT\_PAYLOAD\_ONLY\_OPTION Buffer payload only

XAT\_NO\_SEND\_PARITY\_OPTION Disable parity for sent cells

#### #define XAT\_DISCARD\_SHORT\_OPTION

XAT\_DISCARD\_SHORT\_OPTION Discard runt/short cells

XAT DISCARD PARITY OPTION Discard cells with parity errors

XAT\_DISCARD\_LONG\_OPTION Discard long cells

XAT\_DISCARD\_HEC\_OPTION Discard cells with HEC errors

XAT\_DISCARD\_VXI\_OPTION Discard cells which don't match in the

VCI/VPI fields

XAT\_PAYLOAD\_ONLY\_OPTION Buffer payload only

XAT\_NO\_SEND\_PARITY\_OPTION Disable parity for sent cells

#### #define XAT DISCARD VXI OPTION

XAT\_DISCARD\_SHORT\_OPTION Discard runt/short cells

XAT\_DISCARD\_PARITY\_OPTION Discard cells with parity errors

XAT\_DISCARD\_LONG\_OPTION Discard long cells

XAT\_DISCARD\_HEC\_OPTION Discard cells with HEC errors

XAT\_DISCARD\_VXI\_OPTION Discard cells which don't match in the

VCI/VPI fields

XAT\_PAYLOAD\_ONLY\_OPTION Buffer payload only

XAT\_NO\_SEND\_PARITY\_OPTION Disable parity for sent cells

#### #define XAT LOOPBACK OPTION

XAT\_DISCARD\_SHORT\_OPTION Discard runt/short cells

XAT\_DISCARD\_PARITY\_OPTION Discard cells with parity errors

XAT\_DISCARD\_LONG\_OPTION Discard long cells

XAT\_DISCARD\_HEC\_OPTION Discard cells with HEC errors

XAT\_DISCARD\_VXI\_OPTION Discard cells which don't match in the

VCI/VPI fields

XAT\_PAYLOAD\_ONLY\_OPTION Buffer payload only

XAT\_NO\_SEND\_PARITY\_OPTION Disable parity for sent cells

#### #define XAT\_NO\_SEND\_PARITY\_OPTION

XAT\_DISCARD\_SHORT\_OPTION Discard runt/short cells

XAT\_DISCARD\_PARITY\_OPTION Discard cells with parity errors

XAT\_DISCARD\_LONG\_OPTION Discard long cells

XAT\_DISCARD\_HEC\_OPTION Discard cells with HEC errors

XAT\_DISCARD\_VXI\_OPTION Discard cells which don't match in the

VCI/VPI fields

XAT\_PAYLOAD\_ONLY\_OPTION Buffer payload only

XAT\_NO\_SEND\_PARITY\_OPTION Disable parity for sent cells

#### #define XAT\_PAYLOAD\_ONLY\_OPTION

XAT\_DISCARD\_SHORT\_OPTION Discard runt/short cells

XAT\_DISCARD\_PARITY\_OPTION Discard cells with parity errors

XAT\_DISCARD\_LONG\_OPTION Discard long cells

XAT\_DISCARD\_HEC\_OPTION Discard cells with HEC errors

XAT\_DISCARD\_VXI\_OPTION Discard cells which don't match in the

VCI/VPI fields

XAT\_PAYLOAD\_ONLY\_OPTION Buffer payload only

XAT\_NO\_SEND\_PARITY\_OPTION Disable parity for sent cells

#### #define XAT\_POLLED\_OPTION

XAT\_DISCARD\_SHORT\_OPTION Discard runt/short cells

XAT\_DISCARD\_PARITY\_OPTION Discard cells with parity errors

XAT\_DISCARD\_LONG\_OPTION Discard long cells

XAT\_DISCARD\_HEC\_OPTION Discard cells with HEC errors

XAT DISCARD VXI OPTION Discard cells which don't match in the

VCI/VPI fields

XAT\_PAYLOAD\_ONLY\_OPTION Buffer payload only

XAT\_NO\_SEND\_PARITY\_OPTION Disable parity for sent cells

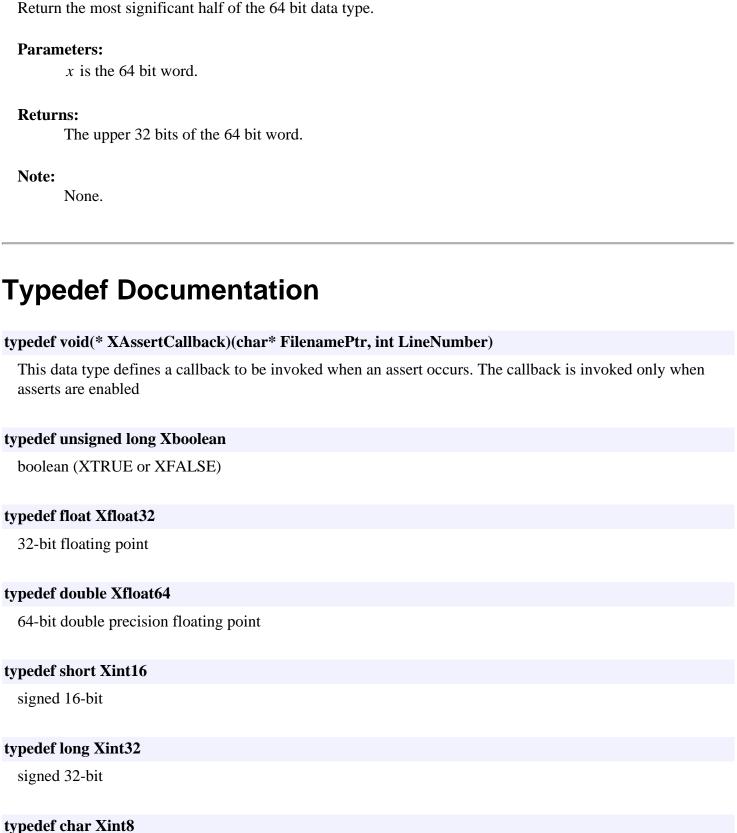

### **Typedef Documentation**

#### typedef void(\* XAtmc\_ErrorHandler)(void \*CallBackRef, XStatus ErrorCode)

Callback when data is sent or received with scatter-gather DMA.

#### **Parameters:**

CallBackRef is a callback reference passed in by the upper layer when setting the callback functions,

and passed back to the upper layer when the callback is invoked.

*ErrorCode* indicates the error that occurred.

#### typedef void(\* XAtmc\_SgHandler)(void \*CallBackRef, Xuint32 CellCount)

Callback when data is sent or received with scatter-gather DMA.

#### **Parameters:**

CallBackRef is a callback reference passed in by the upper layer when setting the callback functions, and passed back to the upper layer when the callback is invoked.

CellCount is the number of cells sent or received.

### **Function Documentation**

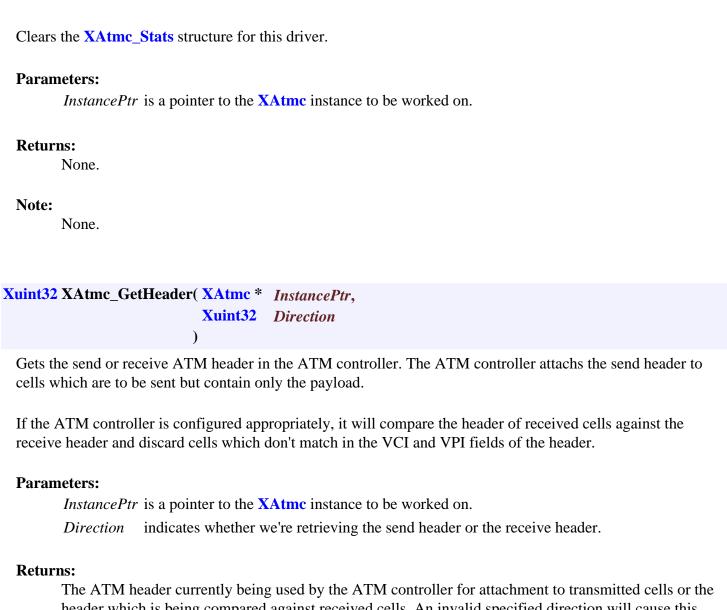

void XAtmc\_ClearStats( XAtmc \* InstancePtr)

header which is being compared against received cells. An invalid specified direction will cause this function to return a value of 0.

#### **Note:**

None.

Xuint32 XAtmc\_GetOptions( XAtmc \* InstancePtr)

Gets Atmc driver/device options. The value returned is a bit-mask representing the options. A one (1) in the bit-mask means the option is on, and a zero (0) means the option is off.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

#### **Returns:**

The 32-bit value of the Atmc options. The value is a bit-mask representing all options that are currently enabled. See **xatmc.h** for a detailed description of the options.

#### Note:

None.

#### Xuint8 XAtmc\_GetPhyAddress( XAtmc \* InstancePtr)

Gets the PHY address for this driver/device.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

#### **Returns:**

The 5-bit PHY address (0 - 31) currently being used by the ATM controller.

#### **Note:**

None.

Gets the value of the packet threshold register for this driver/device. The packet threshold is used for interrupt coalescing when the ATM controller is configured for scatter-gather DMA.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

Direction indicates the channel, send or receive, from which the threshold register is read.

ThreshPtr is a pointer to the byte into which the current value of the packet threshold register will be

copied. An output parameter. A value of 0 indicates the use of packet threshold by the

hardware is disabled.

#### Returns:

- o XST SUCCESS if the packet threshold was retrieved successfully

- o XST\_NOT\_SGDMA if the ATM controller is not configured for scatter-gather DMA

- o XST INVALID PARAM if an invalid direction was specified

Note:

None.

Gets the packet wait bound register for this driver/device. The packet wait bound is used for interrupt coalescing when the ATM controller is configured for scatter-gather DMA.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

*Direction* indicates the channel, send or receive, from which the threshold register is read.

WaitPtr is a pointer to the byte into which the current value of the packet wait bound register will be

copied. An output parameter. Units are in milliseconds in the range 0 - 1023. A value of 0

indicates the packet wait bound timer is disabled.

#### **Returns:**

- o XST\_SUCCESS if the packet wait bound was retrieved successfully

- o XST\_NOT\_SGDMA if the ATM controller is not configured for scatter-gather DMA

- o XST\_INVALID\_PARAM if an invalid direction was specified

#### Note:

None.

Gets a copy of the **XAtmc\_Stats** structure, which contains the current statistics for this driver.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

StatsPtr is an output parameter, and is a pointer to a stats buffer into which the current statistics will be copied.

#### **Returns:**

None. Although the output parameter will contain a copy of the statistics upon return from this function.

#### Note:

Gets the 2nd byte of the User Defined data in the ATM controller for the channel which is sending data. The ATM controller will attach the header to all cells which are being sent and do not have a header. The header of a 16 bit Utopia interface contains the User Defined data which is two bytes. The first byte contains the HEC field and the second byte is available for user data. This function only allows the second byte to be retrieved.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

#### **Returns:**

The second byte of the User Defined data.

#### **Note:**

None.

Initializes a specific ATM controller instance/driver. The initialization entails:

- Initialize fields of the **XAtmc** structure

- Clear the ATM statistics for this device

- Initialize the IPIF component with its register base address

- Configure the FIFO components with their register base addresses.

- Configure the DMA channel components with their register base addresses. At some later time, memory pools for the scatter-gather descriptor lists will be passed to the driver.

- Reset the ATM controller

The only driver function that should be called before this Initialize function is called is GetInstance.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

DeviceId

is the unique id of the device controlled by this **XAtmc** instance. Passing in a device id associates the generic **XAtmc** instance to a specific device, as chosen by the caller or application developer.

#### **Returns:**

- XST\_SUCCESS if initialization was successful

- o XST\_DEVICE\_IS\_STARTED if the device has already been started

#### Note:

Interrupt handler for the ATM controller driver. It performs the following processing:

- Get the interrupt status from the IpIf to determine the source of the interrupt. The source can be: the ATM controller, the send packet FIFO, the receive packet FIFO, the send DMA channel, or the receive DMA channel. The packet FIFOs only interrupt during "deadlock" conditions. All other FIFO-related interrupts are generated by the ATM controller.

- Call the appropriate handler based on the source of the interrupt.

#### **Parameters:**

*InstancePtr* contains a pointer to the ATMC controller instance for the interrupt.

#### **Returns:**

None.

#### **Note:**

None.

####

Looks up the device configuration based on the unique device ID. The table AtmcConfigTable contains the configuration info for each device in the system.

#### **Parameters:**

DeviceId contains the unique device ID that for the device. This ID is used to lookup the configuration.

#### **Returns:**

A pointer to the configuration for the specified device, or XNULL if the device could not be found.

#### Note:

Receives an ATM cell in polled mode. The device/driver must be in polled mode before calling this function. The driver receives the cell directly from the ATM controller packet FIFO. This is a non-blocking receive, in that if there is no cell ready to be received at the device, the function returns with an error. The buffer into which the cell will be received must be word-aligned.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

BufPtr is a pointer to a word-aligned buffer into which the received Atmc cell will be copied.

ByteCountPtr is both an input and an output parameter. It is a pointer to the size of the buffer on entry

into the function and the size the received cell on return from the function.

CellStatusPtr is both an input and an output parameter. It is a pointer to the status of the cell which is

received. It is only valid if the return value indicates success. The status is necessary when cells with errors are not being discarded. This status is a bit mask which may

contain one or more of the following values with the exception of

XAT\_CELL\_STATUS\_NO\_ERROR which is mutually exclusive. The status values are:

- XAT\_CELL\_STATUS\_NO\_ERROR indicates the cell was received without any errors

- XAT\_CELL\_STATUS\_BAD\_PARITY indicates the cell parity was not correct

- XAT CELL STATUS BAD HEC indicates the cell HEC was not correct

- XAT\_CELL\_STATUS\_SHORT indicates the cell was not the correct length

- XAT\_CELL\_STATUS\_VXI\_MISMATCH indicates the cell VPI/VCI fields did not match the expected header values

#### **Returns:**

- o XST\_SUCCESS if the cell was sent successfully

- o XST DEVICE IS STOPPED if the device has not yet been started

- o XST\_NOT\_POLLED if the device is not in polled mode

- o XST NO DATA if tThere is no cell to be received from the FIFO

- XST\_BUFFER\_TOO\_SMALL if the buffer to receive the cell is too small for the cell waiting in the FIFO.

#### **Note:**

The input buffer must be big enough to hold the largest ATM cell. The buffer must also be 32-bit aligned.

Sends an ATM cell in polled mode. The device/driver must be in polled mode before calling this function. The driver writes the cell directly to the ATM controller packet FIFO, then enters a loop checking the device status for completion or error. The buffer to be sent must be word-aligned.

It is assumed that the upper layer software supplies a correctly formatted ATM cell based upon the configuration of the ATM controller (attaching header or not).

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

BufPtr is a pointer to a word-aligned buffer containing the ATM cell to be sent.

ByteCount is the size of the ATM cell. An ATM cell for a 16 bit Utopia interface is 54 bytes with a 6

byte header and 48 bytes of payload. This function may be used to send short cells with or

without headers depending on the configuration of the ATM controller.

#### **Returns:**

- o XST\_SUCCESS if the cell was sent successfully

- o XST\_DEVICE\_IS\_STOPPED if the device has not yet been started

- o XST\_NOT\_POLLED if the device is not in polled mode

- o XST\_PFIFO\_NO\_ROOM if there is no room in the FIFO for this cell

- o XST\_FIFO\_ERROR if the FIFO was overrun or underrun

#### Note:

There is the possibility that this function will not return if the hardware is broken (i.e., it never sets the status bit indicating that transmission is done). If this is of concern to the user, the user should provide protection from this problem - perhaps by using a different timer thread to monitor the PollSend thread.

The input buffer must be big enough to hold the largest ATM cell. The buffer must also be 32-bit aligned.

#### void XAtmc Reset( XAtmc \* InstancePtr)

Resets the ATM controller. It resets the the DMA channels, the FIFOs, and the ATM controller. The reset does not remove any of the buffer descriptors from the scatter-gather list for DMA. Reset must only be called after the driver has been initialized.

The configuration after this reset is as follows:

- Disabled transmitter and receiver

- Default packet threshold and packet wait bound register values for scatter-gather DMA operation

- PHY address of 0

The upper layer software is responsible for re-configuring (if necessary) and restarting the ATM controller after the reset.

When a reset is required due to an internal error, the driver notifies the upper layer software of this need through the ErrorHandler callback and specific status codes. The upper layer software is responsible for calling this Reset function and then re-configuring the device.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

#### **Returns:**

None.

#### Note:

The reset is accomplished by setting the IPIF reset register. This takes care of resetting all hardware blocks, including the ATM controller.

#### XStatus XAtmc\_SelfTest( XAtmc \* InstancePtr)

Performs a self-test on the ATM controller device. The test includes:

- Run self-test on DMA channel, FIFO, and IPIF components

- Reset the ATM controller device, check its registers for proper reset values, and run an internal loopback test on the device. The internal loopback uses the device in polled mode.

This self-test is destructive. On successful completion, the device is reset and returned to its default configuration. The caller is responsible for re-configuring the device after the self-test is run.

It should be noted that data caching must be disabled when this function is called because the DMA self-test uses two local buffers (on the stack) for the transfer test.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

#### **Returns:**

- XST\_SUCCESS if self-test was successful

- o XST\_PFIFO\_BAD\_REG\_VALUE if the FIFO failed register self-test

- o XST\_DMA\_TRANSFER\_ERROR if DMA failed data transfer self-test

- XST\_DMA\_RESET\_REGISTER\_ERROR if DMA control register value was incorrect after a reset

- o XST\_REGISTER\_ERROR if the ATM controller failed register reset test

- o XST\_LOOPBACK\_ERROR if the ATM controller internal loopback failed

- o XST\_IPIF\_REG\_WIDTH\_ERROR if an invalid register width was passed into the function

- o XST\_IPIF\_RESET\_REGISTER\_ERROR if the value of a register at reset was invalid

- XST\_IPIF\_DEVICE\_STATUS\_ERROR if a write to the device status register did not read back correctly

- o XST\_IPIF\_DEVICE\_ACK\_ERROR if a bit in the device status register did not reset when acked

- o XST\_IPIF\_DEVICE\_ENABLE\_ERROR if the device interrupt enable register was not updated correctly by the hardware when other registers were written to

- XST\_IPIF\_IP\_STATUS\_ERROR if a write to the IP interrupt status register did not read back correctly

- o XST\_IPIF\_IP\_ACK\_ERROR if one or more bits in the IP status register did not reset when acked

- XST\_IPIF\_IP\_ENABLE\_ERROR if the IP interrupt enable register was not updated correctly when other registers were written to

#### **Note:**

Because this test uses the PollSend function for its loopback testing, there is the possibility that this function will not return if the hardware is broken (i.e., it never sets the status bit indicating that transmission is done). If this is of concern to the user, the user should provide protection from this problem - perhaps by using a different timer thread to monitor the self-test thread.

Sets the callback function for handling errors. The upper layer software should call this function during initialization.

The error callback is invoked by the driver within interrupt context, so it needs to do its job quickly. If there are potentially slow operations within the callback which should be done at task-level.

The Xilinx errors that must be handled by the callback are:

- XST\_DMA\_ERROR indicates an unrecoverable DMA error occurred. This is typically a bus error or bus timeout. The handler must reset and re-configure the device.

- XST\_FIFO\_ERROR indicates an unrecoverable FIFO error occurred. This is a deadlock condition in the packet FIFO. The handler must reset and re-configure the device.

- XST\_RESET\_ERROR indicates an unrecoverable ATM controller error occurred, usually an overrun or underrun. The handler must reset and re-configure the device.

- XST\_ATMC\_ERROR\_COUNT\_MAX indicates the counters of the ATM controller have reached the maximum value and that the statistics of the ATM controller should be cleared.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

CallBackRef is a reference pointer to be passed back to the adapter in the callback. This helps the adapter correlate the callback to a particular driver.

FuncPtr is the pointer to the callback function.

#### **Returns:**

None.

#### Note:

Sets the send or receive ATM header in the ATM controller. If cells with only payloads are given to the controller to be sent, it will attach the header to the cells. If the ATM controller is configured appropriately, it will compare the header of received cells against the receive header and discard cells which don't match in the VCI and VPI fields of the header.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

Direction indicates the direction, send(transmit) or receive, for the header to set.

Header contains the ATM header to be attached to each transmitted cell for cells with only

payloads or the expected header for cells which are received.

#### **Returns:**

- o XST\_SUCCESS if the PHY address was set successfully

- o XST\_DEVICE\_IS\_STARTED if the device has not yet been stopped

- o XST\_INVALID\_PARAM if an invalid direction was specified

#### Note:

None.

Set Atmc driver/device options. The device must be stopped before calling this function. The options are contained within a bit-mask with each bit representing an option. A one (1) in the bit-mask turns an option on, and a zero (0) turns the option off. See **xatmc.h** for a detailed description of the available options.

#### **Parameters:**

InstancePtr is a pointer to the XAtmc instance to be worked on.OptionsFlag is a bit-mask representing the Atmc options to turn on or off

#### **Returns:**

- XST\_SUCCESS if options were set successfully

- o XST DEVICE IS STARTED if the device has not yet been stopped

#### **Note:**

This function is not thread-safe and makes use of internal resources that are shared between the Start, Stop, and SetOptions functions, so if one task might be setting device options while another is trying to start the device, protection of this shared data (typically using a semaphore) is required.

Sets the PHY address for this driver/device. The address is a 5-bit value. The device must be stopped before calling this function.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on. *Address* contains the 5-bit PHY address (0 - 31).

#### **Returns:**

- o XST\_SUCCESS if the PHY address was set successfully

- o XST\_DEVICE\_IS\_STARTED if the device has not yet been stopped

#### **Note:**

None.

Sets the packet count threshold register for this driver/device. The device must be stopped before setting the threshold. The packet count threshold is used for interrupt coalescing, which reduces the frequency of interrupts from the device to the processor. In this case, the scatter-gather DMA engine only interrupts when the packet count threshold is reached, instead of interrupting for each packet.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

Direction indicates the channel, send or receive, from which the threshold register is read.

Threshold is the value of the packet threshold count used during interrupt coalescing. A value of 0 disables the use of packet threshold by the hardware.

#### **Returns:**

- XST\_SUCCESS if the threshold was successfully set

- o XST\_NOT\_SGDMA if the ATM controller is not configured for scatter-gather DMA

- o XST\_DEVICE\_IS\_STARTED if the device has not been stopped

- XST\_DMA\_SG\_COUNT\_EXCEEDED if the threshold must be equal to or less than the number of descriptors in the list

- o XST\_INVALID\_PARAM if an invalid direction was specified

#### Note:

Sets the packet wait bound register for this driver/device. The device must be stopped before setting the timer value. The packet wait bound is used during interrupt coalescing to trigger an interrupt when not enough packets have been received to reach the packet count threshold.

The timer is in milliseconds.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

Direction indicates the channel, send or receive, from which the threshold register is read.

*TimerValue* is the value of the packet wait bound used during interrupt coalescing. It is in milliseconds in the range 0 - 1023. A value of 0 disables the packet wait bound timer.

#### **Returns:**

- o XST\_SUCCESS if the packet wait bound was set successfully

- o XST\_NOT\_SGDMA if the ATM controller is not configured for scatter-gather DMA

- o XST DEVICE IS STARTED if the device has not been stopped

- XST\_INVALID\_PARAM if an invalid direction was specified

#### **Note:**

None.

```

void XAtmc_SetSgRecvHandler( XAtmc * InstancePtr,

void * CallBackRef,

XAtmc_SgHandler FuncPtr

)

```

Sets the callback function for handling received cells in scatter-gather DMA mode. The upper layer software should call this function during initialization. The callback is called when a number of cells, determined by the DMA scatter-gather packet threshold, are received. The number of received cells is passed to the callback function. The callback function should communicate the data to a thread such that the scatter-gather list processing is not performed in an interrupt context.

The scatter-gather list processing of the thread context should call the function to get the buffer descriptors for each received cell from the list and should attach a new buffer to each descriptor. It is important that the specified number of cells passed to the callback function are handled by the scatter-gather list processing.

The callback is invoked by the driver within interrupt context, so it needs to do its job quickly. If there are other potentially slow operations within the callback, these should be done at task-level.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

CallBackRef is a reference pointer to be passed back to the application in the callback. This helps the application correlate the callback to a particular driver.

*FuncPtr* is the pointer to the callback function.

#### **Returns:**

#### Note:

None.

Gives the driver the memory space to be used for the scatter-gather DMA receive descriptor list. This function should only be called once, during initialization of the Atmc driver. The memory space must be word-aligned.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on. *MemoryPtr* is a pointer to the word-aligned memory.

ByteCount is the length, in bytes, of the memory space.

#### **Returns:**

- o XST\_SUCCESS if the space was initialized successfully

- o XST\_NOT\_SGDMA if the ATM controller is not configured for scatter-gather DMA

- o XST\_DMA\_SG\_LIST\_EXISTS if the list space has already been created

#### Note:

If the device is configured for scatter-gather DMA, this function must be called AFTER the XAtmc\_Initialize function because the DMA channel components must be initialized before the memory space is set.

Sets the callback function for handling confirmation of transmitted cells in scatter-gather DMA mode. The upper layer software should call this function during initialization. The callback is called when a number of cells, determined by the DMA scatter-gather packet threshold, are sent. The number of sent cells is passed to the callback function. The callback function should communicate the data to a thread such that the scatter-gather list processing is not performed in an interrupt context.

The scatter-gather list processing of the thread context should call the function to get the buffer descriptors for each sent cell from the list and should also free the buffers attached to the descriptors if necessary. It is important that the specified number of cells passed to the callback function are handled by the scatter-gather list processing.

The callback is invoked by the driver within interrupt context, so it needs to do its job quickly. If there are potentially slow operations within the callback, these should be done at task-level.

#### Parameters:

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

*CallBackRef* is a reference pointer to be passed back to the application in the callback. This helps the application correlate the callback to a particular driver.

FuncPtr is the pointer to the callback function.

#### **Returns:**

None.

#### Note:

None.

Gives the driver the memory space to be used for the scatter-gather DMA transmit descriptor list. This function should only be called once, during initialization of the Atmc driver. The memory space must be word-aligned.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

*MemoryPtr* is a pointer to the word-aligned memory.

ByteCount is the length, in bytes, of the memory space.

#### **Returns:**

- o XST\_SUCCESS if the space was initialized successfully

- o XST\_NOT\_SGDMA if the ATM controller is not configured for scatter-gather DMA

- o XST\_DMA\_SG\_LIST\_EXISTS if the list space has already been created

#### Note:

If the device is configured for scatter-gather DMA, this function must be called AFTER the XAtmc\_Initialize function because the DMA channel components must be initialized before the memory space is set.

Sets the 2nd byte of the User Defined data in the ATM controller for the channel which is sending data. The ATM controller will attach the header to all cells which are being sent and do not have a header. The header of a 16 bit Utopia interface contains the User Defined data which is two bytes. The first byte contains the HEC field and the second byte is available for user data. This function only allows the second byte to be set.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on. *UserDefined* contains the second byte of the User Defined data.

#### **Returns:**

- o XST\_SUCCESS if the user-defined data was set successfully

- o XST\_DEVICE\_IS\_STARTED if the device has not yet been stopped

#### Note:

None.

Gets the first buffer descriptor of the oldest cell which was received by the scatter-gather DMA channel of the ATM controller. This function is provided to be called from a callback function such that the buffer descriptors for received cells can be processed. The function should be called by the application repetitively for the number of cells indicated as an argument in the callback function. This function may also be used when only payloads are being sent and received by the ATM controller.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

*PtrToBdPtr* is a pointer to a buffer descriptor pointer which will be modified to point to the first buffer descriptor of the cell. This input argument is also an output.

BdCountPtr is a pointer to a buffer descriptor count which will be modified to indicate the number of buffer descriptors for the cell. This input argument is also an output.

#### **Returns:**

A status is returned which contains one of values below. The pointer to a buffer descriptor pointed to by PtrToBdPtr and a count of the number of buffer descriptors for the cell pointed to by BdCountPtr are both modified if the return status indicates success. The status values are:

- o XST\_SUCCESS if a descriptor was successfully returned to the driver.

- o XST NOT SGDMA if the device is not in scatter-gather DMA mode.

- o XST\_DMA\_SG\_NO\_LIST if the scatter gather list has not been created.

- XST\_DMA\_SG\_LIST\_EMPTY if no buffer descriptor was retrieved from the list because there

are no buffer descriptors to be processed in the list.

#### Note:

```

XStatus XAtmc_SgGetSendCell( XAtmc * InstancePtr, XBufDescriptor ** PtrToBdPtr, int * BdCountPtr

```

Gets the first buffer descriptor of the oldest cell which was sent by the scatter-gather DMA channel of the ATM controller. This function is provided to be called from a callback function such that the buffer descriptors for sent cells can be processed. The function should be called by the application repetitively for the number of cells indicated as an argument in the callback function. This function may also be used when only payloads are being sent and received by the ATM controller.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

*PtrToBdPtr* is a pointer to a buffer descriptor pointer which will be modified to point to the first buffer descriptor of the cell. This input argument is also an output.

BdCountPtr is a pointer to a buffer descriptor count which will be modified to indicate the number of buffer descriptors for the cell. this input argument is also an output.

#### **Returns:**

A status is returned which contains one of values below. The pointer to a buffer descriptor pointed to by PtrToBdPtr and a count of the number of buffer descriptors for the cell pointed to by BdCountPtr are both modified if the return status indicates success. The status values are:

- o XST\_SUCCESS if a descriptor was successfully returned to the driver.

- o XST\_NOT\_SGDMA if the device is not in scatter-gather DMA mode.

- o XST DMA SG NO LIST if the scatter gather list has not been created.

- XST\_DMA\_SG\_LIST\_EMPTY if no buffer descriptor was retrieved from the list because there

are no buffer descriptors to be processed in the list.

#### Note:

None.

Adds this descriptor, with an attached empty buffer, into the receive descriptor list. The buffer attached to the descriptor must be word-aligned. This is used by the upper layer software during initialization when first setting up the receive descriptors, and also during reception of cells to replace filled buffers with empty buffers. The contents of the specified buffer descriptor are copied into the scatter-gather transmit list. This function can be called when the device is started or stopped.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

*BdPtr* is a pointer to the buffer descriptor that will be added to the descriptor list.

#### **Returns:**

- o XST\_SUCCESS if a descriptor was successfully returned to the driver

- o XST NOT SGDMA if the device is not in scatter-gather DMA mode

- o XST\_DMA\_SG\_LIST\_FULL if the receive descriptor list is full

- XST\_DMA\_SG\_BD\_LOCKED if the DMA channel cannot insert the descriptor into the list because a locked descriptor exists at the insert point.

- XST\_DMA\_SG\_NOTHING\_TO\_COMMIT if even after inserting a descriptor into the list, the DMA channel believes there are no new descriptors to commit.

#### Note:

None.

Sends an ATM cell using scatter-gather DMA. The caller attaches the cell to one or more buffer descriptors, then calls this function once for each descriptor. The caller is responsible for allocating and setting up the descriptor. An entire ATM cell may or may not be contained within one descriptor. The contents of the buffer descriptor are copied into the scatter-gather transmit list. The caller is responsible for providing mutual exclusion to guarantee that a cell is contiguous in the transmit list. The buffer attached to the descriptor must be word-aligned.

The driver updates the descriptor with the device control register before being inserted into the transmit list. If this is the last descriptor in the cell, the inserts are committed, which means the descriptors for this cell are now available for transmission.

It is assumed that the upper layer software supplies a correctly formatted ATM cell based upon the configuration of the ATM controller (attaching header or not). The ATM controller must be started before calling this function.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

*BdPtr* is the address of a descriptor to be inserted into the transmit ring.

#### **Returns:**

- XST\_SUCCESS if the buffer was successfully sent

- XST DEVICE IS STOPPED if the ATM controller has not been started yet

- o XST\_NOT\_SGDMA if the device is not in scatter-gather DMA mode

- o XST\_DMA\_SG\_LIST\_FULL if the descriptor list for the DMA channel is full

- XST\_DMA\_SG\_BD\_LOCKED if the DMA channel cannot insert the descriptor into the list because a locked descriptor exists at the insert point

- XST\_DMA\_SG\_NOTHING\_TO\_COMMIT if even after inserting a descriptor into the list, the DMA channel believes there are no new descriptors to commit. If this is ever encountered, there is likely a thread mutual exclusion problem on transmit.

#### Note:

This function is not thread-safe. The user must provide mutually exclusive access to this function if there are to be multiple threads that can call it.

#### **XStatus XAtmc\_Start( XAtmc \*** *InstancePtr*)

Starts the ATM controller as follows:

- If not in polled mode enable interrupts

- Enable the transmitter

- Enable the receiver

- Start the DMA channels if the descriptor lists are not empty

It is necessary for the caller to connect the interrupt servive routine of the ATM controller to the interrupt source, typically an interrupt controller, and enable the interrupt in the interrupt controller.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

#### **Returns:**

- XST\_SUCCESS if the device was started successfully

- o XST\_DEVICE\_IS\_STARTED if the device is already started

- XST\_DMA\_SG\_NO\_LIST if configured for scatter-gather DMA and a descriptor list has not yet been created for the send or receive channel.

- o XST\_DMA\_SG\_LIST\_EMPTY iff configured for scatter-gather DMA and no buffer descriptors have been put into the list for the receive channel.

#### Note:

This function makes use of internal resources that are shared between the Start, Stop, and SetOptions functions. So if one task might be setting device options while another is trying to start the device, the user is required to provide protection of this shared data (typically using a semaphore).

#### **XStatus XAtmc\_Stop( XAtmc \*** *InstancePtr*)

Stops the ATM controller as follows:

- Stop the DMA channels (wait for acknowledgment of stop)

- Disable the transmitter and receiver

- Disable interrupts if not in polled mode

It is the callers responsibility to disconnect the interrupt handler of the ATM controller from the interrupt source, typically an interrupt controller, and disable the interrupt in the interrupt controller.

#### **Parameters:**

*InstancePtr* is a pointer to the **XAtmc** instance to be worked on.

#### **Returns:**

- o XST\_SUCCESS if the device was stopped successfully

- o XST\_DEVICE\_IS\_STOPPED if the device is already stopped

#### Note:

This function makes use of internal resources that are shared between the Start, Stop, and SetOptions

| functions. So | o if one task n | night be setting | device options  | while anot | ther is trying t | to stop the | device, th | ıe |

|---------------|-----------------|------------------|-----------------|------------|------------------|-------------|------------|----|

| user is requi | red to provide  | protection of t  | his shared data | (typically | using a semap    | ohore).     |            |    |

Generated on 30 Sep 2003 for Xilinx Device Drivers

XILINX IS PROVIDING THIS DESIGN, CODE, OR INFORMATION "AS IS" AS A COURTESY TO YOU, SOLELY FOR USE IN DEVELOPING PROGRAMS AND SOLUTIONS FOR XILINX DEVICES. BY PROVIDING THIS DESIGN, CODE, OR INFORMATION AS ONE POSSIBLE IMPLEMENTATION OF THIS FEATURE, APPLICATION OR STANDARD, XILINX IS MAKING NO REPRESENTATION THAT THIS IMPLEMENTATION IS FREE FROM ANY CLAIMS OF INFRINGEMENT, AND YOU ARE RESPONSIBLE FOR OBTAINING ANY RIGHTS YOU MAY REQUIRE FOR YOUR IMPLEMENTATION. XILINX EXPRESSLY DISCLAIMS ANY WARRANTY WHATSOEVER WITH RESPECT TO THE ADEQUACY OF THE IMPLEMENTATION, INCLUDING BUT NOT LIMITED TO ANY WARRANTIES OR REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE FROM CLAIMS OF INFRINGEMENT, IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

(c) Copyright 2003 Xilinx Inc. All rights reserved.

# Xilinx Device Drivers <u>Driver Summary</u> <u>Copyright</u> Main Page Data Structures File List Data Fields Globals

## **Xilinx Device Drivers Data Structures**

Here are the data structures with brief descriptions:

| XAtmc            |

|------------------|

| XAtmc_Config     |

| XAtmc_Stats      |

| XEmac            |

| XEmac_Config     |

| XEmac_Stats      |

| XEmc             |

| XEmc_Config      |

| XENV_TIME_STAMP  |

| XFlash_Config    |

| XFlashGeometry   |

| XFlashPartID     |

| XFlashProgCap    |

| XFlashProperties |

| XFlashTag        |

| XFlashTiming     |

| XGemac           |

| XGemac_Config    |

| XGemac_HardStats |

| XGemac_SoftStats |

| XGpio            |

| XHdlc            |

| XHdlc_Config     |

| XHdlc_Stats      |

| 1111010_Dtuto    |

| XIic                 |

|----------------------|

| XIic_Config          |

| XIicStats            |

| XIntc                |

| XIntc_Config         |

| XOpb2Plb             |

| XOpb2Plb_Config      |

| XOpbArb              |

| XOpbArb_Config       |

| XPci                 |

| XPciError            |

| XPlb2Opb             |

| XPlb2Opb_Config      |

| XPlbArb              |

| XPlbArb_Config       |

| XSpi                 |

| XSpi_Config          |

| XSpi_Stats           |

| XSysAce              |

| XSysAce_CFParameters |

| XSysAce_Config       |

| XTmrCtr              |

| XTmrCtr_Config       |

| XTmrCtrStats         |

| XUartLite            |

| XUartLite_Buffer     |

| XUartLite_Config     |

| XUartLite_Stats      |

| XUartNs550           |

| XUartNs550_Config    |

| XUartNs550Format     |

XUartNs550Stats

XWdtTb

XWdtTb\_Config

Generated on 30 Sep 2003 for Xilinx Device Drivers

# **Xilinx Device Drivers File List**

Here is a list of all documented files with brief descriptions:

| Tiere is a fist of all documented files with offer de |

|-------------------------------------------------------|

| atmc/v1_00_c/src/xatmc.c                              |

| atmc/v1_00_c/src/xatmc.h                              |

| atmc/v1_00_c/src/xatmc_cfg.c                          |

| atmc/v1_00_c/src/xatmc_g.c                            |

| atmc/v1_00_c/src/xatmc_i.h                            |

| atmc/v1_00_c/src/xatmc_l.c                            |

| atmc/v1_00_c/src/xatmc_l.h                            |

| common/v1_00_a/src/xbasic_types.c                     |

| common/v1_00_a/src/xbasic_types.h                     |

| common/v1_00_a/src/xenv.h                             |

| common/v1_00_a/src/xenv_linux.h                       |

| common/v1_00_a/src/xenv_none.h                        |

| common/v1_00_a/src/xenv_vxworks.h                     |

| common/v1_00_a/src/xparameters.h                      |

| common/v1_00_a/src/xstatus.h                          |

| common/v1_00_a/src/xutil.h                            |

| common/v1_00_a/src/xutil_memtest.c                    |

| cpu/v1_00_a/src/xio.c                                 |

| cpu/v1_00_a/src/xio.h                                 |

| cpu_ppc405/v1_00_a/src/xio.c                          |

| cpu_ppc405/v1_00_a/src/xio.h                          |

| cpu_ppc405/v1_00_a/src/xio_dcr.c                      |

| cpu_ppc405/v1_00_a/src/xio_dcr.h                      |

| emac/v1_00_d/src/xemac.c                              |

|                                                       |

```

emac/v1 00 d/src/xemac.h

emac/v1_00_d/src/xemac_g.c

emac/v1_00_d/src/xemac_i.h

emac/v1_00_d/src/xemac_intr.c

emac/v1 00 d/src/xemac intr dma.c

emac/v1 00 d/src/xemac intr fifo.c

emac/v1_00_d/src/xemac_l.c

emac/v1 00 d/src/xemac l.h

emac/v1 00 d/src/xemac multicast.c

emac/v1_00_d/src/xemac_options.c

emac/v1_00_d/src/xemac_phy.c

emac/v1 00 d/src/xemac polled.c

emac/v1 00 d/src/xemac selftest.c

emac/v1_00_d/src/xemac_stats.c

emaclite/v1_00_a/src/xemaclite_l.c

emaclite/v1 00 a/src/xemaclite l.h

emc/v1_00_a/src/xemc.c

emc/v1 00 a/src/xemc.h

emc/v1_00_a/src/xemc_g.c

emc/v1_00_a/src/xemc_i.h

emc/v1 00 a/src/xemc l.h

emc/v1_00_a/src/xemc_selftest.c

flash/v1 00 a/src/xflash.c

flash/v1_00_a/src/xflash.h

flash/v1_00_a/src/xflash_cfi.c

flash/v1 00 a/src/xflash cfi.h

flash/v1 00 a/src/xflash g.c

flash/v1 00 a/src/xflash geometry.c

flash/v1_00_a/src/xflash_geometry.h

flash/v1_00_a/src/xflash_intel.c

flash/v1 00 a/src/xflash intel.h

```

```

flash/v1 00 a/src/xflash intel l.c

flash/v1 00 a/src/xflash intel l.h

flash/v1_00_a/src/xflash_properties.h

gemac/v1_00_d/src/xgemac.c

gemac/v1_00_d/src/xgemac.h

gemac/v1_00_d/src/xgemac_control.c

gemac/v1_00_d/src/xgemac_g.c

gemac/v1_00_d/src/xgemac_i.h

gemac/v1_00_d/src/xgemac_intr.c

gemac/v1 00 d/src/xgemac intr dma.c

gemac/v1_00_d/src/xgemac_intr_fifo.c

gemac/v1_00_d/src/xgemac_l.h

gemac/v1 00 d/src/xgemac multicast.c

gemac/v1_00_d/src/xgemac_options.c

gemac/v1_00_d/src/xgemac_polled.c

gemac/v1_00_d/src/xgemac_selftest.c

gemac/v1_00_d/src/xgemac_stats.c

gpio/v1 00 a/src/xgpio.c

gpio/v1_00_a/src/xgpio.h

gpio/v1_00_a/src/xgpio_extra.c

gpio/v1_00_a/src/xgpio_g.c

gpio/v1_00_a/src/xgpio_i.h

gpio/v1_00_a/src/xgpio_l.h

gpio/v1_00_a/src/xgpio_selftest.c

hdlc/v1_00_a/src/xhdlc.c

hdlc/v1 00 a/src/xhdlc.h

hdlc/v1_00_a/src/xhdlc_dmasg.c

hdlc/v1_00_a/src/xhdlc_g.c

hdlc/v1_00_a/src/xhdlc_i.h

hdlc/v1 00 a/src/xhdlc l.c

hdlc/v1_00_a/src/xhdlc_l.h

```

| hdlc/v1_00_a/src/xhdlc_options.c    |

|-------------------------------------|

| hdlc/v1_00_a/src/xhdlc_selftest.c   |

| hdlc/v1_00_a/src/xhdlc_stats.c      |

| iic/v1_01_c/src/xiic.c              |

| iic/v1_01_c/src/xiic.h              |

| iic/v1_01_c/src/xiic_g.c            |

| iic/v1_01_c/src/xiic_i.h            |

| iic/v1_01_c/src/xiic_intr.c         |

| iic/v1_01_c/src/xiic_l.c            |

| iic/v1_01_c/src/xiic_l.h            |

| iic/v1_01_c/src/xiic_master.c       |

| iic/v1_01_c/src/xiic_multi_master.c |

| iic/v1_01_c/src/xiic_options.c      |

| iic/v1_01_c/src/xiic_selftest.c     |

| iic/v1_01_c/src/xiic_slave.c        |

| iic/v1_01_c/src/xiic_stats.c        |

| intc/v1_00_b/src/xintc.c            |

| intc/v1_00_b/src/xintc.h            |

| intc/v1_00_b/src/xintc_g.c          |

| intc/v1_00_b/src/xintc_i.h          |

| intc/v1_00_b/src/xintc_intr.c       |

| intc/v1_00_b/src/xintc_l.c          |

| intc/v1_00_b/src/xintc_l.h          |

| intc/v1_00_b/src/xintc_lg.c         |

| intc/v1_00_b/src/xintc_options.c    |

| intc/v1_00_b/src/xintc_selftest.c   |

| opb2plb/v1_00_a/src/xopb2plb.c      |

| opb2plb/v1_00_a/src/xopb2plb.h      |

| opb2plb/v1_00_a/src/xopb2plb_g.c    |

| opb2plb/v1_00_a/src/xopb2plb_i.h    |

| opb2plb/v1_00_a/src/xopb2plb_l.h    |

```

opb2plb/v1_00_a/src/xopb2plb_selftest.c

opbarb/v1_02_a/src/xopbarb.c

opbarb/v1_02_a/src/xopbarb.h

opbarb/v1_02_a/src/xopbarb_g.c

opbarb/v1_02_a/src/xopbarb_l.h

pci/v1_00_a/src/xpci.h

pci/v1_00_a/src/xpci_config.c

pci/v1_00_a/src/xpci_g.c

pci/v1_00_a/src/xpci_intr.c

pci/v1_00_a/src/xpci_l.h

pci/v1_00_a/src/xpci_selftest.c

pci/v1_00_a/src/xpci_v3.c

plb2opb/v1_00_a/src/xplb2opb.c

plb2opb/v1_00_a/src/xplb2opb.h

plb2opb/v1_00_a/src/xplb2opb_g.c

plb2opb/v1_00_a/src/xplb2opb_i.h

plb2opb/v1_00_a/src/xplb2opb_l.h

plb2opb/v1 00 a/src/xplb2opb selftest.c

plbarb/v1_01_a/src/xplbarb.c

plbarb/v1_01_a/src/xplbarb.h

plbarb/v1_01_a/src/xplbarb_g.c

plbarb/v1 01 a/src/xplbarb i.h

plbarb/v1_01_a/src/xplbarb_l.h

plbarb/v1_01_a/src/xplbarb_selftest.c

rapidio/v1_00_a/src/xrapidio_l.c

rapidio/v1 00 a/src/xrapidio l.h

spi/v1_00_b/src/xspi.c

spi/v1_00_b/src/xspi.h

spi/v1_00_b/src/xspi_g.c

spi/v1_00_b/src/xspi_i.h

spi/v1_00_b/src/xspi_l.h

```

```

spi/v1_00_b/src/xspi_options.c

spi/v1_00_b/src/xspi_selftest.c

spi/v1_00_b/src/xspi_stats.c

sysace/v1_00_a/src/xsysace.c

sysace/v1_00_a/src/xsysace.h

sysace/v1 00 a/src/xsysace compactflash.c

sysace/v1_00_a/src/xsysace_g.c

sysace/v1_00_a/src/xsysace_intr.c

sysace/v1_00_a/src/xsysace_jtagcfg.c

sysace/v1_00_a/src/xsysace_l.c

sysace/v1_00_a/src/xsysace_l.h

sysace/v1_00_a/src/xsysace_selftest.c

tmrctr/v1 00 b/src/xtmrctr.c

tmrctr/v1_00_b/src/xtmrctr.h

tmrctr/v1_00_b/src/xtmrctr_g.c

tmrctr/v1 00 b/src/xtmrctr i.h

tmrctr/v1_00_b/src/xtmrctr_intr.c

tmrctr/v1 00 b/src/xtmrctr l.c

tmrctr/v1 00 b/src/xtmrctr l.h

tmrctr/v1_00_b/src/xtmrctr_options.c

tmrctr/v1 00 b/src/xtmrctr selftest.c

tmrctr/v1_00_b/src/xtmrctr_stats.c

uartlite/v1 00 b/src/xuartlite.c

uartlite/v1_00_b/src/xuartlite.h

uartlite/v1_00_b/src/xuartlite_g.c

uartlite/v1 00 b/src/xuartlite i.h

uartlite/v1_00_b/src/xuartlite_intr.c

uartlite/v1 00 b/src/xuartlite l.c

uartlite/v1 00 b/src/xuartlite l.h

uartlite/v1_00_b/src/xuartlite_selftest.c

uartlite/v1 00 b/src/xuartlite stats.c

```

```

uartns550/v1_00_b/src/xuartns550.c

uartns550/v1_00_b/src/xuartns550.h

uartns550/v1_00_b/src/xuartns550_format.c

uartns550/v1_00_b/src/xuartns550_g.c

uartns550/v1 00 b/src/xuartns550 i.h

uartns550/v1 00 b/src/xuartns550 intr.c

uartns550/v1_00_b/src/xuartns550_l.c

uartns550/v1_00_b/src/xuartns550_l.h

uartns550/v1_00_b/src/xuartns550_options.c

uartns550/v1_00_b/src/xuartns550_selftest.c

uartns550/v1_00_b/src/xuartns550_stats.c

wdttb/v1_00_b/src/xwdttb.c

wdttb/v1 00 b/src/xwdttb.h

wdttb/v1_00_b/src/xwdttb_g.c

wdttb/v1_00_b/src/xwdttb_i.h

wdttb/v1_00_b/src/xwdttb_l.h

wdttb/v1_00_b/src/xwdttb_selftest.c

```

Generated on 30 Sep 2003 for Xilinx Device Drivers

# Xilinx Device Drivers <u>Driver Summary</u> <u>Copyright</u> Main Page Data Structures File List Data Fields Globals

# Xilinx Device Drivers Data Fields

# $\underline{a} | \underline{b} | \underline{c} | \underline{d} | \underline{e} | \underline{f} | \underline{h} | \underline{i} | \underline{1} | \underline{m} | \underline{n} | \underline{p} | \underline{r} | \underline{s} | \underline{t} | \underline{u} | \underline{v} | \underline{w} | \underline{x}$

Here is a list of all documented struct and union fields with links to the structures/unions they belong to:

#### - a -

• AbsoluteBlock : XFlashGeometry

AbsoluteOffset : XFlashGeometry

AckBeforeService : XIntc\_Config

• ArbitrationLost : XIicStats

• AtmcInterrupts : **XAtmc\_Stats**

## - b -

- BaseAddr : XWdtTb\_Config, XFlash\_Config

- BaseAddress: XUartNs550\_Config, XTmrCtr\_Config, XSysAce\_Config, XSpi\_Config, XPlbArb\_Config, XPlb2Opb\_Config, XOpbArb\_Config, XOpb2Plb\_Config, XIntc\_Config, XIic\_Config, XHdlc\_Config, XGemac\_Config, XFlashGeometry, XEmac\_Config, XAtmc\_Config

- BaudRate: XUartNs550Format, XUartLite\_Config

- BufferSize : XSysAce\_CFParameters

- BufferType : XSysAce\_CFParameters

- BusBusy: XIicStats

- BytesTransferred : XSpi\_Stats

#### - C -

- Capabilities : XSysAce\_CFParameters

- CharactersReceived : XUartNs550Stats, XUartLite\_Stats

- CharactersTransmitted: XUartNs550Stats, XUartLite\_Stats

- CommandSet: XFlashPartID

- CurNumCylinders : XSysAce\_CFParameters

- CurNumHeads : XSysAce\_CFParameters

- CurSectorsPerCard : XSysAce\_CFParameters

- CurSectorsPerTrack : XSysAce\_CFParameters

## - d -

- DataBits : XUartNs550Format, XUartLite\_Config

- DblWord : XSysAce\_CFParameters

- DeviceID : XFlashPartID

- DeviceId: XWdtTb\_Config, XUartNs550\_Config, XUartLite\_Config, XTmrCtr\_Config, XSysAce\_Config, XSpi\_Config, XPlbArb\_Config, XPlb2Opb\_Config, XOpbArb\_Config, XOpb2Plb\_Config, XIntc\_Config, XIic\_Config, XHdlc\_Config, XGemac\_Config, XFlash\_Config, XEmc\_Config, XEmac\_Config, XAtmc\_Config

- DeviceSize : **XFlashGeometry**

- DmaErrors : XHdlc\_Stats, XGemac\_SoftStats, XEmac\_Stats, XAtmc\_Stats

- DmaMode : XSysAce\_CFParameters

- DmaRegBaseAddr : XPci

- DmaType : **XPci**

#### - e -

- EmacInterrupts : **XGemac\_SoftStats**, **XEmac\_Stats**

- EraseBlock\_Ms: XFlashTiming

- EraseChip\_Ms: XFlashTiming

- EraseQueueSize : XFlashProgCap

# - f -

- FifoErrors: XHdlc\_Stats, XGemac\_SoftStats, XEmac\_Stats, XAtmc\_Stats

- FwVersion : XSysAce\_CFParameters

• Has10BitAddr : **XIic\_Config**

• HasCounters : XGemac\_Config, XEmac\_Config

• HasFifos : **XSpi\_Config**

• HasGmii : XGemac\_Config

• HasMii : **XEmac\_Config**

• HdlcInterrupts : XHdlc\_Stats

## - i -

• IicInterrupts : XIicStats

• InputClockHz: XUartNs550\_Config

• Interrupts : **XTmrCtrStats**

• IpIfDmaConfig: XHdlc\_Config, XGemac\_Config, XEmac\_Config, XAtmc\_Config

• IsError : **XPciError**

• IsReady : XPci

# - | -

• LbaSectors : XSysAce\_CFParameters

• LocalBusReadAddr : **XPciError**

• LocalBusReason : **XPciError**

• LocalBusWriteAddr: XPciError

#### - m -

• ManufacturerID : XFlashPartID

• MaxSectors : XSysAce\_CFParameters

• MemoryLayout : **XFlashGeometry**

• ModeFaults : **XSpi\_Stats**

$\bullet \quad Model No: {\bf XSysAce\_CFParameters}$

• ModemInterrupts : XUartNs550Stats

• MultipleSectors : XSysAce\_CFParameters

#### - n -

• NumBanks : **XEmc\_Config**

• Number : **XFlashGeometry**

- NumBlocks : **XFlashGeometry**

- NumBytesPerSector : XSysAce\_CFParameters

- NumBytesPerTrack : XSysAce\_CFParameters

- NumCylinders : XSysAce\_CFParameters

- NumEccBytes : XSysAce\_CFParameters

- NumEraseRegions : XFlashGeometry

- NumHeads : XSysAce\_CFParameters

- NumInterrupts : **XSpi\_Stats**

- NumMasters: XPlbArb\_Config, XPlb2Opb\_Config, XOpbArb\_Config

- NumParts : **XFlash\_Config**

- NumSectorsPerCard : XSysAce\_CFParameters

- NumSectorsPerTrack : XSysAce\_CFParameters

- NumSlaveBits : **XSpi\_Config**

# - p -

- Parity: XUartNs550Format

- ParityOdd: XUartLite\_Config

- PartID : XFlashProperties

- PartMode : XFlash\_Config

- PartWidth : **XFlash\_Config**

- PciReadAddr : XPciError

- PciReason : **XPciError**

- PciSerrReadAddr : **XPciError**

- PciSerrReason : XPciError

- PciSerrWriteAddr: XPciError

- PciWriteAddr : XPciError

- PioMode : XSysAce\_CFParameters

- PowerDesc : XSysAce\_CFParameters

- ProgCap : XFlashProperties

#### - r -

- ReceiveBreakDetected : XUartNs550Stats

- ReceiveFifoSize : XHdlc\_Config

- ReceiveFramingErrors : XUartNs550Stats, XUartLite\_Stats

- ReceiveInterrupts : XUartNs550Stats, XUartLite\_Stats

- ReceiveOverrunErrors : XUartNs550Stats, XUartLite\_Stats

- ReceiveParityErrors : XUartNs550Stats, XUartLite\_Stats

- Recv1024\_MaxByte : **XGemac\_HardStats**

- Recv128\_255Byte : **XGemac\_HardStats**

- Recv256\_511Byte : **XGemac\_HardStats**

- Recv512\_1023Byte : **XGemac\_HardStats**

- Recv64Byte : **XGemac\_HardStats**

- Recv65\_127Byte : **XGemac\_HardStats**

- RecvAbortedFrames : XHdlc Stats

- RecvAlignmentErrors : **XHdlc\_Stats**, **XEmac\_Stats**

- RecvBadOpcode : **XGemac\_HardStats**

- RecvBroadcast : XGemac HardStats

- RecvBytes: XIicStats, XHdlc\_Stats, XGemac\_HardStats, XEmac\_Stats

- RecvCells : **XAtmc\_Stats**

- RecvCollisionErrors : XEmac Stats

- RecvControl: XGemac HardStats

- RecvFcs : XGemac\_HardStats

- RecvFcsErrors: XHdlc\_Stats, XGemac\_SoftStats, XEmac\_Stats

- RecvFragment : XGemac\_HardStats

- RecvFrames: XHdlc\_Stats, XGemac\_HardStats, XEmac\_Stats

- RecvHecErrors : **XAtmc\_Stats**

- RecvInterrupts: XIicStats, XHdlc\_Stats, XGemac\_SoftStats, XEmac\_Stats,

XAtmc\_Stats

- RecvLengthFieldErrors : XGemac\_SoftStats, XEmac\_Stats

- RecvLengthRange : **XGemac\_HardStats**

- RecvLong : XGemac\_HardStats

- RecvLongCells : **XAtmc\_Stats**

- RecvLongErrors : **XGemac\_SoftStats**, **XEmac\_Stats**

- RecvMissedFrameErrors : XEmac\_Stats

- RecvMulticast : **XGemac\_HardStats**

- RecvOverrunErrors : XHdlc\_Stats, XGemac\_SoftStats, XEmac\_Stats

- RecvOverruns : XSpi\_Stats

- RecvParityErrors : **XAtmc\_Stats**

- RecvPause : XGemac\_HardStats

- RecvShort : XGemac\_HardStats

- RecvShortCells : XAtmc\_Stats

- RecvShortErrors : XEmac\_Stats

- RecvSlotLengthErrors : XGemac\_SoftStats

- RecvUnderrunErrors : XGemac\_SoftStats, XEmac\_Stats

- RecvUnexpectedHeaders : **XAtmc\_Stats**

- RecvVlan : XGemac\_HardStats

- RegBaseAddr : XUartLite\_Config, XPci, XEmc\_Config

- RepeatedStarts : XIicStats

#### **- S -**

- SecurityStatus : XSysAce\_CFParameters

- SendBytes : XIicStats

- SendInterrupts : XIicStats

- SerialNo : XSysAce\_CFParameters

- Signature : XSysAce\_CFParameters

- Size: XFlashGeometry

- SlaveModeFaults : XSpi\_Stats

- SlaveOnly : XSpi\_Config

- StatusInterrupts : **XUartNs550Stats**

- StopBits: XUartNs550Format

## - t -

- TimeMax : XFlashProperties

- TimeTypical : XFlashProperties

- TotalInterrupts : **XGemac\_SoftStats**

- TotalIntrs : **XEmac\_Stats**

- TranslationValid : XSysAce\_CFParameters