# BSIM4 High-Frequency Model Verification For 0.13 µm RF-CMOS Technology

M.T. Yang<sup>1</sup>, Patricia P.C. Ho<sup>1</sup>, C.K. Lin<sup>1</sup>, T.J. Yeh<sup>1</sup>, Y.J. Wang<sup>1</sup>, Sorin P. Voinigescu<sup>2</sup>, Mihai Tazlauanu<sup>3</sup>, Y.T. Chia<sup>1</sup>, K. L. Young<sup>1</sup>

<sup>1</sup>TSMC, 9 Creation Rd. 1, Science-Based Industrial Park, Hsin-Chu, Taiwan 300-77, R.O.C., <sup>2</sup>ECE Department, University of Toronto, 10 King's College Rd. Toronto, ON, M5S 3G4, Canada, <sup>3</sup>Quake Technologies Inc., 80 Hines Rd. Ottawa, ON, K2K 2T8 Canada. Tel: +886-3-5781688 ext. 3592, Fax: +886-3-6668166, E-mail: mtyang@tsmc.com

Abstract — A compact model capable of simulating both DC and RF characteristics is highly desirable. This work is the first report of an extensive experimental evaluation of the accuracy of the BSIM4 model at high frequencies using a 0.13 µm RF-CMOS process. The accuracy of the model is verified on both N-channel and P-channel devices through small-signal S-parameter measurements up to 50 GHz, 1/f noise measurements, and noise figure measurements in the 2-GHz to 6-GHz range.

Index Terms — 0.13μm, BSIM4, Compact model, CMOS, MS/RF.

### I. Introduction

As the cutoff frequency (fT) of deep sub-micron MOSFETs now exceeds 130 GHz, many high-speed and microwave ICs are likely to be implemented in CMOS technology. Coupled with the low cost, high level of integration and easy access to technology, these high fT values open the door for highly integrated full CMOS solutions for next-generation wireless applications. The availability of a compact MOS model that is valid for a broad range of bias conditions and operating frequencies is essential in the development of microwave circuits using MOS transistors. Such a model is critical for accurate design of high-frequency integrated circuits with 'first pass' success. Unfortunately, most of commercially available MOS transistor models are not particularly suited for high frequencies. Although the BSIM3v3 model has been extensively validated in DC and low-frequency measurements, not much attention has been paid to high-frequency modeling. Recent papers have extended the validity of BSIM3v3 to RF applications by adding a complicated substrate network and a gate resistance to the BSIM3v3 core [1].

In the development of foundry technologies, a compact model capable of simulating both DC and RF characteristics is highly desirable. BSIM4 features several major improvements and additions over BISM3v3 and was developed to explicitly address deficiencies in modeling sub-0.13  $\mu m$  CMOS transistors and for RF and

high-speed circuit simulation [2]. It includes three critical modules for accurate high-frequency design: the intrinsic-input resistance (IIR) model, the substrate resistance network model, and the holistic thermal noise model. So far only the DC performance of the BSIM4 model has been investigated [3]. This work is the first report of an extensive experimental evaluation of the accuracy of the BSIM4 model at high frequencies.

This paper is organized as follows: Section II describes the CMOS technology for mixed-signal and RF system-on-a-chip (MS/RF SOC) applications. Section III presents the BSIM4 high-frequency model verification and experimental results. Finally, concluding remarks are summarized in section IV.

# II. CMOS TECHNOLOGY FOR MS/RF SOC

N-channel and P-channel MOSFETs were fabricated in a 0.13 µm RF CMOS process with full Cu damascene metallization. The main features of this process flow were reported in [4]. In addition to standard CMOS logic technology components and embedded memory cells, passive components such as resistors, capacitors, inductors, varactors, and transmission lines, as well as adequate on-chip electrical noise-isolation (DNW), are mandatory ingredients in support of MS/RF SOC. A more detailed description of all the available devices in TSMC's 0.13 µm RF CMOS process can be found in [5] and [6].

The BSIM4 model parameters were extracted using on-wafer DC and S-parameter measurements performed with GSG probe. A two-step series-shunt de-embedding of pad and interconnect parasitics was employed.

# III. BSIM4 MODEL VERIFICATION

## A. DC-IV Characteristics Verification

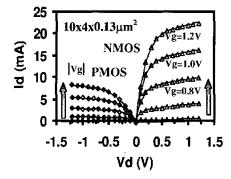

Fig. 1 shows the measured and simulated output characteristics of N- and P- channel 0.13  $\mu m$  MOSFETs.

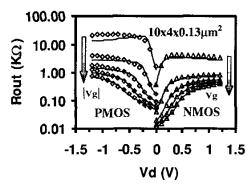

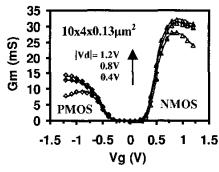

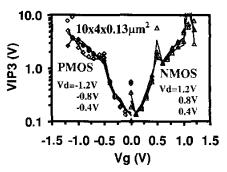

The modeled and measured transconductance and output resistance are compared in Figs. 2 and 3, respectively. Furthermore, the VIP3, important in power amplifier linearity simulations, is evaluated in Fig. 4. The excellent match between measurements and simulations is attributed to the improvements in the BSIM4 mobility and physics-based output resistance models. Both are essential in accurately predicting high-frequency gain and output power behavior.

Fig. 1. Output characteristic fitting of N-( $\Delta$ )/P-( $\Delta$ )MOS with  $10x4x0.13~\mu m^2$  at |Vg|=0.4, 0.6, 0.8, 1.0 and 1.2V

Fig. 2. Small-signal output resistance fitting of N-( $\Delta$ )/P-( $\delta$ )MOS with  $10x4x0.13 \mu m^2$  at |Vg|=0.4, 0.6, 0.8, 1.0 and 1.2V.

Fig. 3. Small-signal transconductance fitting of N-( $\Delta$ )/P-( $\Diamond$ )MOS with  $10x4x0.13 \ \mu m^2$  at |Vd |=0.4, 0.8 and 1.2V.

Fig. 4. The VIP3 ( $\sqrt{24 \text{xgm}/|\text{gm}_3|}$ ) fitting of N-( $\Delta$ )/P-( $\Diamond$ ) MOS with  $10x4x0.13 \,\mu\text{m}^2$  at |Vd| = 0.4, 0.8 and 1.2V.

### B. HF Characteristics Verification

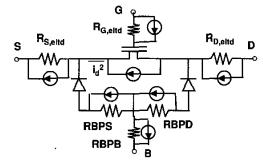

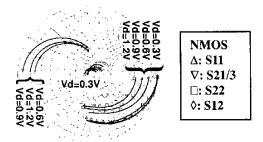

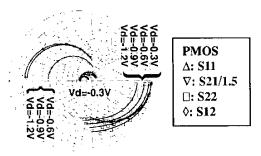

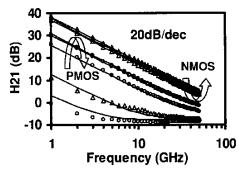

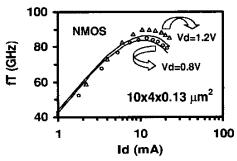

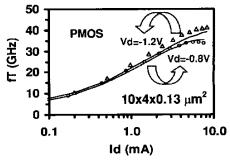

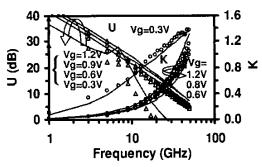

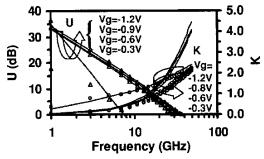

Next, the measured and simulated S-parameters of 0.13µm RF CMOS transistors were compared at different bias points and frequencies ranging from 1GHz up to 50 GHz. The device has a multi-fingered gate structure with a unit width of 4µm and the bulk and source nodes are grounded. Fig. 5 depicts the BSIM4 equivalent circuit used in the RF and noise analysis. The model parameters R<sub>D/S,elid</sub> were determined from DC-IV measurements. R<sub>Geltd</sub> and RBPD/S/B, which are associated with the gate electrode and lossy Si substrate, respectively, were extracted from the real part of the input admittance YII and of the output admittance Y22. Figs. 6 and 7 show excellent S-parameter fitting for both N- and P-MOS devices under various bias conditions, thus validating the model and the parameter extraction methodology. The RF and noise related model selectors and their corresponding extracted parameter values, are depicted in Table I. Several RF figures of merit (FOM) such as current gain H21, fT, Unilateral power gain U, and stability factor K are also analyzed and shown in Figs. 8 through 12. In all cases good agreement between measurements and simulations has been demonstrated.

Fig. 5. The BSIM4 equivalent circuit used for DC, RF and Noise simulation. Input intrinsic resistance (IIR), substrate resistance network and holistic thermal noise are integrated internally.

Fig. 6. S-parameter fitting of NMOS at Vd=0.8V; Vg=0.3, 0.6, 0.9 and 1.2V with frequency sweep from 1GHz to 50GHz.

Fig. 7. S-parameter fitting of PMOS at Vd=-0.8V; Vg=-0.3, -0.6, -0.9 and -1.2V with frequency sweep from 1GHz to 50GHz.

TABLE I

SUMMARY OF MODEL SELECTORS AND EXTRACTED

PARAMETERS

| Model Selector | Fitting Parameter                                |                                                |

|----------------|--------------------------------------------------|------------------------------------------------|

|                | NMOS                                             | PMOS                                           |

| RGATEMOD=1     | RSHG=13; NF=10                                   | RSHG=30; NF=10                                 |

| RDSMOD=0       | NRD=19; RSH=67m                                  | NRS=22; RSH= 122m                              |

| PERMOD=0       | ASeff=25p; PSeff=13u                             | ADeff=21p; PDeff=10u                           |

| RBODYMOD=1     | RBPS=RBPD=1; RBPB=47.5                           | RBPS=RBPD=1.5; RBPB=36                         |

| FNOIMOD=1      | NOIA=2E43; NOIB=4E26;<br>NOIC=5E8; EF=1;EM=4.1E7 | NOIA=2E40; NOIB=2E24;<br>NOIC=6E8; EF=1;EM=4E6 |

| TNOIMOD=1      | TNOIA=1.5E6; TNOIB=3.5E6                         | TNOIA=1.5E6;TNOIB=3.5E6                        |

Fig. 8. Current gain (H21) frequency response fitting of  $N-(\Delta)/P-(\diamond)MOS$  at |Vd|=0.8V; |Vg|=0.3, 0.6, 0.9 and 1.2V.

Fig. 9. Current gain cutoff frequency (fT) as function of the drain current fitting of NMOS at Vd =0.8V (o) and 1.2V( $\Delta$ ).

Fig. 10. Current gain cutoff frequency (fT) as function of the drain current fitting of PMOS at Vd =-0.8V (o) and -1.2V( $\Delta$ ).

Fig. 11. Power gain (U;  $\Delta$ ) and stability factor (K; o) frequency response fitting of NMOS at Vd=0.8V; Vg=0.3, 0.6, 0.9 and 1.2V.

Fig. 12. Power gain (U;  $\Delta$ ) and stability factor (K; o) frequency response fitting of PMOS at Vd=-0.8V; Vg=-0.3, -0.6, -0.9 and -1.2V.

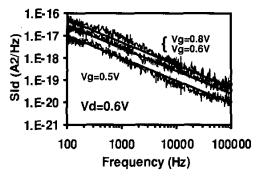

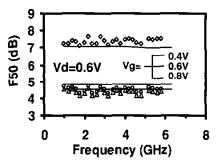

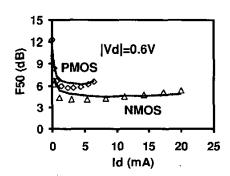

# C. Noise Characteristics Verification

Finally, the ability of the model to accurately capture low-frequency flicker noise and high-frequency thermal noise was assessed. The former is demonstrated in Fig. 13 at various biases from 100 Hz up to 100 kHz with BSIM4 noise model to immunity from discrepancy for multiple identical devices connected in parallel. The measured and simulated noise figure for a 500hm signal source impedance is shown in Fig. 14 as a function of frequency, and as a function of bias at 4.8 GHz in Fig.15.

Fig. 13. Low-frequency 1/f noise (Sid) fitting of NMOS with  $10x0.18 \mu m^2$  at Vd =0.6V; Vg=0.5V, 0.6V and 0.8V.

Fig. 14. HF thermal noise with 50  $\Omega$  termination (F50) fitting of NMOS at Vd=0.6V; Vg=0.4 ( $\Diamond$ ), 0.6( $\wp$ ), and 0.8V( $\Delta$ ).

Fig. 15. High-frequency thermal noise with 50  $\Omega$  termination (F50) fitting of N-( $\Delta$ )/P-( $\delta$ )MOS at |Vd |=0.6V.

### V. CONCLUSION

The BSIM4 high-speed/RF Spice model featuring distributed gate and substrate resistance was evaluated and verified for the first time in terms of 0.13 µm RF CMOS. The measured and modeled characteristics of DC-IV. small-signal gm and gds, high-frequency FOMs, and noise of 1/f and F50 with excellent agreement have been demonstrated. The improvements in the BSIM4 mobility and physics-based output resistance models facilitate the mimic of linearity and output impedance simulations. To yield correct simulation result we have modeled the access source/drain resistance in terms of absorbed-resistance approach instead of with lumped-resistance approach. It is necessary to include R<sub>Geltd</sub> to account for the NQS effect due to the convergence of simulation NQS deficiency, which is important in accurate prediction of bandwidth. As to the substrate network, we have observed that a simple 3-R T-shape resistive network is good enough for output impedance model. Issue for scalable parameter for rapid growth in RF circuit applications should be improved. The ability of the model to accurately capture low-frequency Flicker noise and high-frequency thermal noise was also assessed. A unified Flicker noise model and Holistic thermal noise model improvement the excess noise associated with short-channel effect and immunity from the inaccurate for multiple identical devices as well.

## REFERENCES

- [1] W. Liu et al., "RF MOSFET modeling accounting for distributed substrate and channel resistances with emphasis on the BSIM3v3 SPICE model." in *IEEE Electron Devices Meeting Tech. Dig.*, pp. 309-312, Dec. 1997.

- [2] http://www-device.eecs.berkeley.edu

- [3] D. Souil et al.,"BSIM4.1 DC Parameter Extraction on 50nm n-pMOSFETs" in *Proc. IEEE 2002 ICMTS*, Vol. 15, pp.115-119, 2002.

- [4] K.K. Young et al., "A 0.13 μm CMOS technology with 193nm lithography and Cu/low-k for high performance application," in *IEDM Tech. Dig.*, 2000, pp. 563-566.

- [5] C.S. Chang et al., "Extended 0.13 μm CMOS technology for the ultra high-speed and MS/RF application segments." in Proc. IEEE VLSI Technology Symp., 2002, pp. 68-69.

- [6] C.H. Lin et al., "State-of-the-art RF/Analog Foundry technology." in Proc. IEEE Bipolar/BiCMOS Circuits and Technology Meeting, 2002, pp.73-79.