High Speed Chip to Chip Interfaces

Introduction

The data rates which can be processed by integrated communication systems are increasing as CMOS process technologies scale. Providing interfaces that can keep up with the processing speed of the chip is becoming increasingly difficult. Due to the bandwidth limitations of the IC packaging and interconnect, it is inevitable that more sophisticated transceivers be developed for this purpose.

Objective

Power-efficient, robust, and low-cost chip-to-chip interfaces are sought to meet the needs of high-performance computers and high-bandwidth communication systems.

Research

Channel Modeling

A simple scalable model for chip-to-chip communication channels may be developed using a cascade of 2-port network parameters. For instance, a typical channel is shown below with packaging, mismatched terminations, and lossy differential microstrip interconnect.

A Matlab model for this channel is developed and the frequency response for various lengths is shown below.

I have developed a set of Matlab functions to help generate and manipulate ABCD matrices for simulating cascaded two-port electrical networks such as transmission lines with discontinuities. I have found this to be particularly useful for modeling chip-to-chip links. Included in the zip file below are the functions, a README file, and a M-file that uses the functions to generate a sample channel model.

MatlabABCD.zip [approx 500 kb]

Crosstalk

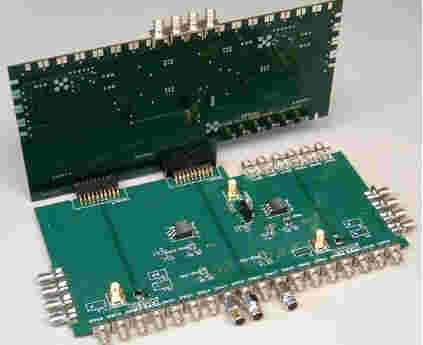

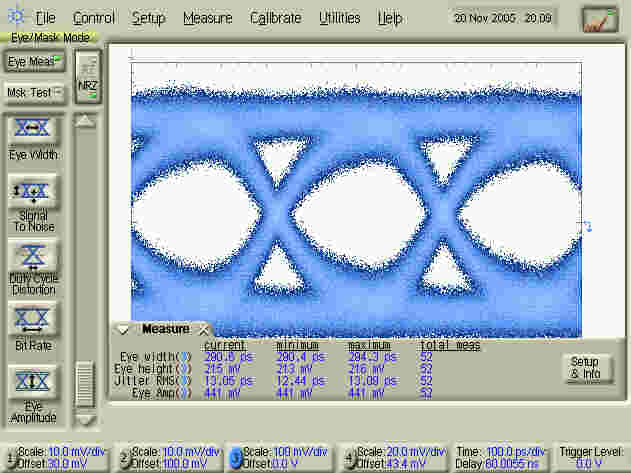

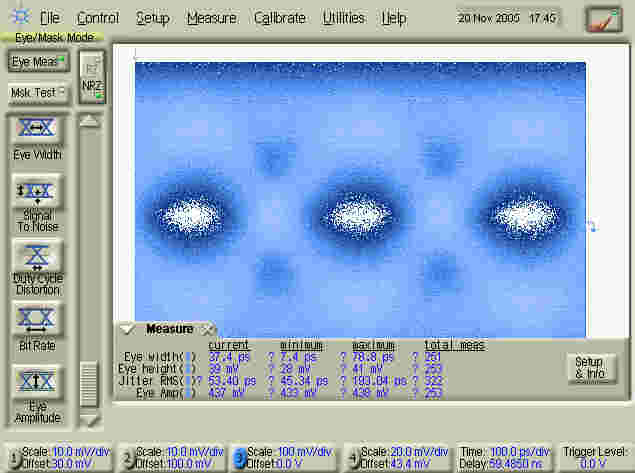

A major impairment on parallel chip-to-chip buses is crosstalk from adjacent traces. Below are eye diagrams measured on a real PCB at 2.7 Gb/s, without and with crosstalk. Clearly, some form of crosstalk mitigation is required. This is an ongoing research area.

Equalization

Several techniques for equalization are currently in use and under development including pre-emphasis, linear equalization in both discrete- and continuous-time, and decision feedback equalization. Clearly, adding complexity will improve performance, but our research in this area is aimed at understanding the tradeoffs between these various approaches including realistic circuit implementation issues. Ongoing projects include programmable filter design in the GHz range and hardware-efficient adaptation strategies.

Multilevel Signaling

The use of multilevel signaling is another well-known technique for increasing the data rate over bandlimited channels. Practical issues for high-speed pulse amplitude modulation are an active research area. How can timing recovery be efficiently performed? What are good line codes? How can linearity be ensured in 10+ Gb/s circuits?

Similar challenges arise in a partial response or full-duplex receiver since in either case it must be capable of discerning more than two received levels. Partial response signaling has been proposed for some time for chip-to-chip links, although practical systems are only now beginning to appear. Full-duplex communication allows for decreased pin counts in bidirectional applications, but has been problematic in practice due primarily to near-end (self) crosstalk.

Coding

Research on coding for parallel chip-to-chip interfaces (i.e. a data bus) to improve noise immunity while maintaining a low pin-count has resulted in an "incremental signaling" approach. This approach resembles partial response signaling except that the difference is taken in space across the width of the bus, rather than in time as in traditional partial response channels.

The straight forward approach diagrammed above provides performance that is 3 dB worse than fully-differential signaling, but with approximately half the number of pins. With a more complex receiver, the performance can be made practically identical to that of a fully-differential system.

Reference

A. Carusone, K. Farzan and D. A. Johns, "Differential Signaling with a Reduced Number of Signal Paths," IEEE Transactions on Circuits and Systems II, March 2001, pp. 294-300. [PDF Format]