# Program Transformations for Cache Locality Enhancement on Shared-memory Multiprocessors

by

Naraig Manjikian

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy Graduate Department of Electrical and Computer Engineering University of Toronto

© Copyright by Naraig Manjikian 1997

#### **Abstract**

Program Transformations for Cache Locality Enhancement on Shared-memory Multiprocessors

Naraig Manjikian

Doctor of Philosophy

Graduate Department of Electrical and Computer Engineering

University of Toronto

1997

This dissertation proposes and evaluates compiler techniques that enhance cache locality and consequently improve the performance of parallel applications on shared-memory multi-processors. These techniques target applications with loop-level parallelism that can be detected and exploited automatically by a compiler. Novel program transformations are combined with appropriate loop scheduling in order to exploit data reuse while maintaining parallelism and avoiding cache conflicts.

First, this dissertation proposes the *shift-and-peel* transformation for enabling loop fusion and exploiting reuse across parallel loops. The shift-and-peel transformation overcomes dependence limitations that have previously prevented loops from being fused legally, or prevented legally-fused loops from being parallelized. Therefore, this transformation exploits all reuse across loops without loss of parallelism.

Second, this dissertation describes and evaluates adaptations of static *loop scheduling strategies* to exploit wavefront parallelism while ensuring locality in tiled loops. Wavefront parallelism results when tiling is enabled by combining the shift-and-peel transformation with loop skewing. Proper scheduling exploits both intratile and intertile data reuse when independent tiles are executed in parallel on a large number of processors.

Third, this dissertation proposes *cache partitioning* for preventing cache conflicts between data from different arrays, especially when exploiting reuse across loops. Specifically, cache partitioning prevents frequently-recurring conflicts in loops with compatible data access patterns. Cache partitioning transforms the data layout such that there are no conflicts for reused data from different arrays during loop execution.

An analytical model is also presented to assess the potential benefit of locality enhancement. This model estimates the expected reduction in execution time by parameterizing the reduction in the number of memory accesses with locality enhancement and the contribution of memory accesses towards execution time.

Experimental results show that the proposed techniques improve parallel performance by 20%-60% for representative applications on contemporary multiprocessors. The results also show that significant improvements are obtained in conjunction with other performance-enhancing techniques such as prefetching. The importance of the techniques described in this dissertation will continue to increase as processor performance continues to increase more rapidly than memory performance.

### Acknowledgements

First and foremost, I would like to thank my supervisor, Dr. Tarek S. Abdelrahman. For five years, he has maintained the right balance between providing close supervision and giving me the freedom to pursue my ideas, and he has given me much-appreciated encouragement and advice along the path of graduate studies. His attention to my work ultimately helped ensure its final quality.

I would also like to thank the members of my examination committee, Dr. David A. Padua, Dr. Zvonko G. Vranesic, Dr. Kenneth C. Sevcik, Dr. Todd C. Mowry, and Dr. Stephen D. Brown, for their careful reading and critical evaluation of my dissertation.

Access to the multiprocessor systems used in this research was provided by the University of Michigan Center for Parallel Computing. In particular, I would like to acknowledge the assistance of Andrew Caird of the Center of Parallel Computing.

I am grateful for the financial support that I have received during the course of my doctoral studies. I have been supported by a Postgraduate Scholarship from the Natural Sciences and Engineering Research Council of Canada, a University of Toronto Open Doctoral Fellowship, and a V. L. Henderson Memorial Fellowship. Additional financial support for this research was provided by the Natural Sciences and Engineering Research Council, and by the Information Technology Research Centre of Ontario.

I am also grateful for the opportunity to have participated in the NUMAchine Multiprocessor Project at the University of Toronto. I would like to thank the faculty, staff, and students involved in the NUMAchine Project for providing me with a rewarding experience.

I would like to thank the members of my extended family for their kindness and support, and for always providing me with a home away from home during the entire course of my university education.

To my parents, Hagop and Dirouhie, my brother, Sevak, and my sister, Lalai, words alone cannot convey my heartfelt gratitude. Despite my long absences, you supported all of my scholarly endeavors. You accepted the importance of my education, and you respected my decisions, although you gave me advice so that my direction was always clear. Let us always celebrate our successes together.

# **Contents**

| 1 | Intr | oductio | n                                                                 | 1  |

|---|------|---------|-------------------------------------------------------------------|----|

|   | 1.1  | Large-  | Scale Shared-memory Multiprocessors                               | 1  |

|   | 1.2  | Loop-l  | level Parallelism and Parallelizing Compilers                     | 3  |

|   | 1.3  | Data R  | Reuse and Cache Locality                                          | 4  |

|   | 1.4  | Cache   | Locality Enhancement                                              | 5  |

|   | 1.5  | Resear  | ch Overview                                                       | 6  |

|   | 1.6  | Thesis  | Organization                                                      | 8  |

| 2 | Bac  | kground | d                                                                 | 9  |

|   | 2.1  | Loops   | and Loop Nests                                                    | 9  |

|   | 2.2  | Loop I  | Dependence Analysis                                               | 11 |

|   |      | 2.2.1   | Iteration Spaces, Iteration Vectors, and Lexicographical Ordering | 11 |

|   |      | 2.2.2   | Definition and Use of Variables                                   | 12 |

|   |      | 2.2.3   | Data Dependence                                                   | 12 |

|   |      | 2.2.4   | The Dependence Problem                                            | 13 |

|   |      | 2.2.5   | Dependence Tests                                                  | 14 |

|   | 2.3  | Loop F  | Parallelization and Concurrentization                             | 16 |

|   |      | 2.3.1   | DOALL Loops and DOACROSS Loops                                    | 16 |

|   |      | 2.3.2   | Data Expansion and Privatization to Enable Parallelization        | 17 |

|   |      | 2.3.3   | Recognition of Induction and Reduction Variables                  | 18 |

|   |      | 2.3.4   | Scheduling Loop Iterations                                        | 19 |

|   | 2.4  | Loop 7  | Γransformations for Locality and Parallelism                      | 20 |

|   |      | 2.4.1   | Data Reuse and Locality                                           | 20 |

|   |     | 2.4.2    | Degree and Granularity of Parallelism                              | 21 |

|---|-----|----------|--------------------------------------------------------------------|----|

|   |     | 2.4.3    | Unimodular Transformations                                         | 21 |

|   |     | 2.4.4    | Tiling                                                             | 23 |

|   |     | 2.4.5    | Loop Distribution                                                  | 24 |

|   |     | 2.4.6    | Loop Fusion                                                        | 25 |

|   | 2.5 | Data T   | Transformations                                                    | 26 |

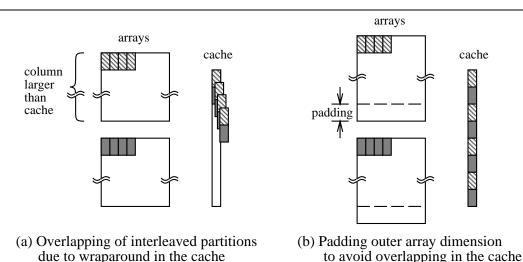

|   |     | 2.5.1    | Memory Alignment                                                   | 26 |

|   |     | 2.5.2    | Array Padding                                                      | 26 |

|   |     | 2.5.3    | Array Element Reordering                                           | 27 |

|   |     | 2.5.4    | Array Expansion and Contraction                                    | 27 |

|   |     | 2.5.5    | Array Merging                                                      | 28 |

|   | 2.6 | Effecti  | veness of Locality Enhancement within Loop Nests                   | 28 |

|   |     | 2.6.1    | Survey of Selected Studies                                         | 28 |

|   |     | 2.6.2    | Conclusions and Implications                                       | 31 |

| 3 | Oua | ntifving | g the Benefit of Locality Enhancement                              | 34 |

|   | 3.1 |          | iew of Model and Underlying Assumptions                            | 34 |

|   | 3.2 |          | Ifying Memory Accesses for Arrays                                  | 36 |

|   | 3.3 |          | Ifying the Reduction in Memory Accesses with Locality Enhancement. | 37 |

|   | 3.4 |          | Ifying the Impact of Locality Enhancement on Execution Time        | 38 |

|   | 3.5 | Potent   | ial Limitations of the Model                                       | 40 |

|   | 3.6 | Chapte   | er Summary                                                         | 42 |

|   |     | -        |                                                                    |    |

| 4 | The | Shift-a  | nd-peel Transformation for Loop Fusion                             | 43 |

|   | 4.1 | Loop I   | Fusion                                                             | 43 |

|   |     | 4.1.1    | Granularity of Parallelism and Frequency of Synchronization        | 43 |

|   |     | 4.1.2    | Quantifying the Benefit of Enhancing Locality with Fusion          | 44 |

|   |     | 4.1.3    | Dependence Limitations on the Applicability of Loop Fusion         | 45 |

|   |     | 4.1.4    | Related Work                                                       | 47 |

|   | 4.2 | The Sh   | nift-and-peel Transformation                                       | 48 |

|   |     | 421      | Shifting to Enable Legal Fusion                                    | 48 |

|   |      | 4.2.2  | Peeling to Enable Parallelization of Fused Loops       | 49 |

|---|------|--------|--------------------------------------------------------|----|

|   |      | 4.2.3  | Derivation of Shift-and-peel                           | 50 |

|   |      | 4.2.4  | Implementation of Shift-and-peel                       | 54 |

|   |      | 4.2.5  | Legality of the Shift-and-peel Transformation          | 57 |

|   | 4.3  | Multid | imensional Shift-and-peel                              | 65 |

|   |      | 4.3.1  | Motivation                                             | 65 |

|   |      | 4.3.2  | Derivation                                             | 65 |

|   |      | 4.3.3  | Implementation                                         | 66 |

|   |      | 4.3.4  | Legality of Multidimensional Shift-and-peel            | 69 |

|   | 4.4  | Fusion | with Boundary-scanning Loop Nests                      | 69 |

|   | 4.5  | Chapte | er Summary                                             | 72 |

| _ | G.L. | 1 1    | XX7 C 4 D H P                                          |    |

| 5 |      | Ü      | Wavefront Parallelism in Tiled Loop Nests              | 73 |

|   | 5.1  | Wavef  | ront Parallelism in Tiled Loop Nests                   | 73 |

|   |      | 5.1.1  | Loop Skewing to Enable Legal Tiling                    | 73 |

|   |      | 5.1.2  | Enabling Tiling with the Shift-and-Peel Transformation | 74 |

|   |      | 5.1.3  | Wavefront Parallelism after Tiling                     | 77 |

|   |      | 5.1.4  | Exploiting Wavefront Parallelism: DOALL vs. DOACROSS   | 78 |

|   | 5.2  | Data R | euse in Tiled Loop Nests                               | 79 |

|   |      | 5.2.1  | Intratile and Intertile Reuse                          | 79 |

|   |      | 5.2.2  | Quantifying the Locality Benefit of Tiling             | 80 |

|   |      | 5.2.3  | Tile Size, Parallelism, and Locality                   | 83 |

|   | 5.3  | Relate | d Work                                                 | 83 |

|   |      | 5.3.1  | Tiling                                                 | 83 |

|   |      | 5.3.2  | Loop Scheduling                                        | 84 |

|   |      | 5.3.3  | Scheduling Vectors                                     | 85 |

|   | 5.4  | Schedu | aling Strategies for Wavefront Parallelism             | 85 |

|   |      | 5.4.1  | Dynamic Self-scheduling                                | 86 |

|   |      | 5.4.2  | Static Cyclic Scheduling                               | 87 |

|   |      | 5.4.3  | Static Block Scheduling                                | 88 |

|   |     | 5.4.4   | Comparison of Scheduling Strategies                       | 89  |

|---|-----|---------|-----------------------------------------------------------|-----|

|   |     |         | 5.4.4.1 Runtime Overhead for Scheduling                   | 89  |

|   |     |         | 5.4.4.2 Synchronization Requirements                      | 90  |

|   |     |         | 5.4.4.3 Parallelism and Theoretical Completion Time       | 90  |

|   |     |         | 5.4.4.4 Locality Enhancement                              | 95  |

| 6 | Cac | he Part | itioning to Eliminate Cache Conflicts                     | 98  |

|   | 6.1 | Cache   | Conflicts                                                 | 98  |

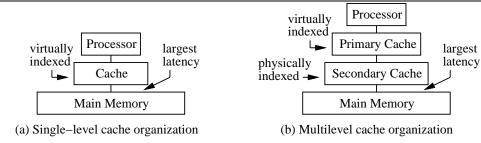

|   |     | 6.1.1   | Cache Organization and Indexing Methods                   | 98  |

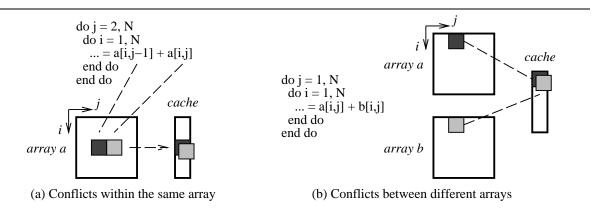

|   |     | 6.1.2   | Cache Conflicts for Arrays in Loops                       | 99  |

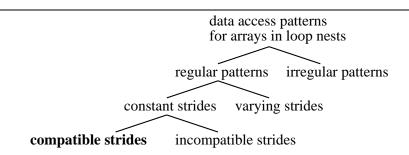

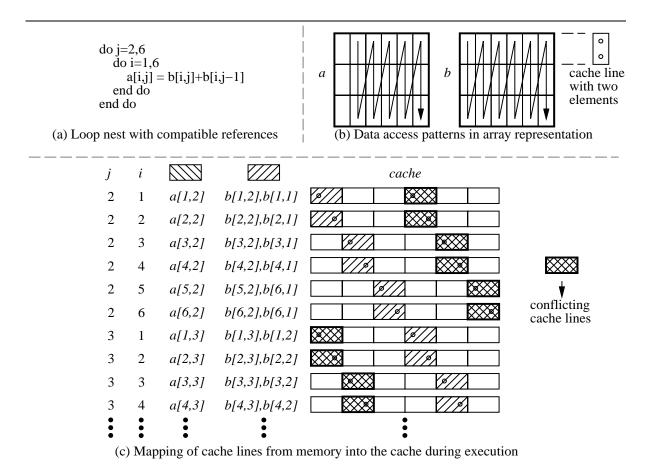

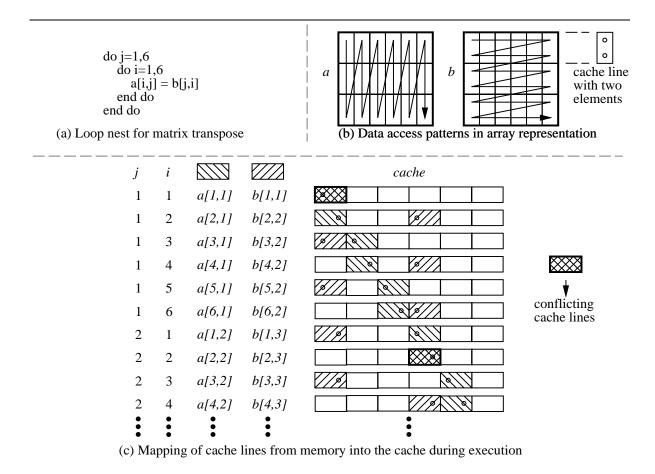

|   |     | 6.1.3   | Data Access Patterns and Cache Conflicts                  | 100 |

|   |     | 6.1.4   | Related Work                                              | 104 |

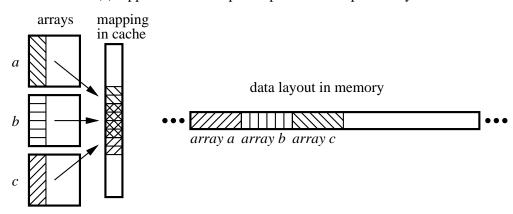

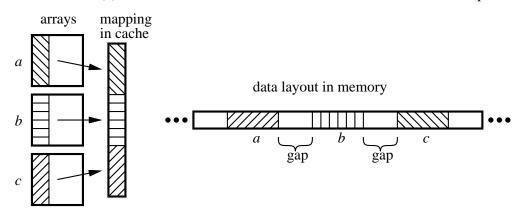

|   | 6.2 | Cache   | Partitioning                                              | 105 |

|   |     | 6.2.1   | Overview                                                  | 106 |

|   |     | 6.2.2   | One-dimensional Cache Partitioning                        | 108 |

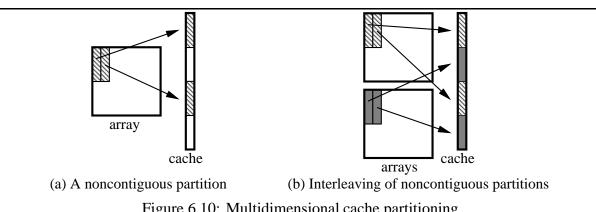

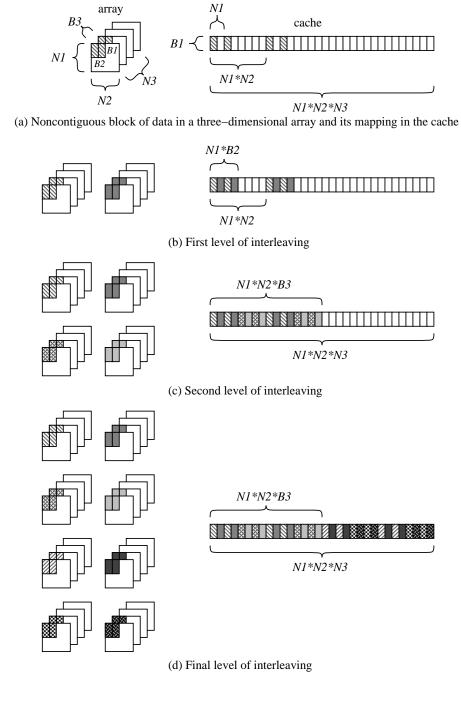

|   |     | 6.2.3   | Multidimensional Cache Partitioning                       | 111 |

|   |     | 6.2.4   | Cache Partitioning for Multiple Loop Nests                | 117 |

|   | 6.3 | Chapte  | er Summary                                                | 119 |

| 7 | Exp | eriment | tal Evaluation                                            | 122 |

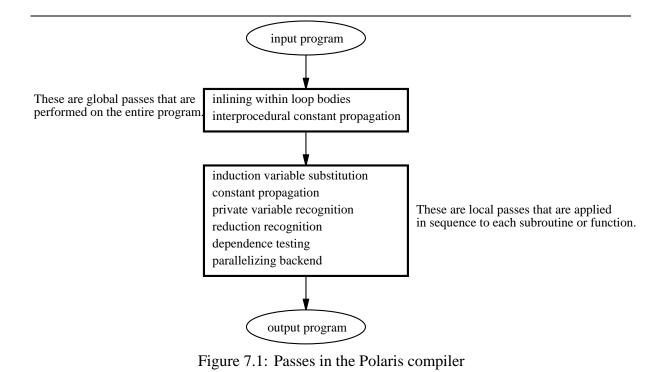

|   | 7.1 | Protot  | ype Compiler Implementation                               | 122 |

|   |     | 7.1.1   | Compiler Infrastructure                                   | 123 |

|   |     | 7.1.2   | Enhancements to Infrastructure                            | 124 |

|   |     |         | 7.1.2.1 Support for High-level Code Transformations       | 124 |

|   |     |         | 7.1.2.2 Dependence Distance Information Across Loop Nests | 125 |

|   |     |         | 7.1.2.3 Manipulation of Array Data Layout                 | 125 |

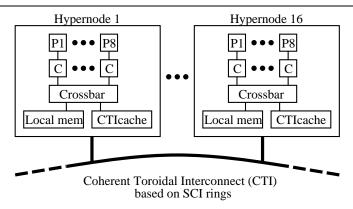

|   | 7.2 | Experi  | imental Platforms                                         | 126 |

|   |     | 7.2.1   | Hewlett-Packard/Convex SPP1000 and SPP1600                | 126 |

|   |     | 7.2.2   | Silicon Graphics Power Challenge R10000                   | 128 |

|   | 7.3 | Codes   | Used in Experiments                                       | 129 |

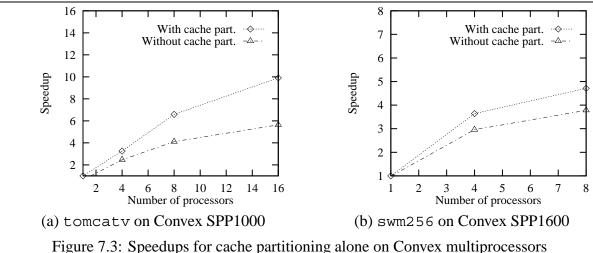

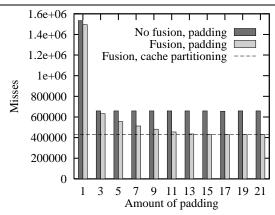

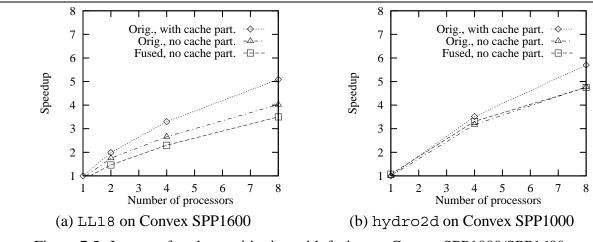

|   | 7.4 | Effecti | iveness of Cache Partitioning                             | 131 |

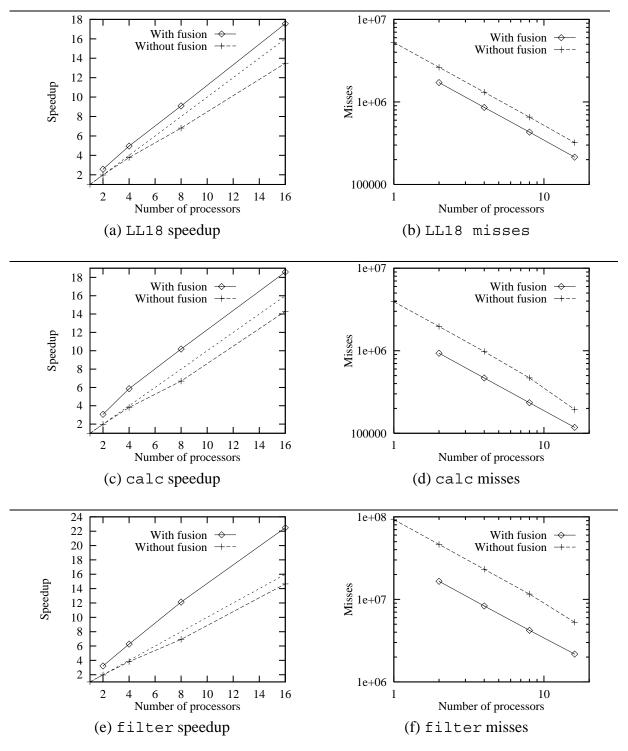

|    | 7.5    | Effecti | veness of the Shift-and-peel Transformation                           |

|----|--------|---------|-----------------------------------------------------------------------|

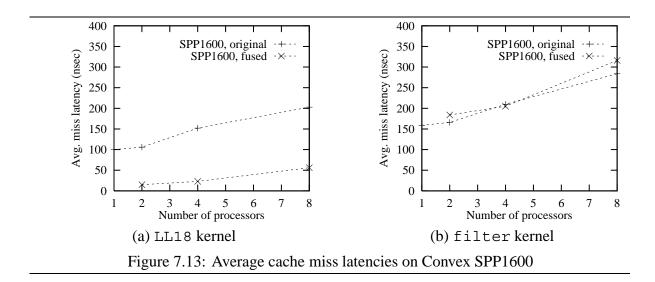

|    |        | 7.5.1   | Results for Kernels                                                   |

|    |        |         | 7.5.1.1 Derived Amounts of Shifting and Peeling                       |

|    |        |         | 7.5.1.2 Multiprocessor Speedups                                       |

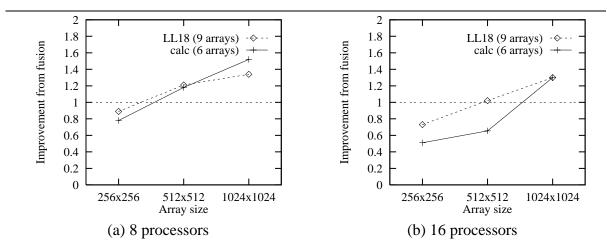

|    |        |         | 7.5.1.3 Impact of Problem Size on the Improvement from Fusion . 136   |

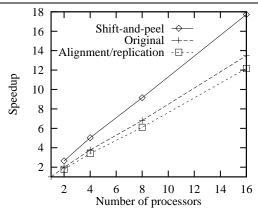

|    |        |         | 7.5.1.4 Comparison of Shift-and-peel with Alignment/replication . 138 |

|    |        | 7.5.2   | Comparing Measured Performance Improvements with the Model 139        |

|    |        |         | 7.5.2.1 Determining the Sweep Ratios                                  |

|    |        |         | 7.5.2.2 Determining $f_m$ and Applying the Model                      |

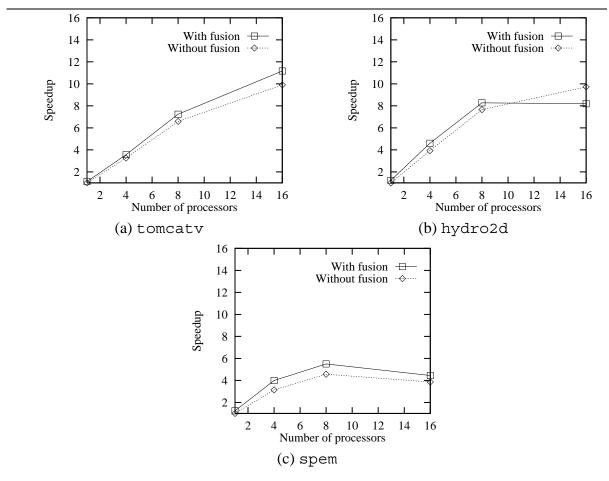

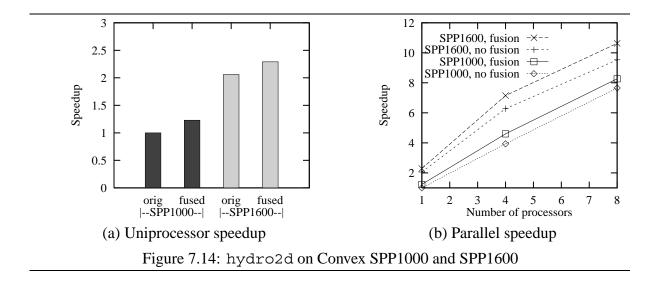

|    |        | 7.5.3   | Results for Applications                                              |

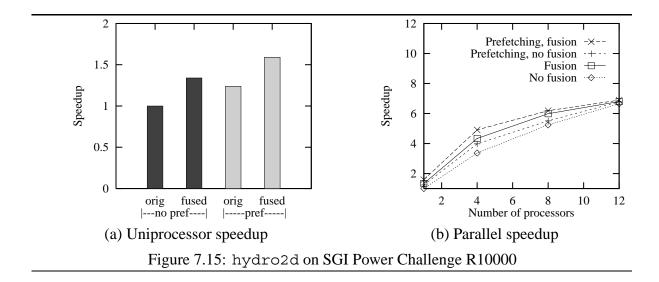

|    |        | 7.5.4   | Combining Shift-and-peel with Prefetching                             |

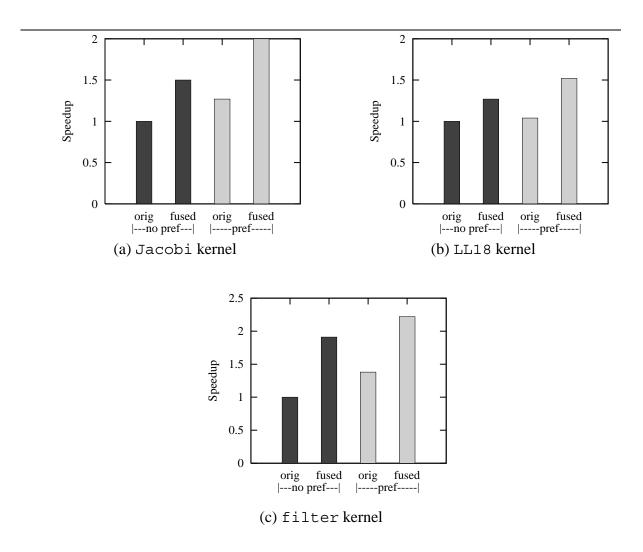

|    |        |         | 7.5.4.1 Results for Kernels                                           |

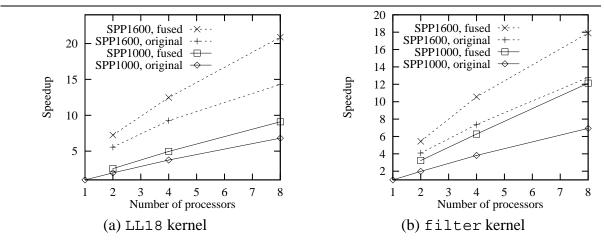

|    |        |         | 7.5.4.2 Results for Applications                                      |

|    |        | 7.5.5   | Summary for the Shift-and-peel Transformation                         |

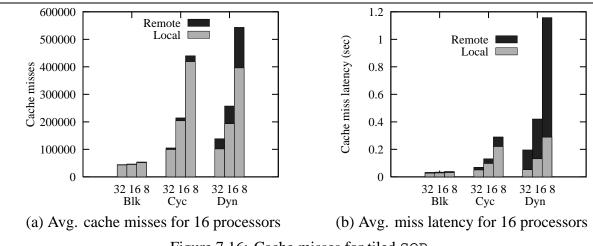

|    | 7.6    | Evalua  | tion of Scheduling for Wavefront Parallelism                          |

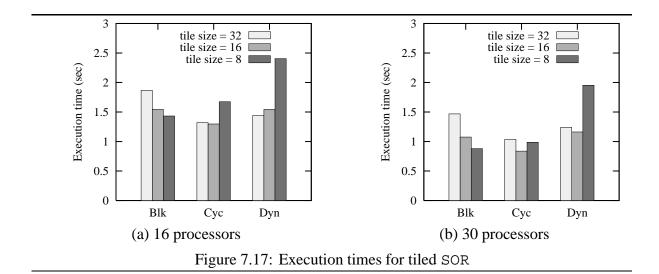

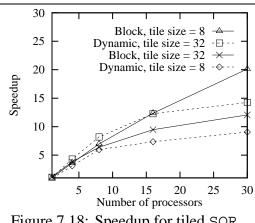

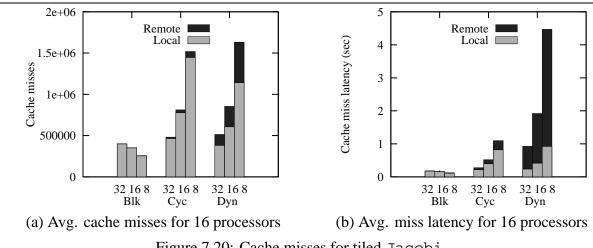

|    |        | 7.6.1   | Results for SOR                                                       |

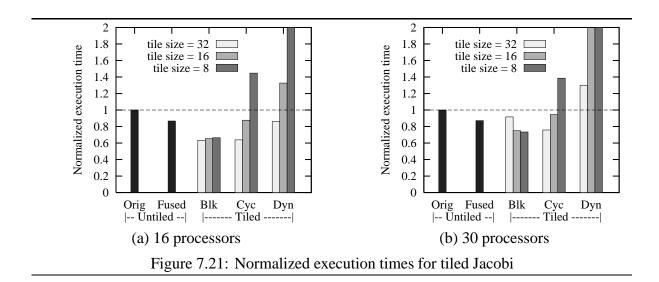

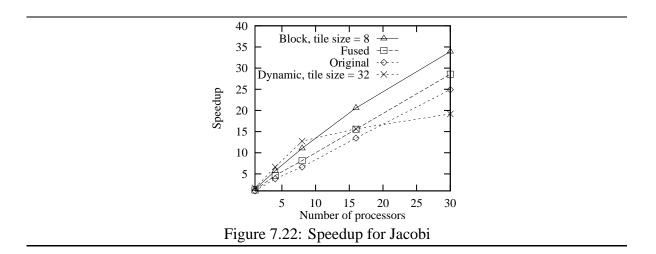

|    |        | 7.6.2   | Results for Jacobi                                                    |

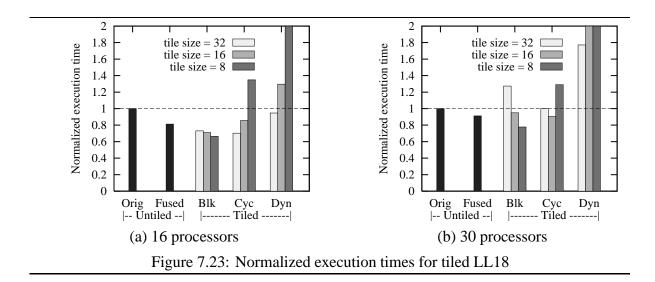

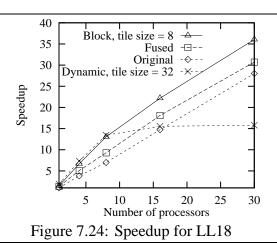

|    |        | 7.6.3   | Results for LL18                                                      |

|    |        | 7.6.4   | Comparison of Sweep Ratios for Tiling                                 |

|    |        | 7.6.5   | Summary for Evaluation of Scheduling Strategies                       |

| O  | Com    | alai a  | 163                                                                   |

| ð  |        | clusion | 163                                                                   |

|    | 8.1    |         | ary of Contributions                                                  |

|    | 8.2    | ruture  | Work                                                                  |

| Bi | bliogr | raphy   | 167                                                                   |

# **List of Tables**

| 5.1  | Comparison of scheduling strategies for tiling                                     | 89  |

|------|------------------------------------------------------------------------------------|-----|

| 7.1  | Kernels and applications for experimental results                                  | 130 |

| 7.2  | Kernels and applications used in experiments for the shift-and-peel transformation | 134 |

| 7.3  | Amounts of shifting and peeling for kernels                                        | 135 |

| 7.4  | Characteristics of loop nest kernels                                               | 140 |

| 7.5  | Revised sweep ratios to account for upgrade requests                               | 142 |

| 7.6  | Cache misses for parallel execution on Convex SPP1000                              | 142 |

| 7.7  | Comparison of estimated and measured improvement from fusion                       | 143 |

| 7.8  | Expected and measured cache misses for uniprocessor execution on Power             |     |

|      | Challenge                                                                          | 147 |

| 7.9  | Expected and measured writebacks for uniprocessor execution on Power Chal-         |     |

|      | lenge                                                                              | 148 |

| 7.10 | Cache misses for parallel execution on Convex SPP1600                              | 149 |

| 7.11 | Cache misses and sweep ratios for Jacobi on Convex SPP1000 (16 processors)         | 161 |

# **List of Figures**

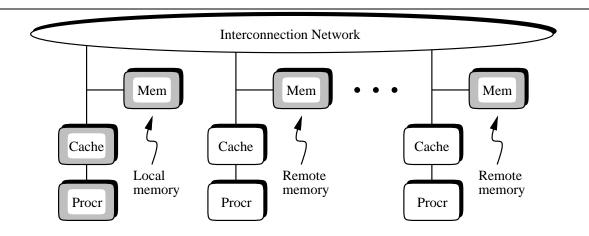

| 1.1  | Large-scale shared-memory multiprocessor architecture                            | 2  |

|------|----------------------------------------------------------------------------------|----|

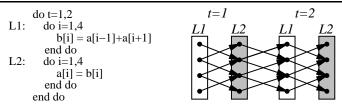

| 1.2  | Parallelism in loops                                                             | 3  |

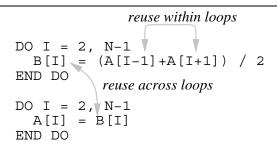

| 1.3  | Data reuse in loops                                                              | 4  |

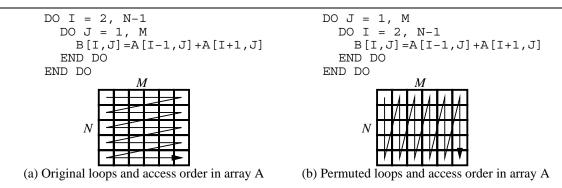

| 1.4  | Example of loop permutation                                                      | 5  |

| 2.1  | Classification of loop nest structure                                            | 10 |

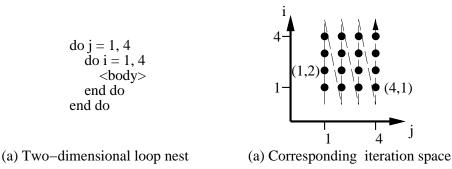

| 2.2  | A two-dimensional iteration space                                                | 12 |

| 2.3  | Example formulation of the dependence problem for subscripted array references   | 15 |

| 2.4  | A DOACROSS loop with explicit synchronization for loop-carried dependences       | 17 |

| 2.5  | Scalar expansion to eliminate loop-carried antidependences                       | 18 |

| 2.6  | Induction variable recognition                                                   | 19 |

| 2.7  | Reduction variable recognition                                                   | 19 |

| 2.8  | Unimodular transformations                                                       | 22 |

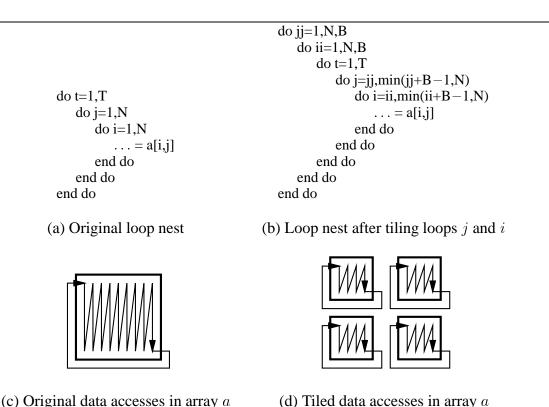

| 2.9  | Example of tiling                                                                | 24 |

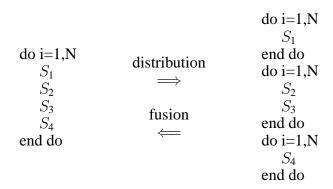

| 2.10 | Loop distribution and loop fusion                                                | 25 |

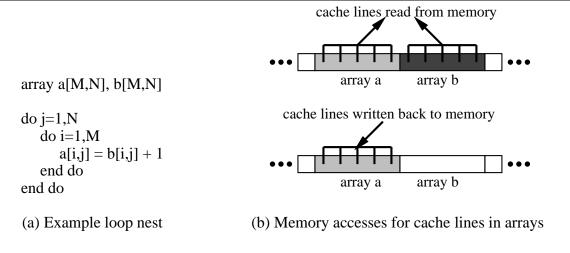

| 3.1  | Illustration of memory accesses for arrays in loop nests                         | 36 |

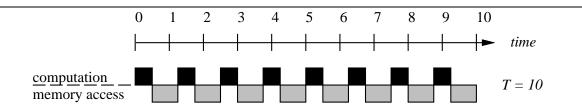

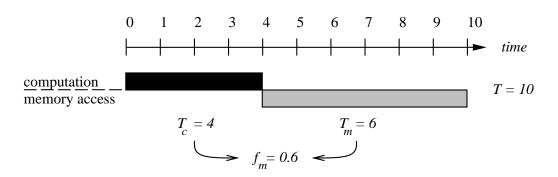

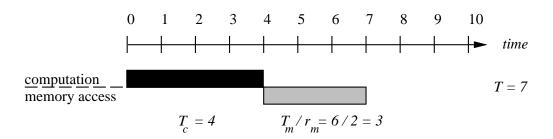

| 3.2  | Graphical representation of $T = T_c + T_m$ and effect of locality enhancement . | 39 |

| 3.3  | Examples of loop nests accessing arrays with differing dimensionalities          | 41 |

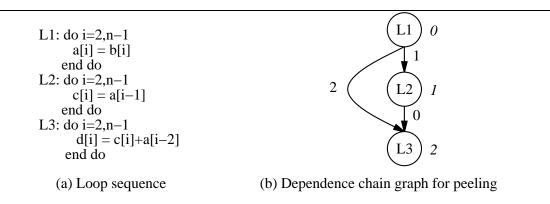

| 4.1  | Example to illustrate fusion-preventing dependences                              | 46 |

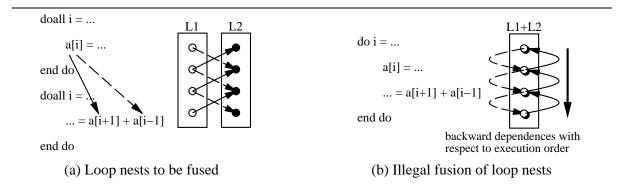

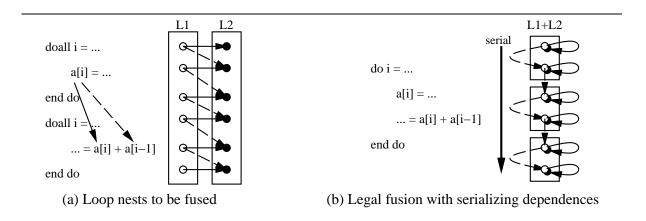

| 4.2  | Example to illustrate serializing dependences                                    | 46 |

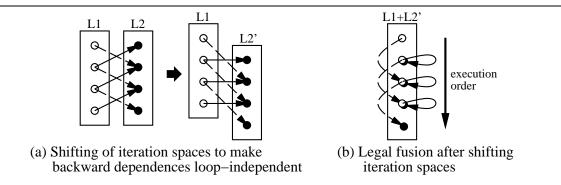

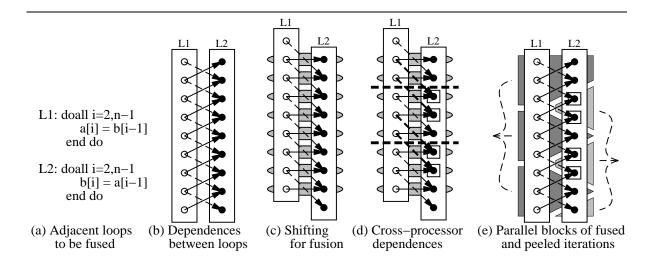

| 4.3  | Shifting iteration spaces to permit legal fusion                                 | 49 |

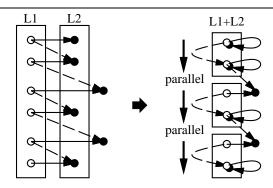

| 4.4  | Peeling to retain parallelism when fusing parallel loops                         | 50 |

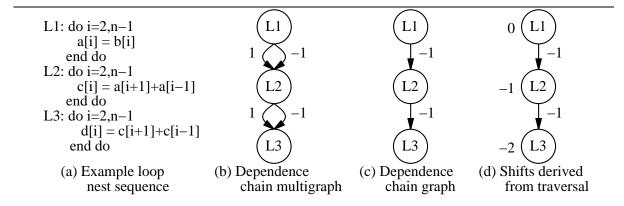

| 4.5  | Algorithm for propagating shifts along dependence chains                         | 52 |

| 4.6  | Representing dependences to derive shifts for fusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

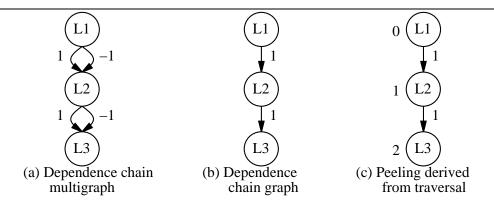

| 4.7  | Algorithm for propagating peeling along dependence chains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53 |

| 4.8  | Deriving the required amount of peeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54 |

| 4.9  | Dependence chain graph with dependences between non-adjacent loops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54 |

| 4.10 | Alternatives for implementing fusion with shift-and-peel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55 |

| 4.11 | Complete implementation of fusion with shift-and-peel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56 |

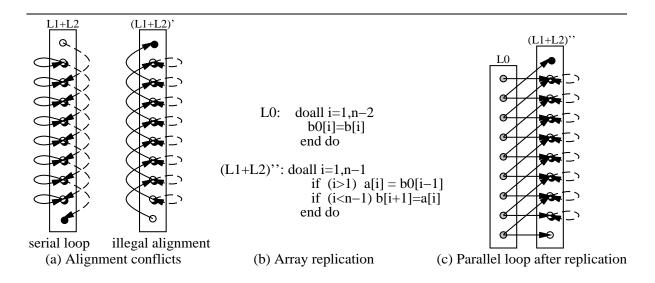

| 4.12 | Legality of the shift-and-peel transformation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57 |

| 4.13 | Resolution of alignment conflicts with replication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 59 |

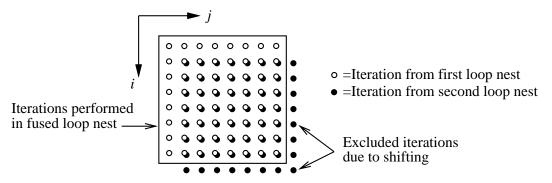

| 4.14 | Fusion with multidimensional shifting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 67 |

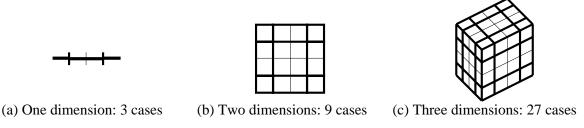

| 4.15 | Enumerating the number of cases for multidimensional shift-and-peel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 67 |

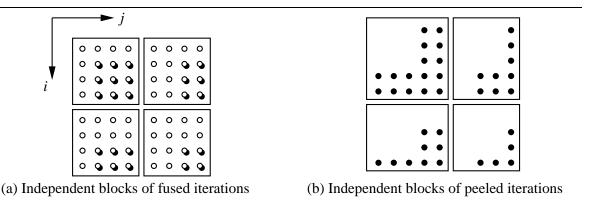

| 4.16 | Parallelization with multidimensional peeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68 |

| 4.17 | Independent blocks of iterations with multidimensional shift-and-peel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 68 |

| 4.18 | Fusing a loop nest sequence with a boundary-scanning loop nest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 70 |

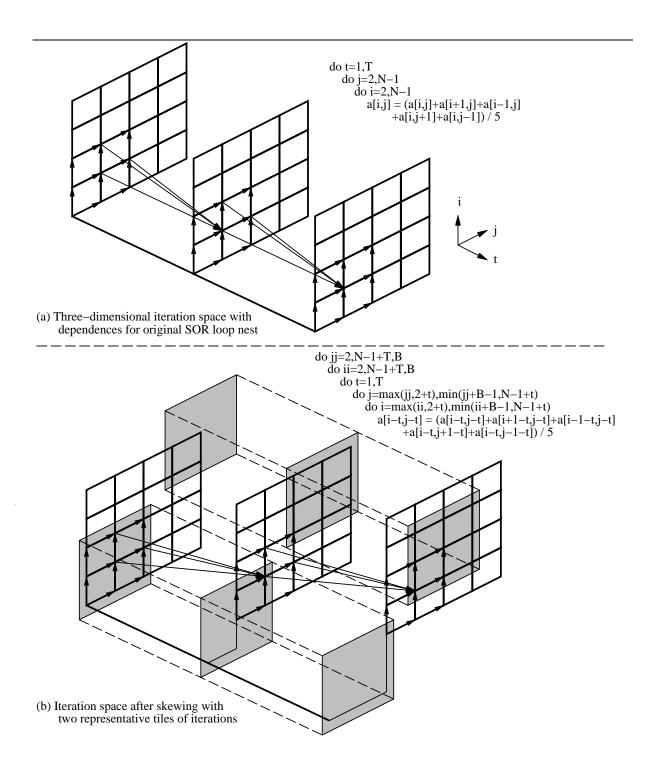

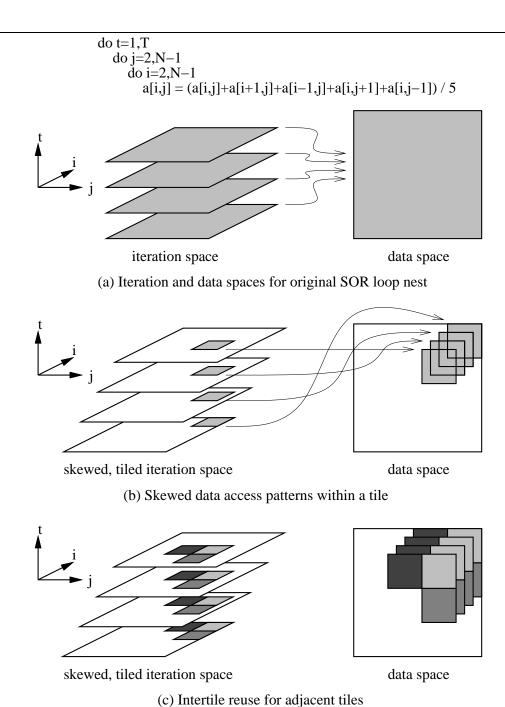

| 5.1  | Steps in tiling the SOR loop nest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74 |

| 5.2  | Graphical representation of skewing and tiling in the iteration space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 75 |

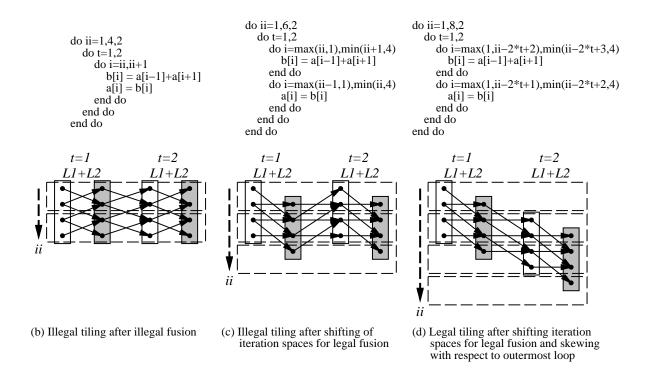

| 5.3  | Enabling tiling with the shift-and-peel transformation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76 |

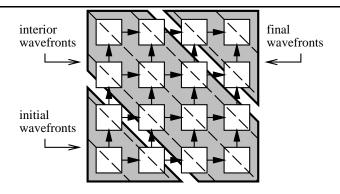

| 5.4  | Dependences and wavefronts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 78 |

| 5.5  | Exploiting parallelism with inner DOALL loops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 79 |

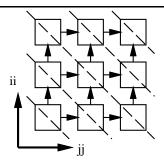

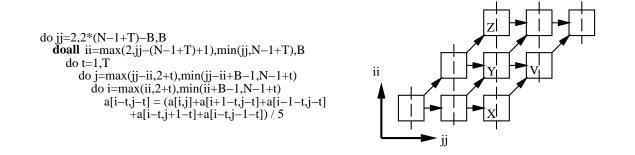

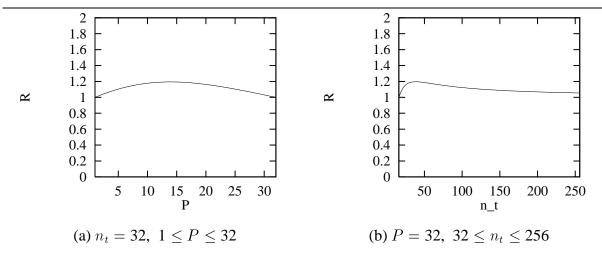

| 5.6  | Data reuse in a tiled loop nest that requires skewing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 81 |

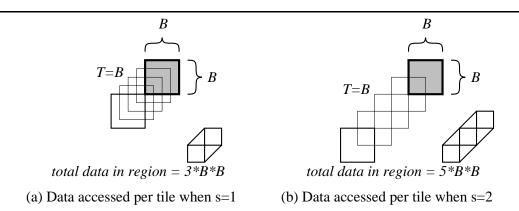

| 5.7  | Amount of data accessed per tile with skewing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82 |

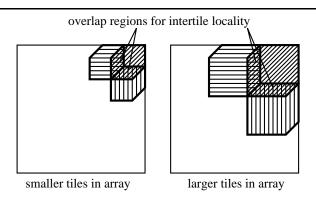

| 5.8  | Impact of tile size on locality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84 |

| 5.9  | Static cyclic scheduling of tiles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 87 |

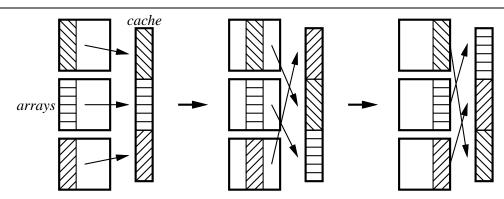

| 5.10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88 |

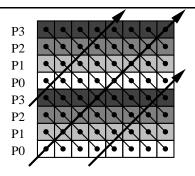

|      | Wavefronts for dynamic and cyclic scheduling $(n_t = 4, P = 2)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 92 |

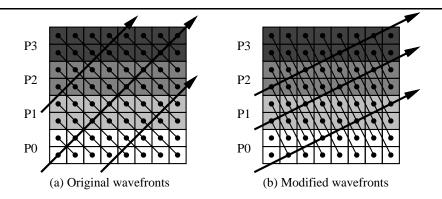

|      | Wavefronts for block scheduling $(n_t = 4, P = 2)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 93 |

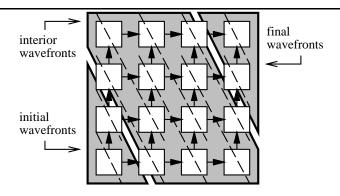

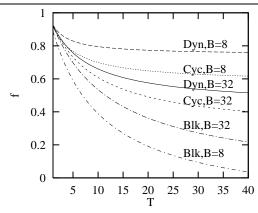

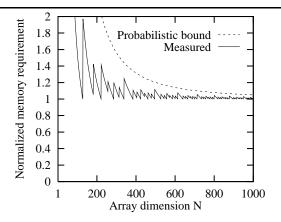

|      | Variation of completion time ratio $R = T_{blk}/T_{cyc}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 94 |