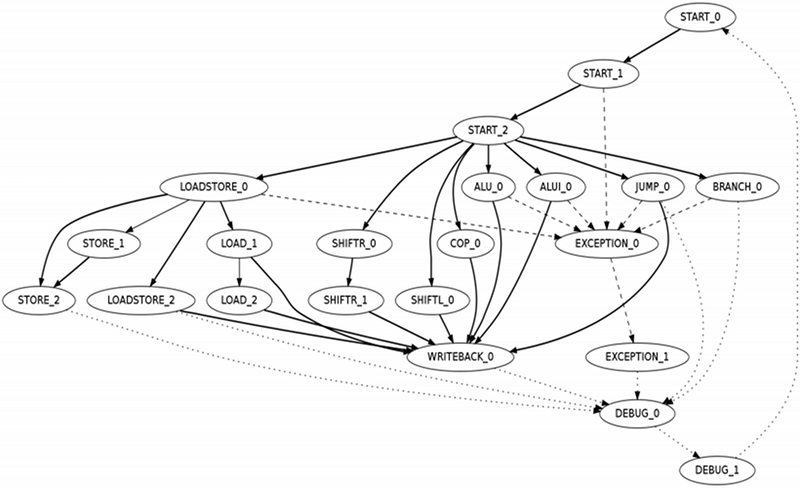

| State | Activities | Next States | Cycles | Exceptions |

|---|---|---|---|---|

| START-0 | Load instruction | START_1 | 2 | None |

| Reset branch conditions | ||||

| START-1 | Check branch conditions | START_2 | 33 | Int |

| A = rs (decoded) | Bp | |||

| B = rt (decoded) | Syscall | |||

| PC = nPC | RI | |||

| nPC = nPC (branch) or PC+4 | CpU | |||

| START-2 | Choose whether to shift in zeros or data | ALU_0 | 1 | None |

| ALUI_0 | ||||

| SHIFTL_0 | ||||

| SHIFTR_0 | ||||

| Choose FSM path based on instruction | BRANCH_0 | |||

| LOADSTORE_0 | ||||

| JUMP_0 | ||||

| COP0_0 | ||||

| ALU_0 | A = rs <op> rt | WRITEBACK_0 | 33 | Ov |

| ALUI_0 | A = rs <op> IMM || rs = IMM (LUI) | WRITEBACK_0 | 33 | Ov |

| SHIFTL_0 | A = rs (shifted) | WRITEBACK_0 | 33 | None |

| SHIFTR_0 | A = rt | SHIFTR_1 | 33 | None |

| SHIFTR_1 | A = A (shifted) | WRITEBACK_0 | Variable | None |

| LOADSTORE_0 | A = rt + IMM(SE) | LOAD_1 | 33 | AdEL |

| STORE_1 | AdES | |||

| STORE_2 | ||||

| STORE_1 | Wrap byte/halfword to front of B | STORE_2 | Up to 28 | None |

| STORE_2 | Write B to data memory | START_0 | waitrq | None |

| LOAD_1 | Read data memory into A | WRITEBACK_0 | waitrq | None |

| LOAD_2 | ||||

| LOAD_2 | Wrap data to left end of A | LOAD_3 | Up to 28 | None |

| LOAD_3 | Sign-extend A | WRITEBACK_0 | 17/25 | None |

| BRANCH_0 | Set branch delay stack | START_0 | 33 | None |

| nPC = PC + IMM or PC+4 | ||||

| JUMP_0 | nPC = A || nPC = IMM | WRITEBACK_0 | 33 | AdEL |

| A = nPC | START_0 | |||

| COP0_0 | A = cop0out || cop0in = B | WRITEBACK_0 | 33 | None |

| START_0 | ||||

| WRITEBACK_0 | Register = A | START_0 | 1 | None |