Research Interests

Mixed-Signal Integrated Circuits:

• Communications: Circuits for High speed wireline communication over copper and fiber optic cables

• Memories: Low-power and reliable Memories and Deep-subthreshold Sense Amplifier Circuits

• Machine Learning: Mixed-signal circuits for energy efficient computing for deep learning accelerators

Photonic Integrated Circuits:

• CMOS-Photonic Intagration: Die-to-Die CMOS-Photonic interfaces

Publications

IEEE Copyright Notice:

© IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Refereed Journal Papers:

[J5] B. Radi, Z. Li, D. Patel and A. C. Carusone, "Optimizing the Photodetector/Analog Front-end Interface in Optical Communication Receivers," in IEEE Transactions on Signal and Power Integrity, 2023, vol. 2, pp. 111-121, Aug. 2023 [PDF] [IEEExplore Link]

[J4] D. Patel, A. Sharif-Bakhtiar and A. C. Carusone, "A 112 Gb/s -8.2 dBm Sensitivity 4-PAM Linear TIA in 16nm CMOS with Co-Packaged Photodiodes," in IEEE Journal of Solid-State Circuits (JSSC), vol. 58, no. 3, pp. 771-784, March 2023. [Invited Paper from CICC'22] [PDF] [IEEExplore Link]

[J3] D. Patel, A. Neale, D. Wright and M. Sachdev, "Body Biased Sense Amplifier with Auto-Offset Mitigation for Low-Voltage SRAMs," in IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I), vol. 68, no. 8, pp. 3265-3278, Aug. 2021. [PDF] [IEEExplore Link]

[J2] D. Patel, A. Neale, D. Wright and M. Sachdev, "Hybrid Latch-Type Offset Tolerant Sense Amplifier for Low-Voltage SRAMs," in IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I), vol. 66, no. 7, pp. 2519-2532, July 2019. [PDF] [IEEExplore Link]

[J1] D. Patel and M. Sachdev, "0.23-V Sample-Boost-Latch-Based Offset Tolerant Sense Amplifier," in IEEE Solid-State Circuits Letters (SSC-L), vol. 1, no. 1, pp. 6-9, Jan. 2018. [PDF] [IEEExplore Link]

Refereed Conference Papers, Posters and Presentations:

[C4] D. Patel, B. Radi, A. Sharif-Bakhtiar and A. C. Carusone, "Experimental Study of the Equalization Requirements of a 2.5D Co-Packaged 16-nm CMOS Optical Receiver up to 160 Gb/s," in 2022 European Conference on Optical Communication (ECOC), Basel, Switzerland, 2022, pp. 1-4. [PDF] [IEEExplore Link]

[C3] D. Patel, A. Sharif-Bakhtiar and A. C. Carusone, "A 112 Gb/s -8.2 dBm Sensitivity 4-PAM Linear TIA in 16nm CMOS with Co-Packaged Photodiodes," in 2022 IEEE Custom Integrated Circuits Conference (CICC), 2022, pp. 1-2, Newport Beach, CA, USA. (Outstanding Student Paper Award) [PDF] [IEEExplore Link]

[C2] D. Patel, D. Wright and M. Sachdev, "Sense amplifier offset characterisation and test implications for low-voltage SRAMs in 65 nm," in 2018 IEEE 23rd European Test Symposium (ETS), Bremen, 2018, pp. 1-6. [PDF] [Slides] [IEEExplore Link]

[C1] D. Patel and M. Sachdev, "Sample-Boost-Latch Based Offset Tolerant Sense Amplifier for Sub-threshold SRAMs" IEEE 2018 International Solid-State Circuits Conference (ISSCC) Student Research Preview, San Francisco, California. [Poster] [Slides] [Research Gate Link]

Submitted Work Under Review:

Research Experience

CMOS Optical Receiver Circuits: University of Toronto

Sept 2016-Present, Advisor: Prof. Anthony Chan Carusone

• Designing Optical Receiver Front-end for +100 Gb/s PAM-4 fiber-optic communications in 16 nm FinFet CMOS

• Providing compact package level integration solution of CMOS optical receiver with state-of-the-art photodetectors

• High-frequency and Low-noise layout optimization in 16 nm FinFet CMOS

• Second order system optimization with Gain-BW-Noise trade-offs and peak-distortion analysis

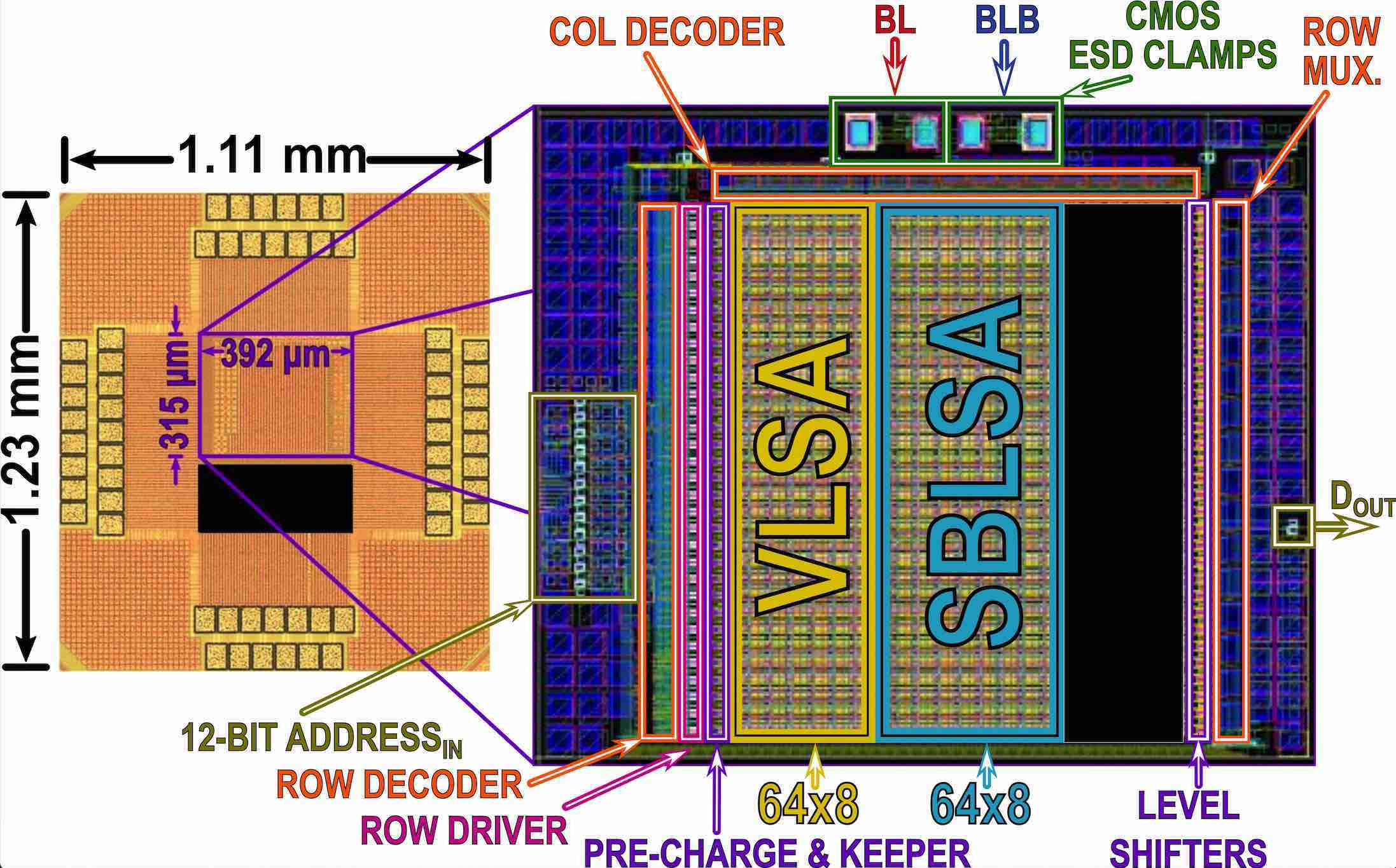

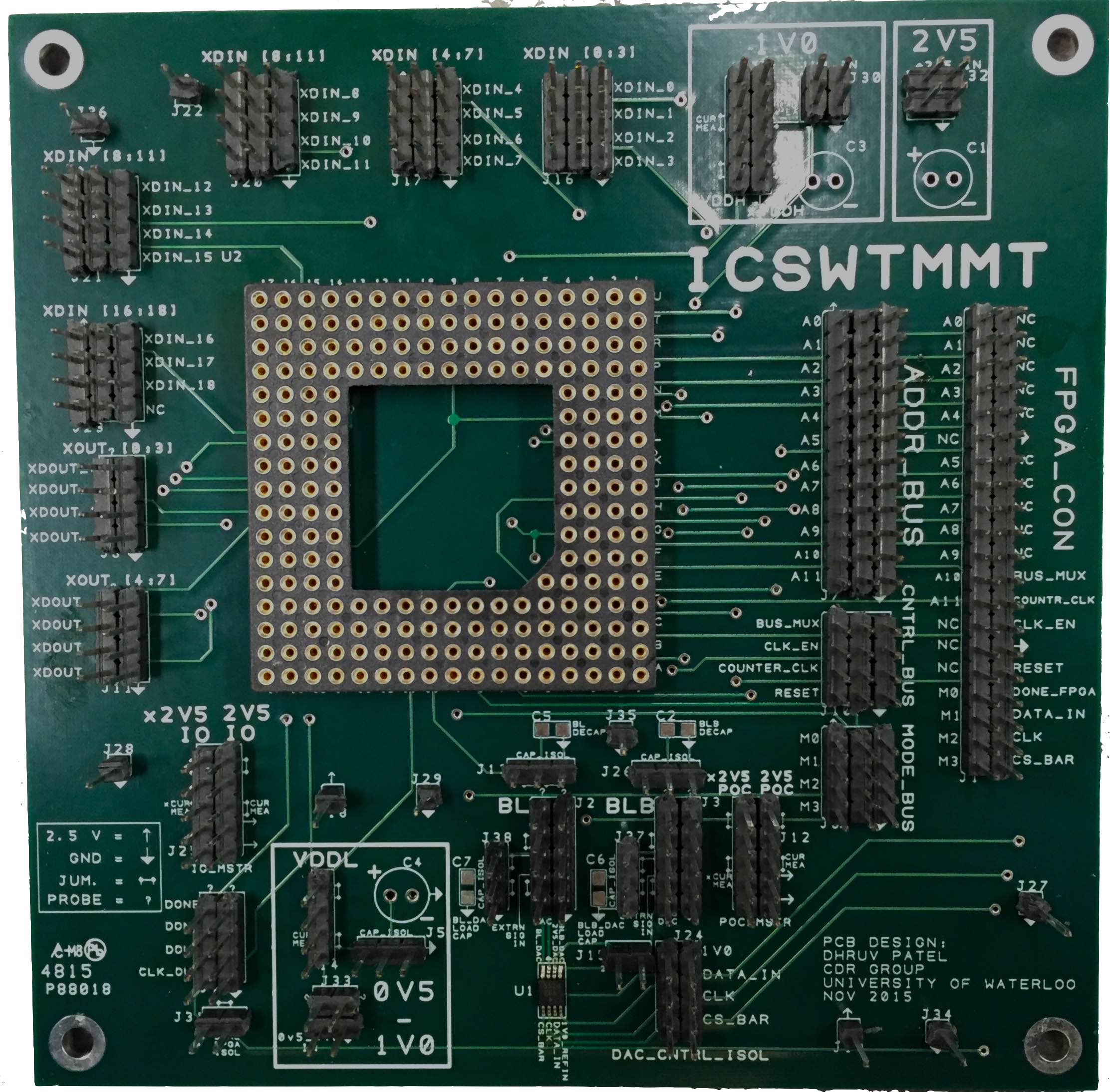

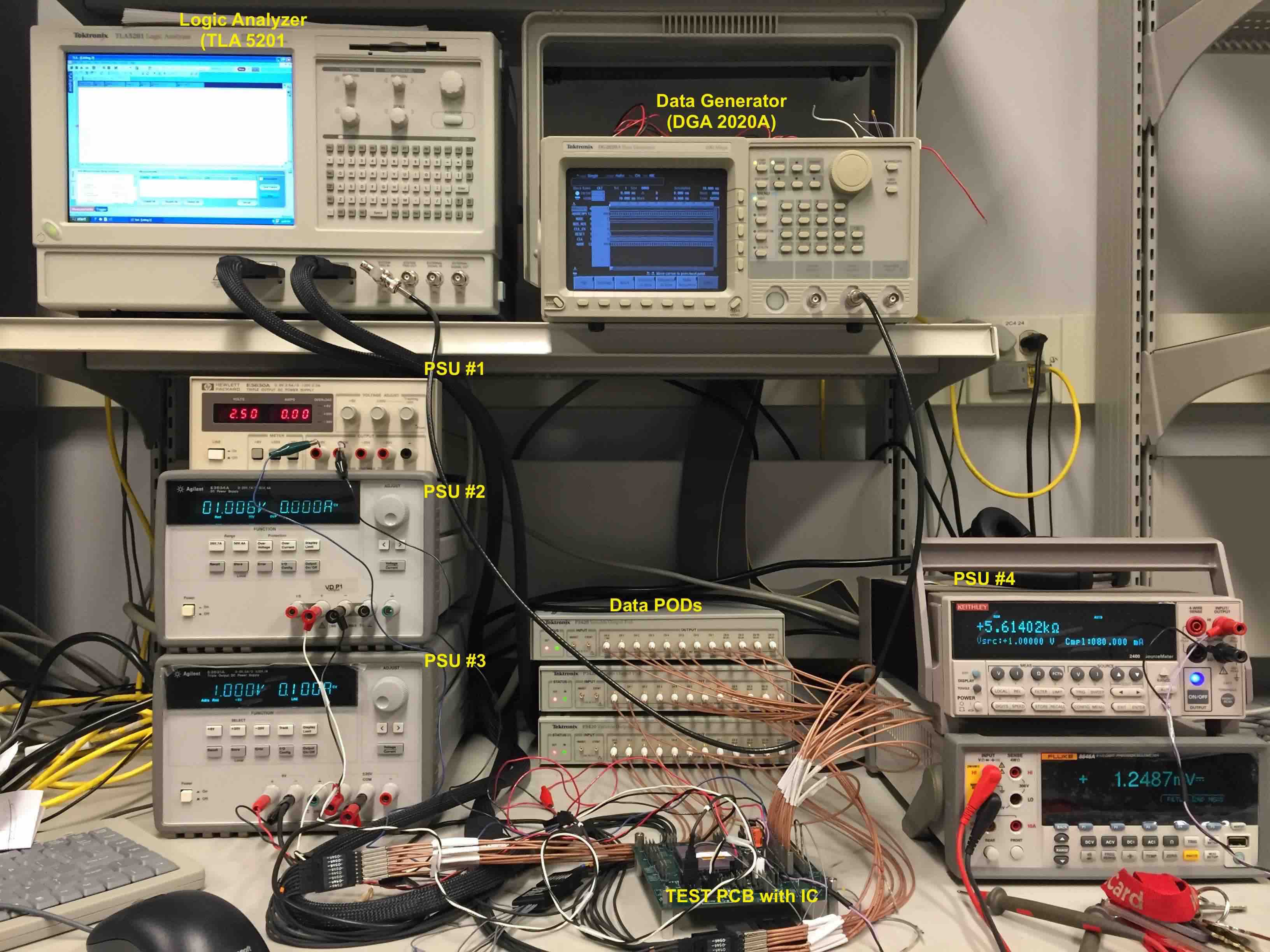

SRAM VLSI Circuits: University of Waterloo

Sept 2015-Aug 2017, Advisors: Prof. Manoj Sachdev, Prof. Adam Neale and Prof. Derek Wright

• Taped-out low-voltage and offset reducing Sense-amplifiers in 65 nm CMOS

• Researched variation tolerant, low-voltage, short-sensing delay sense amplifiers for SRAMs

• PCB Design for Sense Amplifier IC characterization

• Characterization of 65-nm Sense Amplifier ICs in VLSI laboratory

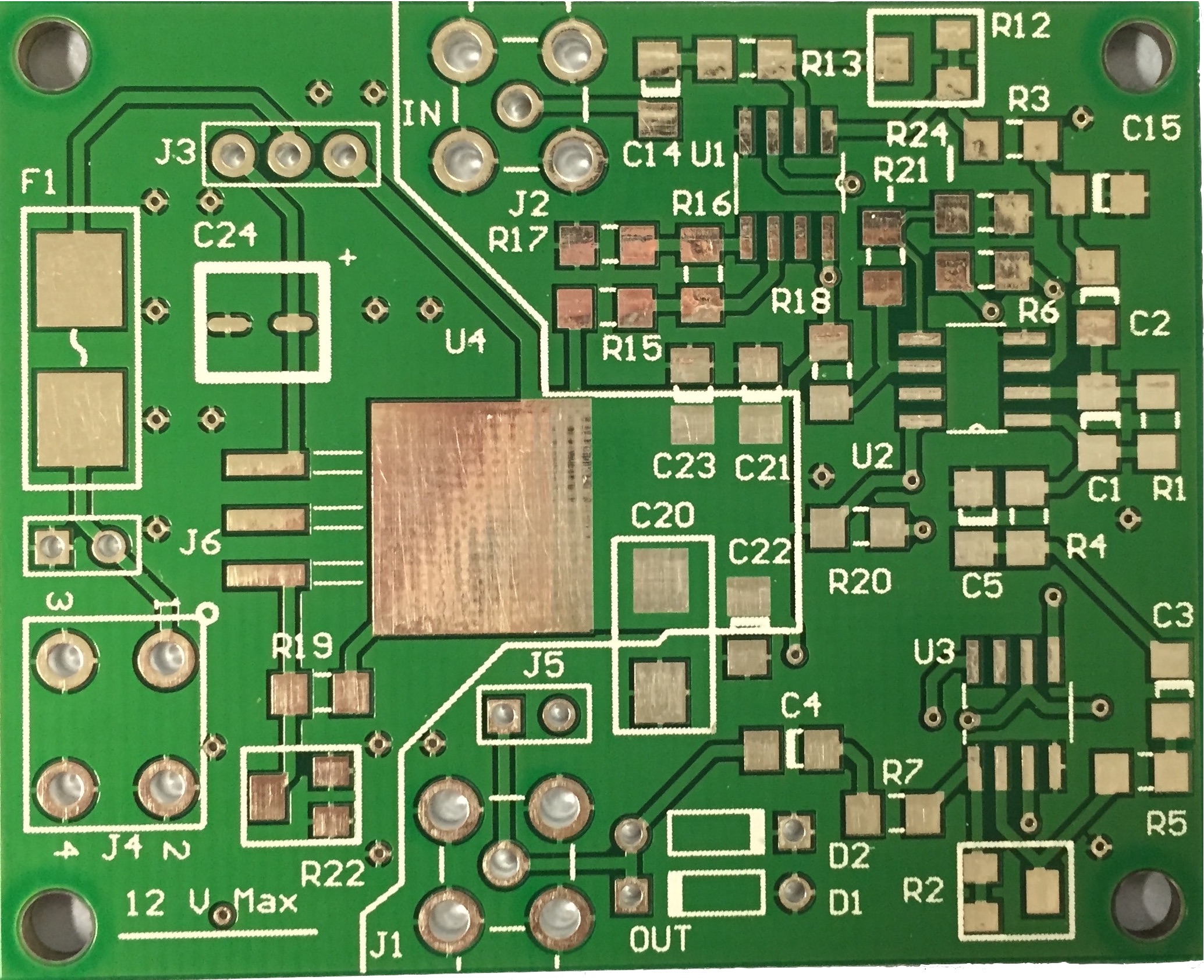

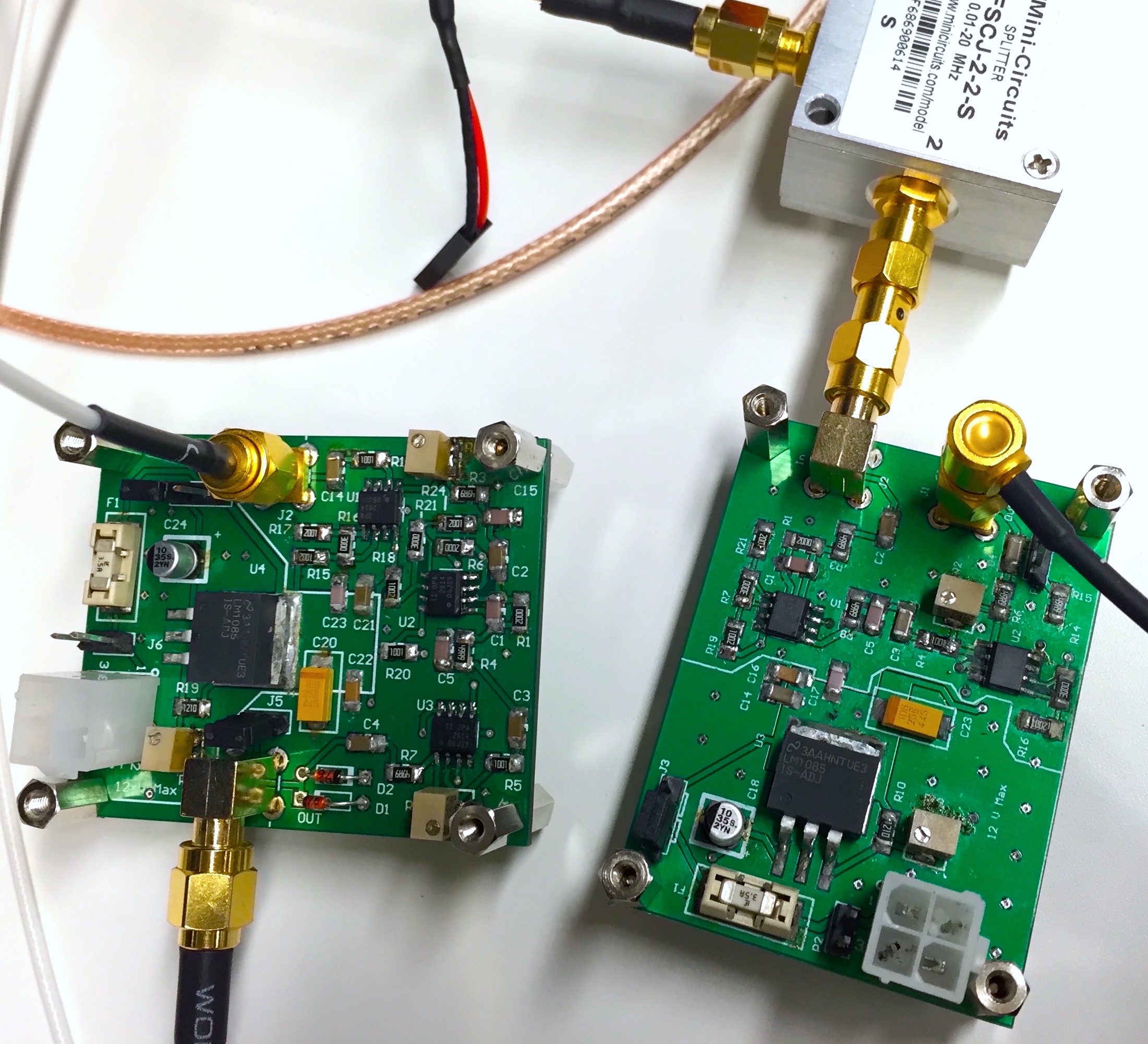

Powerline Transceiver Design: University of Waterloo

Jan 2015-Aug 2015, Advisor: Prof. Vincent Gaudet

• Assisted in In-Vehicular DC power-line communication (PLC) research

• Schematics and PCB designs of transmitter and receiver analog-front-end (AFE) boards

• Prototyped and characterized AFE transceivers in microelectronics laboratory

• Performed substantial circuit simulations and component selections for the AFE circuitry